70гЦЦЮ5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения экстремального числа | 1986 |

|

SU1388845A1 |

| Устройство для вычисления порядковых статистик последовательностей из @ - @ -разрядных чисел | 1987 |

|

SU1434424A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Устройство для поиска экстремальных чисел | 1980 |

|

SU883895A1 |

| Устройство для выделения экстремального из @ чисел | 1981 |

|

SU1005030A1 |

| Устройство определения локальных экстремумов функции | 1984 |

|

SU1241227A1 |

| Устройство для сравнения чисел | 1981 |

|

SU960799A1 |

| Устройство для определения разностидВуХ п-РАзРядНыХ чиСЕл | 1979 |

|

SU824208A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для сравнительного анализа п чисел | 1978 |

|

SU736090A1 |

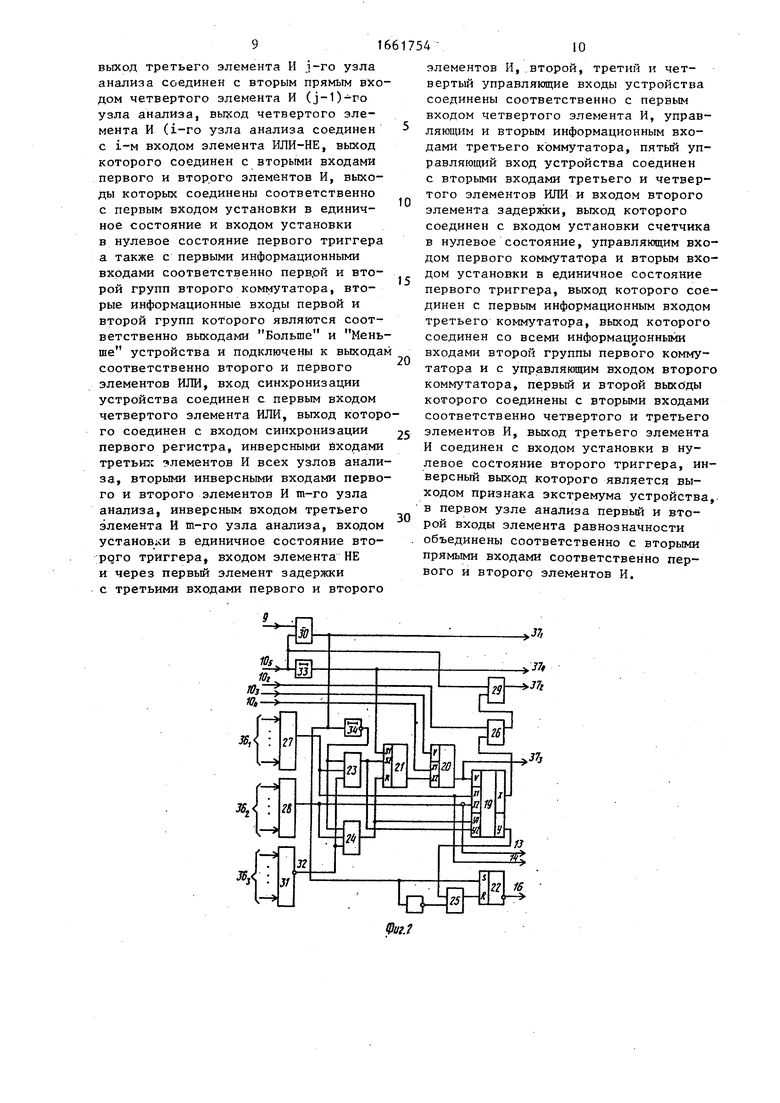

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет обеспечения сравнения чисел с порогом и выделения локальных экстремумов в последовательности чисел. Устройство содержит коммутатор 1, регистры 2, 3, узлы анализа (УА) 41 - 4т, блок управления (БУ) 5, счетчик 6, выходной регистр 7, информационные входы 81 - 8т, вход 9 синхронизации, управляющие входы 101 - 105, выходы экстремума 11 и адреса экстремума 12, выходы "больше" 13, "меньше" 14, "равно" 15, выход признака экстремума 16. УА содержит элементы равнозначности, элементы И. БУ содержит коммутаторы, триггеры, элементы И, ИЛИ, ИЛИ - НЕ, НЕ, элементы задержки. Устройство работает в одном из четырех режимов: сравнение чисел с порогом, выделение максимального числа, выделение минимального числа, выделение локальных экстремумов в последовательности чисел. 5 ил.

Cft О

s|

СП

Јь

Изобретение относится к автоматике и вычислительной технике.

Цель изобретения - расширение функциональных возможностей за счет обеспечения сравнения чисел с порогом и выделения локальных экстремумов в последовательности чисел.

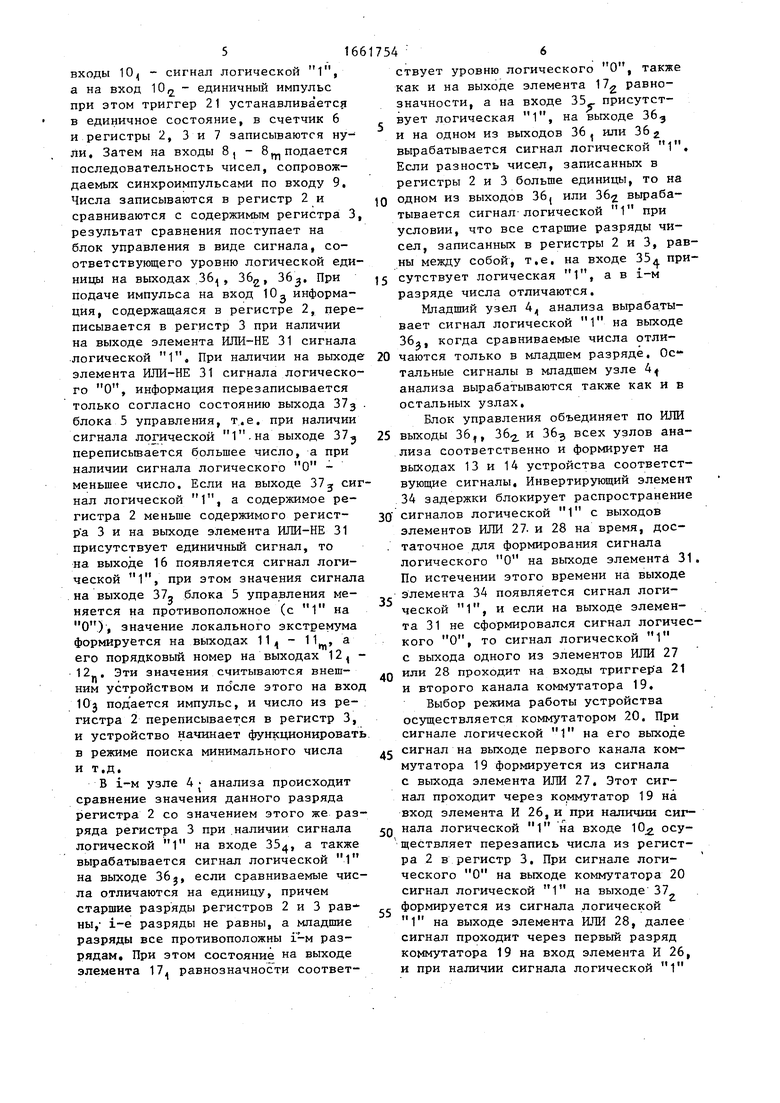

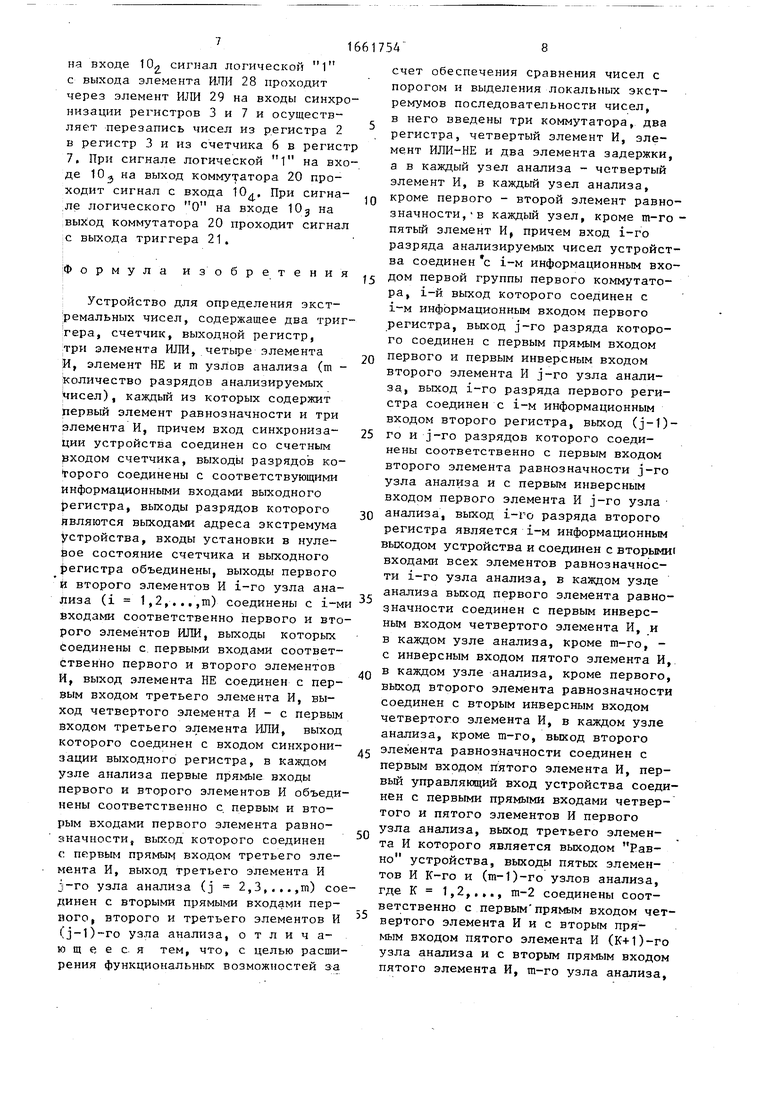

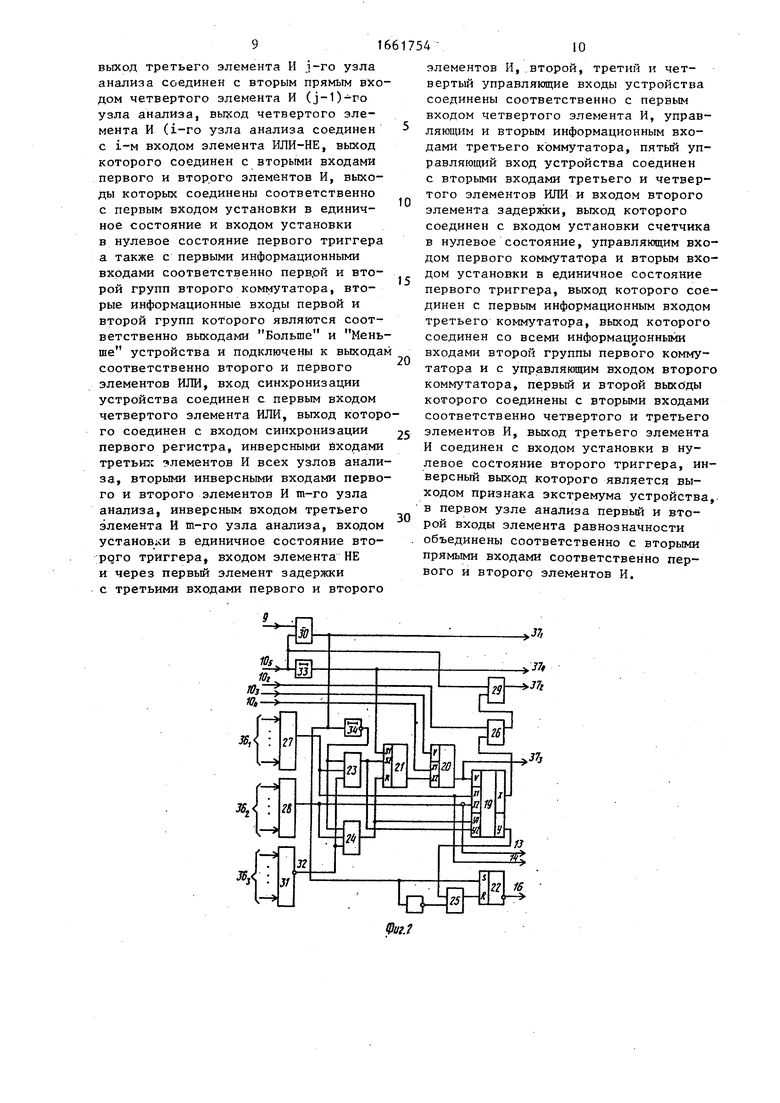

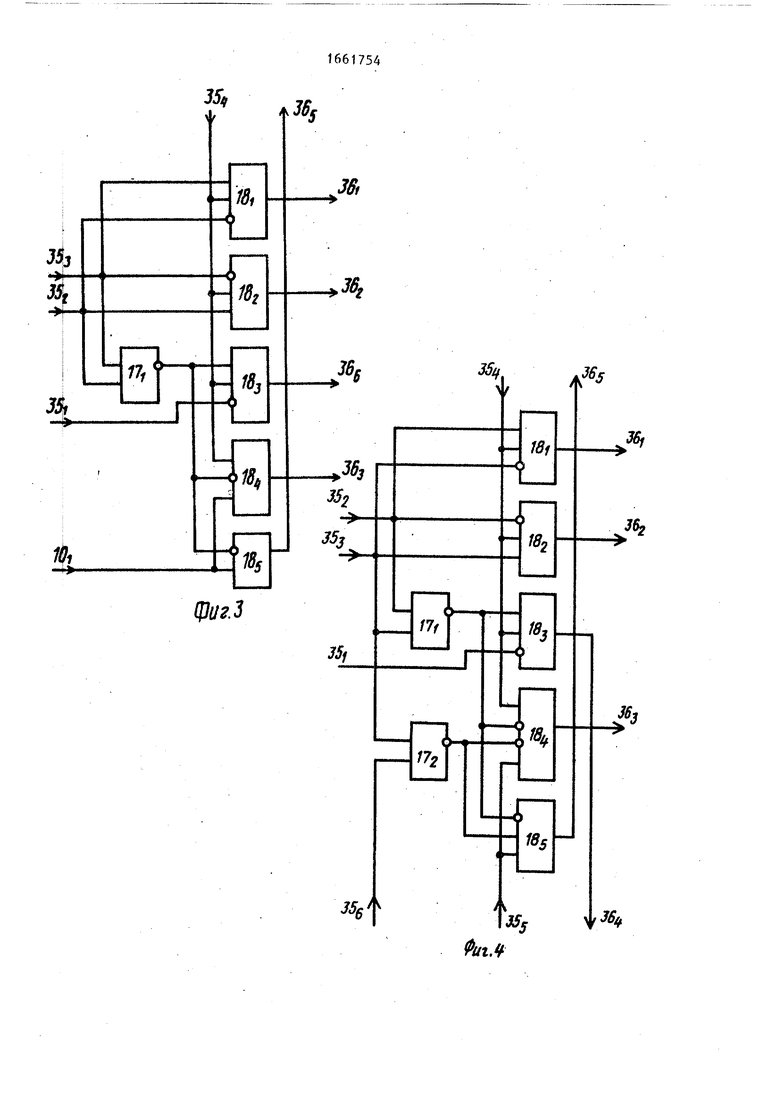

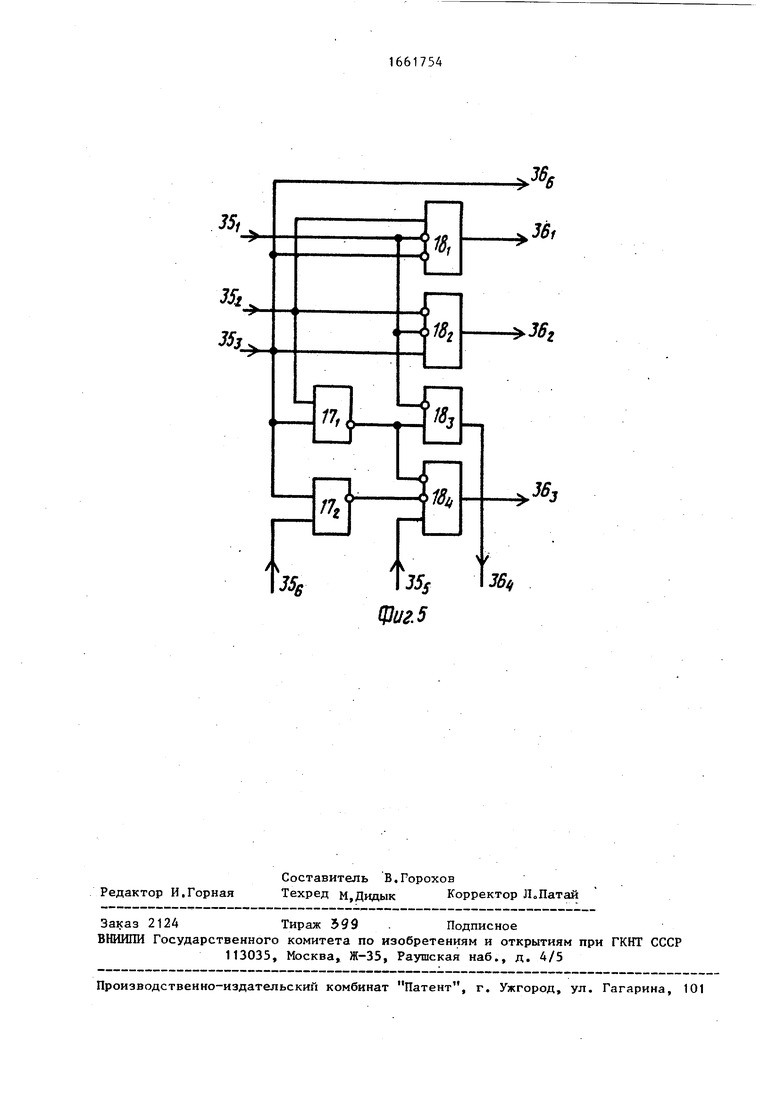

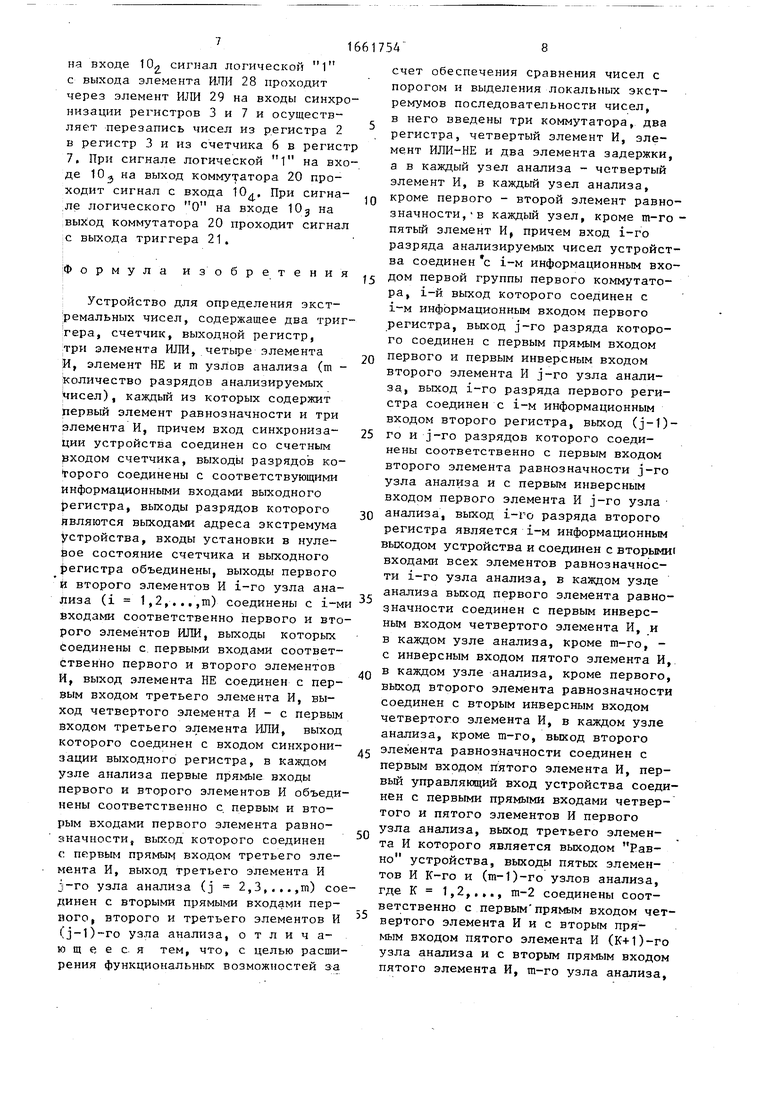

На фиг, 1 приведена схема предлагаемого устройстваJ на фиг, 2 - схема блока управления, на фиг. 3-5 - схемы соответственно первого (младшего), 1-го (2 1 Ј го, m - количество раз-- рядов анализируемых чисел) и m-го узлов анализа,

Устройство содержит коммутатор 1, регистры 2 и 3, узлы 4 - 4№ анализа, блок 5 управления, счетчик 6, выходной регистр 7, информационные входы 8 - 8 , вход 9 синхронизации, управляющие входы 10 - , выходы экстремума 11 и адреса экстремума 12, выходы Больше 13, Меньше 14, Равно 15, выход 16 признака экстремума.

Узлы 4 анализа содержат элементы

17«

И

и 17 равнозначности, элементы

18, 18. Блок 5 управления содержит коммутаторы 19 и 20, триггеры 21 и 22, элементы И 23-26, ИЛИ 27-30, ИЛИ-НЕ 31, НЕ 32, элементы 33 и 34 задержки (элемент 34 - инвертирующий) Обозначены также входы 35 - 35g и

36

выходы Jtt 1 - J&g, узлов 4 анализа и выходы 37 - 37 блока 5 управления.

Устройство работает в одном из четырех режимов: сравнение чисел с порогом, выделение минимального числа, выделение максимального числа, выделение локальных экстремумов,

В режиме сравнения с порогом устройство работает следующим образом,

На входы 10j, 104. и Ю5 подается потенциал логической 1. Затем на вход 10л подают положительный импульс, при этом счетчик 6 и регистры 2, 3 и 7 обнуляются. После этого на входы 8, - 8 подается значение порога, а на вход 9 - синхроимпульс, при этом значение порога записывается в регистр 2 и сравнивается со значением числа, записанного в регистре 3, Узел 4m анализа старшего разряда сравнивает старший разряд и вырабатывает сигнал логической 1 на

выходе 36,, если старший разряд значения порога равен 1. Если старший разряд кода порога равен О, то на выходе 36ц вырабатывается сигнал

0

5

0

5

0

35

40

50

55

логической 1 и поступает к младшим разрядам. После окончания процесса сравнения на выходе 37а блока 5 управления формируется сигнал логической 1, который, записывает значение порога в регистр 3. Затем на вход 10 подается сигнал логического О. Устройство установлено в начальное состояние. Затем во входной регистр 2 последовательно записываются числа, подлежащие сравнению. Результат сравнения появляется в виде сигнала логической соответствующем выходе (13, 14 или 15).

В режиме выделения минимального числа устройство работает следующим образом.

На входы Ю5 и 10 подается сигнал логической 1, а на вход 10 - сигнал логического О и на вход Ю2 импульс, при этом счетчик 6 и регистр 7 обнуляются, а в регистры 2 и 3 записываются единицы - устройство установлено в начальное состояние. Затем на входы 8 - 8 подают последовательно числа в параллельном коде, подача числа сопровождается синхроимпульсом, подаваемым на вход 9. Поданное число при этом записывается в регистр 2, а к содержимому

счетчика 6 добавляется единица. Число, записанное в регистр 2, сравнивается с содержимым регистра 3, а результат сравнения появляется на выходах 36,, 36„, 36А узлов 4

, -jo, jo УЗЛОВ анализа. Если содержимое регистра 2 меньше содержимого регистра 3, то на выходе блока 5 управления появляется сигнал логической 1 и содержимое регистра 2 записывается в регистр 3, а содержимое счетчика 6 - в регистр 7, Таким образом, на выходах П 4- 11 присутствует значение наименьшего 45 поданного на текущий момент числа, а на выходах 12 - 12 значение его порядкового номера.

В режиме выделения максимального числа устройство работает аналогично, однако на вход 10 . поступает сигнал логического нуля, при этом регистры 2 и 3 обнуляются,

В режиме поиска локальных экстремумов устройство работает следующим образом.

За условие экстремума взято изменение знака приращения, когда оно больше единицы. На входы 10 и 10$. подаются сигналы логического О, на

входы 10,, - сигнал логической 1, а на вход 10 - единичный импульс при этом триггер 21 устанавливается в единичное состояние, в счетчик 6 и регистры 2, 3 и 7 записываются нули. Затем на входы 8, - 8, подается последовательность чисел, сопровождаемых синхроимпульсами по входу 9, Числа записываются в регистр 2 и сравниваются с содержимым регистра 3, результат сравнения поступает на блок управления в виде сигнала, соответствующего уровню логической единицы на выходах 36, 362, 36 а. При подаче импульса на вход Ю3 информация, содержащаяся в регистре 2, переписывается в регистр 3 при наличии на выходе элемента ИЛИ-НЕ 31 сигнала логической 1, При наличии на выходе элемента ИЛИ-НЕ 31 сигнала логического О, информация перезаписывается только согласно состоянию выхода 373 блока 5 управления, т.е. при наличии сигнала логической 1 на выходе 37 переписывается большее число, а при наличии сигнала логического О - меньшее число. Если на выходе 373 сигнал логической 1, а содержимое регистра 2 меньше содержимого регист- р а 3 и на выходе элемента ИЛИ-НЕ 31 присутствует единичный сигнал, то на выходе 16 появляется сигнал логической 1, при этом значения сигнала на выходе 37- блока 5 управления меняется на противоположное (с 1 на О), значение локального экстремума

формируется на выходах

« 11

т

его порядковый номер на выходах 12{ - 12 . Эти значения считываются внешним устройством и после этого на вход 10з подается импульс, и число из регистра 2 переписывается в регистр 3, и устройство начинает функционировать в режиме поиска минимального числа и т.д.

В i-м узле 4 анализа происходит сравнение значения данного разряда регистра 2 со значением этого же разряда регистра 3 при наличии сигнала логической 1 на входе 35, а также вырабатывается сигнал логической 1 на выходе 36j, если сравниваемые числа отличаются на единицу, причем старшие разряды регистров 2 и 3 равны,- 1-е разряды не равны, а младшие разряды все противоположны i-м разрядам. При этом состояние на выходе элемента 17, равнозначности соответ0

ствует уровню логического О, также как и на выходе элемента 17„ значности, а на входе 35 вует логическая 1, на выходе 36д и на одном из выходов 36 или 362 вырабатывается сигнал логической 1. Если разность чисел, записанных в регистры 2 и 3 больше единицы, то на одном из выходов 36, или 36 выраба0

5

0

5

0

5

/2 равно- присутсттывается сигнал логической 1 при условии, что все старшие разряды чисел, записанных в регистры 2 и 3, равны между собой, т.е. на входе 35 при- 5 сутствует логическая 1, а в i-м разряде числа отличаются.

Младший узел 4 анализа вырабатывает сигнал логической 1 на выходе 36, когда сравниваемые числа отличаются только в младшем разряде. Остальные сигналы в младшем узле 4 анализа вырабатываются также как и в остальных узлах.

Блок управления объединяет по ИЛИ выходы 36f, 36.2. и 36-э всех узлов анализа соответственно и формирует на выходах 13 и 14 устройства соответствующие сигналы. Инвертирующий элемент 34 задержки блокирует распространение сигналов логической 1 с выходов элементов ИЛИ 27. и 28 на время, достаточное для формирования сигнала логического О на выходе элемента 31. По истечении этого времени на выходе элемента 34 появляется сигнал логической 1, и если на выходе элемента 31 не сформировался сигнал логического О, то сигнал логической 1 с выхода одного из элементов ИЛИ 27 или 28 проходит на входы триггер а 21 и второго канала коммутатора 19,

Выбор режима работы устройства осуществляется коммутатором 20. При сигнале логической 1 на его выходе сигнал на выходе первого канала коммутатора 19 формируется из сигнала с выхода элемента ИЛИ 27. Этот сигнал проходит через коммутатор 19 на вход элемента И 26, и при наличии сигнала логической 1 на входе 10 осуществляет перезапись числа из регистра 2 в регистр 3, При сигнале логического О на выходе коммутатора 20 сигнал логической 1 на выходе 37 формируется из сигнала логической 1 на выходе элемента ИЛИ 28, далее сигнал проходит через первый разряд коммутатора 19 на вход элемента И 26, и при наличии сигнала логической 1

0

5

на входе 10 сигнал логической 1 с выхода элемента ИЛИ 28 проходит через элемент ИЛИ 29 на входы синхронизации регистров 3 и 7 и осуществляет перезапись чисел из регистра 2 в регистр 3 и из счетчика 6 в регист 7, При сигнале логической 1 на входе 10 Ј на выход коммутатора 20 проходит сигнал с входа 10. При сигнале логического О на входе 10j на выход коммутатора 20 проходит сигнал с выхода триггера 21,

Формула изобретения

Устройство для определения экстремальных чисел, содержащее два триггера, счетчик, выходной регистр, три элемента ИЛИ, четыре элемента И, элемент НЕ и m узлов анализа (т - количество разрядов анализируемых чисел), каждый из которых содержит первый элемент равнозначности и три элемента И, причем вход синхронизации устройства соединен со счетным рходом счетчика, выходы разрядов которого соединены с соответствующими информационными входами выходного регистра, выходы разрядов которого Являются выходами адреса экстремума устройства, входы установки в нулевое состояние счетчика и выходного регистра объединены, выходы первого И второго элементов И 1-го узла анализа (i 1,2,...,m) соединены с i-м входами соответственно первого и второго элементов ИЛИ, выходы которых соединены с первыми входами соответственно первого и второго элементов И, выход элемента НЕ соединен с первым входом третьего элемента И, выход четвертого элемента И - с первым входом третьего элемента ИЛИ, выход

которого соединен с входом синхрони- элемента равнозначности соединен с

зации выходного регистра, в каждом узле анализа первые прямые входы первого и второго элементов И объединены соответственно с первым и вторым входами первого элемента равнозначности, выход которого соединен с первым прямым входом третьего элемента И, выход третьего элемента И j-ro узла анализа (j 2,3,...,m) соединен с вторыми прямыми входами первого, второго и третьего элементов И (j-l)-ro узла анализа, отличающееся тем, что, с целью расширения функциональных возможностей за

50

первым входом пятого элемента И, пе вый управляющий вход устройства сое нен с первыми прямыми входами четве того и пятого элементов И первого узла анализа, выход третьего элемен та И которого является выходом Рав но устройства, выходы пятых элемен тов И К-го и (m-l)-ro узлов анализа где К 1,2,.,., т-2 соединены соот ветственно с первым прямым входом ч вертого элемента И и с вторым прямым входом пятого элемента И (К+1)узла анализа и с вторым прямым вход пятого элемента И, га-го узла анализ

счет обеспечения сравнения чисел с порогом и выделения локальных экстремумов последовательности чисел, в него введены три коммутатора, два регистра, четвертый элемент И, элемент ИЛИ-НЕ и два элемента задержки, а в каждый узел анализа - четвертый элемент И, в каждый узел анализа,

0 кроме первого - второй элемент равнозначности, в каждый узел, кроме т-го - пятый элемент Et причем вход 1-го разряда анализируемых чисел устройства соединен с i-м информационным вхо5 дом первой группы первого коммутатора, i-й выход которого соединен с i-м информационным входом первого регистра, выход j-ro разряда которого соединен с первым прямым входом

0 первого и первым инверсным входом второго элемента И j-ro узла анализа, выход 1-го разряда первого регистра соединен с i-м информационным входом второго регистра, выход (j-1)5 го и j-ro разрядов которого соединены соответственно с первым входом второго элемента равнозначности j-ro узла анализа и с первым инверсным входом первого элемента И j-ro узла

0 анализа, выход 1-го разряда второго регистра является i-м информационным выходом устройства и соединен с вторыми входами всех элементов равнозначности i-ro узла анализа, в каждом узле анализа выход первого элемента равнозначности соединен с первым инверсным входом четвертого элемента И, и в каждом узле анализа, кроме т-го, - с инверсным входом пятого элемента И,

Q в каждом узле анализа, кроме первого, выход второго элемента равнозначности соединен с вторым инверсным входом четвертого элемента И, в каждом узле анализа, кроме т-го, выход второго

5

0

первым входом пятого элемента И, первый управляющий вход устройства соединен с первыми прямыми входами четвертого и пятого элементов И первого узла анализа, выход третьего элемента И которого является выходом Равно устройства, выходы пятых элементов И К-го и (m-l)-ro узлов анализа, где К 1,2,.,., т-2 соединены соответственно с первым прямым входом четвертого элемента И и с вторым прямым входом пятого элемента И (К+1)го узла анализа и с вторым прямым входом пятого элемента И, га-го узла анализа,

916

выход третьего элемента И i-ro узла анализа соединен с вторым прямым входом четвертого элемента И (j-1)-ro узла анализа, выход четвертого элемента И (1-го узла анализа соединен с i-м входом элемента ИЛИ-НЕ, выход которого соединен с вторыми входами первого и второго элементов И, выходы которых соединены соответственно с первым входом установки в единичное состояние и входом установки в нулевое состояние первого триггера а также с первыми информационными входами соответственно перв.он и второй групп второго коммутатора, вторые информационные входы первой и второй групп которого являются соответственно выходами Больше и Мень

ше устройства и подключены к выходам входами второй группы первого коммусоответственно второго и первого элементов ИЛИ, вход синхронизации устройства соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с входом синхронизации 25 первого регистра, инверсными входами третьих элементов И всех узлов анализа, вторыми инверсными входами первого и второго элементов И го-го узла анализа, инверсным входом третьего элемента И m-го узла анализа, входом установки в единичное состояние вто- pq.ro триггера, входом элемента НЕ и через первый элемент задержки с третьими входами первого и второго

30

татора и с управляющим входом второго коммутатора, первый и второй выходы которого соединены с вторыми входами соответственно четвертого и третьего элементов И, выход третьего элемента И соединен с входом установки в нулевое состояние второго триггера, инверсный выход которого является выходом признака экстремума устройства в первом узле анализа первый и второй входы элемента равнозначности объединены соответственно с вторыми прямыми входами соответственно первого и второго элементов И.

0

10

элементов И, второй, третий и четвертый управляющие входы устройства соединены соответственно с первым входом четвертого элемента И, управляющим и вторым информационным входами третьего коммутатора, пятый управляющий вход устройства соединен с вторыми входами третьего и четвертого элементов ИЛИ и входом второго элемента задержки, выход которого соединен с входом установки счетчика в нулевое состояние, управляющим входом первого коммутатора и вторым входом установки в единичное состояние первого триггера, выход которого соединен с первым информационным входом третьего коммутатора, выход которого соединен со всеми информационными

5

0

татора и с управляющим входом второго коммутатора, первый и второй выходы которого соединены с вторыми входами соответственно четвертого и третьего элементов И, выход третьего элемента И соединен с входом установки в нулевое состояние второго триггера, инверсный выход которого является выходом признака экстремума устройства, в первом узле анализа первый и второй входы элемента равнозначности объединены соответственно с вторыми прямыми входами соответственно первого и второго элементов И.

ФигЛ

| Устройство для сравнения чисел | 1979 |

|

SU873236A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения экстремального числа | 1986 |

|

SU1388845A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1989-04-04—Подача