тов, старт-вход которого является входом Ввод устройства, первые входы пятого и шестого элементов -И соединены с первыми входами первого второго элементов РАВНОЗНАЧНОСТЬ, вторые входы которых соединены между собой, первый вход седьмого элемента И соединен с вторым входом шестого элемента И, третий вход которого соеинен с первым входом восьмого элемента И и с выходом второго элемента И, выход первого элемента И соединен с первым входом девятого элемента И, вторые входы пятого и седьмого элементов И соединены с вькодом третьего элемГента И,, вторые . входы восьмого и девятого элементов И подключены к выходам второго п пер- вого элементов РАВНОЗНАЧНОСТЬ сбответственно, выход восьмого элемента И соединен со счетным входом первого двоичного счетчика, первьй вход установки О которого соединен с вькодом второго элемента задержки, вход которого подключен к выходу первого элемента ИЛИ и к первому входу десятого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, входы которого подключены к выходам первого двоичного счетчика, второй вход установки О которого соединен с вторыми входами установки О счетных триггеров, с вторым стопвходом ждущего генератора тактов, с входами установки пуля peiHCTpa сдвита, регистра памяти,D -триггера, с входами установки 1 первого и второго | 5-триггеров и является входом сброса устройства, а выходы пятого, седьмого, девятого, шестого и десятого элементов И соединены с соответствующими входами регистра памяти, вы- , ходы которого являются выходами информации о наборе свойств полноты устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения возможности контроля входной информации, в устройство введены третий RS-триггер, третий элемент задержки, третий элемент ИЛИ, второй и третий двоичные счетчики, одиннадцатьй и двенадцатый элементы И, три коммутатора каналов и два оперативных запоминающих блока, причем выход третьего RS-триггера. подключен к управляющим входам ком мутаторов каналов,, к входам Записьсчитывание оперативных запоминающих блоков первому входу одиннадцатого элемента И,, второй вход которого является информационным входом устройства, а выход соединен с информационными входами оперативных запог-шнаюпщх блоков и первым входом двенадцатого элемента И, второй вход которого подключен к выходу первого коммутатора каналов, входам разрешения работы оперативных запошшающих блоков и к входу третьего элемента задерлски, выход которого соединен со счетным входом второго двоичного счетчигса, выходы которого подключены к первым группам информационных входов второго и третьего коммутаторов каналов, вторая группа информа.ционных входов второго коммутатора каналов подключена к соответствуюП1им выходам счетиьпс триггеров, а выходы соединены с адресны.ми входами первого onepaiT-iBHoro запоминающего блока, выход которого соединен с первыми входами первого и второго элементов РАВН031-1АЧНОСТЬ, вторые входы которых подключены к выходу второго оперативного запоминающего блока, инверсяьм выход которого соединен с первым входом седьмого элемента И, а адресные входы подключены к выходам третьего KOMNtyTaTopa каналов, вторая группа информационных входов которого подключена к соответствую1Щ-1м вторьм выходам разрядов коммутатора триггерных сигналов, первый информационный вход первого коммутатора каналов является входом синхронизации устройства, вход запуска устройства подключен к входу установки 1 третьего RSтрпггера, вход установки нуля которого подключен к выходу третьего элемента Ш1И, первый вход которого соединен со входом Ввод устройства, вход сброса устройства соединен с входами установки нуля второго и третьего двоичных счетчиков и с вторым входом третьего элемента ИЛИ, счетньй вход третьего двоичного счетчика подключен к выходу двенадцатого элемента И, а выходы,являются выходами информации в ранге устройства, второй информационный вход первого 7соммутатора каналов соединен с выходом ждущего генератора тактов Изобретение относится к автоматике и вычислительной технике и может, быть использовано для распознавания функциональной полноты систем логических функций при проектировании цифровых устройств, а также для контроля и поиска неисправностей в устройствах путем анализа логических свойств булевых функций, описывающих временные диаграммы их функционирования . Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности контроля входной информацией. При этом, кроме определения свойств функциональной полноты, устройство может производить анализ двоичных последовательностей, поступающих с выходов цифровых блоков при их функционировании, достаточный для эффективного контроля и поиска неисправностей в них. На чертеже представлена схема устройства. Устройство содержит RS-триггер 1, оперативные запоминакщие блоки 2 и 3, триггеры 4 со счетным входом, коммутатор 5 триггерных сигналов, формирователи 6 и 7 импульсов, D триггер 8, регистр 9 сдвига, элементы И 10 и 11, элементРАВНОЗНАЧНОСТЬ 12, элемент И 13, элемент РАВНОЗНАЧНОСТЬ 14, элемент И 15, регистр 16 памяти, двоичный счетчик 17, ждущий генератор 18 тактов, элемент задержки 19, RS-триггеры 20 и 21, шину 22 логической единицы, Ввод, вход 24 сброса, вькоды 25-29 ииформаи;ии о наборе свойствполноты, выход 30 сигнала окончания работы, вход 31 запуска, элемент задержки 32 элемент ИЛИ 33, элементы И 34-39,элемент ИЛИ 40, элементы И 41 и 42, ком мутаторы 43, 44 и 45 каналов, элемент задержки 46, двоичные счетчики 47 и 48, информационньй вход 49, вход 50 синхронизации, выход 51 информации о ранге, элемент ИЛИ 52.

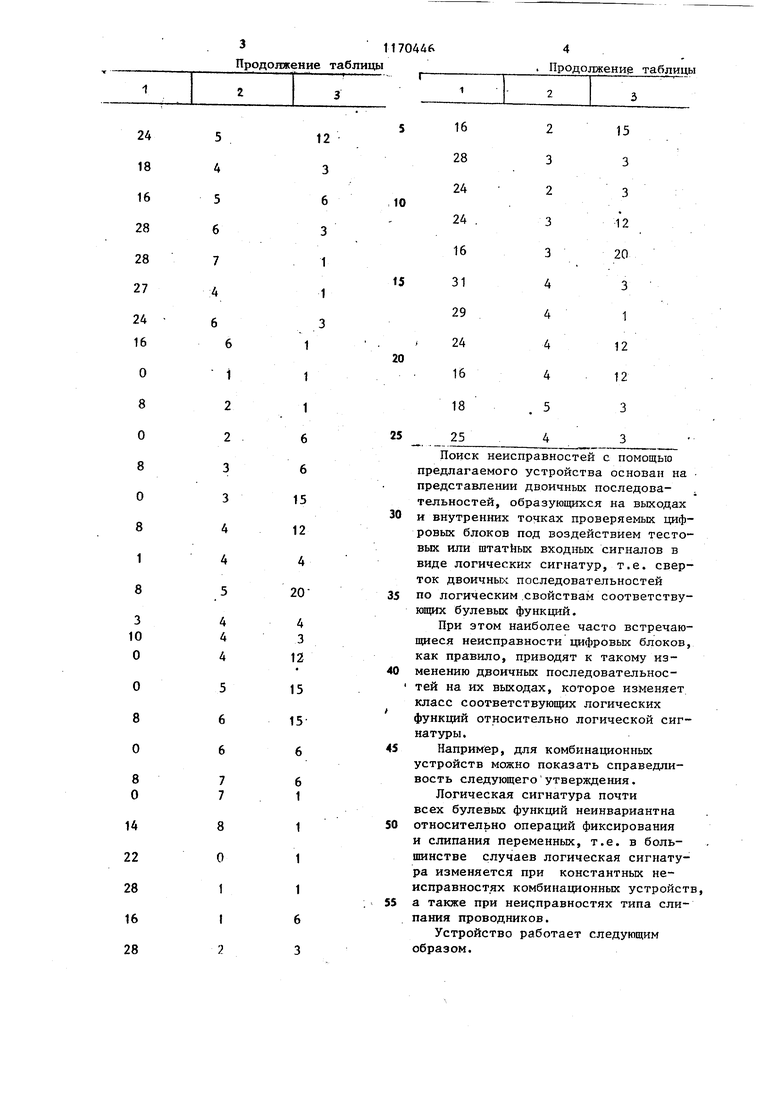

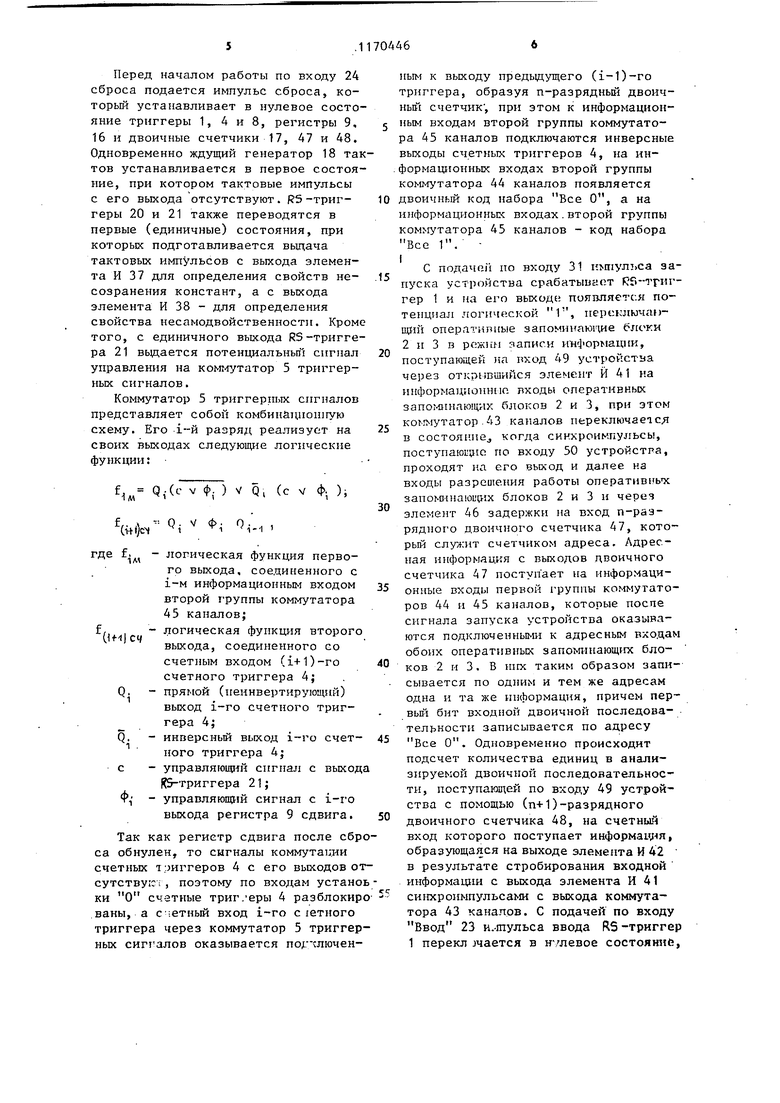

При таком построении устройство определяет не только набор свойств полноты, но и ранг, т.е. число единиц в таблиг,с истинности анализируемой логической функции, и, таким образом,5Ь определяет обобщенньй типовой логический признак, который назовем логической слгнатурой. Таким образом, логическая сигнатура булевой функщш представляет собой комбинацию ранга и наб.ора свойств полноты данной функции. Набором свойств полноты называется комбинация пяти свойств полноты логических функций: несохранения константы нуль, несохранеьгая.константы единица, немонотонности, нелинейности и несамодвойственности. Известно, что существует только пят aдцaть различных наборов свойств полноты логических функций, в соответствии с которыми все булевые функции делятся на 15 типов. Очевидно, что в соответствии с возможными рангами все булевые функции делятся на () тип.Можно показать также,что при п 72 существует ровно 5 2 типов логических сигнатур булевых функций. В качестве примера, в таблице приведены все возможные в алгебре логики типы логических сигнатур для булевых функций от двух и трех переменных.

5 4 5 6 7 4

12 3 6 3 1 1 3

6 6

1

1 2 2 3 3 4 4 5

1

1

6

6 15 12

4 204 3

4 4

4 5 6 6

12

15

15

6

7 7

6 1

1 1 1 6

8 О 1

I 2

3

10

15

20

Поиск неисправностей с помощью предлагаемого устройства основан на представлении двоичных последовательностей, образующихся на выходах и внутренних точках проверяемых цифровых блоков под воздействием тестовых или штатных входных сигналов в виде логических сигнатур, т.е. сверток двоичньс-с последовательностей по логическим .свойствам соответствующих булевых функций.

При этом наиболее часто встречающиеся неисправности цифровых блоков, как правило, приводят к такому изменению двоичных последовательностей на их выходах, которое изменяет класс соответствующих логических функций относительно логической сигнатуры.

Например, для комбинационных устройств можно показать справедливость следующегоутверждения.

Логическая сигнатура почти всех булевых функций неинвариантна относительно операций фиксирования и слипания переменных, т.е. в большинстве случаев логическая сигнатура изменяется при константньк неисправностях комбинационных устройств, а также при неисправностях типа слипания проводников.

Устройство работает следующим образом. Перед началом работы по входу 24 сброса подается импульс сброса, которьш устанавливает в нулевое состо яние триггеры 1, 4 и 8, регистры 9, 16 и двоичные счетчики 17, 47 и 48. Одновременно ждущий генератор 18 та тов устанавливается в первое состоя ние, при котором тактовые импульсы с его выхода отсутствуют. R5-триггеры 20 и 21 также переводятся в первые (единичные) состояния, при которых подготавливается вьщача тактовых импульсов с выхода элемента И 37 для определения свойств несозранения констант, а с выхода элемента И 38 - для определения свойства несамодвойственности. Кром того, с единичного выхода RS-тригге ра 21 вьщается потенциальньй сигнал управления на коммутатор 5 триггерных сигналов. Коммутатор 5 триггерпых сигналов представляет собой комбинациоп гую схему. Его i-й разряд реализует на своих выходах следующие логические функции: 1м V ф; ) V Q, (с V ф; ); Сн()с.- i / f. логическая функция первого выхода, соединенного с i-M информационным входом второй группы коммутатора 45 каналов; f, . - логическая функция второго выхода, соединенного со счетным входом (i+1)-ro счетного триггера 4; Q, - прямой (пеинвертирующий) выход i-ro счетного триггера 4; Q. - инверсньй выход счетнего триггера 4; с - управляющий сигнал с выход КЗ-триггера 21; Ф, - управляющий сигнал с i-ro выхода регистра 9 сдвига. Так как регистр сдвига после сбр са обнулен, то сигналы коммутации счетных триггеров 4 с его выходов о сутству::;, поэтому по входам устано ки О сч-зтиые триггеры 4 разблокир ваны, а с- етный вход i-ro с leTnoro триггера через коммутатор 5 триггер ных сипалов оказывается пo :-отIoчeнньм к выходу предыдущего (i-1)-ro риггера, образуя п-разрядный двоичный счетчик , при зтом к информационным входам второй группы коммутатоа 45 каналов подключаются инверсные выходы счетных триггеров 4, на инормационных входах второй группы оммутатора 44 каналов появляется воичньй код набора Все О, а на нформационных входах.второй группы оммутатора 45 каналов - код набора Все 1. С подачей по входу 31 им11ул1 са запуска устройства срабатывает К -триггер 1 и на его выходе появляется поте}щиал логической 1, переключающий оперативные запоминающие блоки 2 и 3 в режим записи информации, поступающей )ia вход 49 устройства через ОТКР1ШШИЙСЯ элемент И 41 на информациоинмо. входы оперативных запо1-о1нающих блоков 2 и 3, при этом коммутатор 43 каналов переключается в состоянизл когда синхроимпульсы, поступаю131е по входу 50 устройства, проходят на его выход и далее на входы разрешения работы оператнвньх запо а-1наюи(их блоков 2 и 3 и через элемент 46 задержки на вход п-разрядного двоичного счетчика 47, которьй служит счетчиком адреса. Адресная информация с выходов двоичного счетчика 47 поступает на информационные входы первой группы коммутаторов 44 и 45 каналов, которые после сигнала запуска устройства оказываются подключенными к адресным входам обоих оперативных запоминающггх блоков 2 и 3. В Н1ГХ таким образом записывается по одним и тем же адресам одна и та же информация, причем первьй бит входной двоичной последова- тельности записывается по адресу Все О. Одновременно происходит подсчет количества единиц в анализируемой двоичной Последовательности, поступающей по входу 49 устройства с помощью (п+1)-разрядного двоичного счетчика 48, на счетный вход которого поступает информа1 ля, образующаяся на выходе элемента И 42 в результате стробирования входной информации с выхода элемента И 41 синхроимпульсами с выхода коммутатора 43 каналов. С подачей по входу Ввод 23 и.-шульса ввода RS -триггер 1 перекл зчается в нулевое состояний,

при которрм закрьгоаются элементы И 41 и 42, а оба оперативных запоминающих блока переводятся в, режим считьшания записанной информации. При этом запускается ждуший генератор 18 тактов и первьш же импульс с его выхода через подготовленные элементы И 37, 38 поступает на входы элементов И 10, 11 и 35 соответственно. Кроме того, коммутаторы 44 и 45 каналов переключаются Так, что к их выходам подключаются информационные входы второй группы, т.е. адресные входы блока 2 подключаются к счетным триггерам 4, а адресные входы блока 3 - к соответствующим выходам коммутатора 5 триггерных сигналов. Вместе с тем, через коммутатор43 каналов на входы разре шения работ блоков 2 и 3 начинают поступать импульсы с выхода ждущего генератора 18 тактов.

Элемент И 10 является определителем свойства Несохранерия константы нуль. К моменту поступления первого тактового импульса на один из его входов с выхода элемента И 37 на другом его входе с выхода блока 2 оказывается подключенным значение булевой функции на нулевом наборе, поэтому, если анализируемая логическая функция не сохраняет константу нуль, то тактовьй л.-шульс пройдет на выход элемента И 10 и переведет первьй триггер регистра 16 памяти в единичное состояние, фиксируемое на выходе 25 устройства. Аналогично элемент И 11 является определителем свойства несохранения константы единица. Один из его входов подключен к инверсному выходу блока 3, поэтому к моменту поступления первого импульса с выхода элемента И37 на этом входе оказывается инверсное значение анализируемой функции, на наборе Все 1,

Если анализируемая логическая функ1щя не сохраняет константу единица, то тактовьй импульс пройдет на выход элемента И 11 и установит второй триггер регистра 16 в единичное состояние, фиксируемое на выходе 26 устройства.

Первьй после ввода тактовьй им-t пульс, пройдя элемент задержки 19, переводит Р5-триггер 20 во второе (нулевое) состояние, при котором

запрещается, прохождение тактовьк импульсов на выход элемента И 37, и поступает на счетньй вход первого триггера двоичного счетчика, образованного (как было уже описано) из отдельных счетных триггеров 4 с помощью коммутатора 5 триггерных сигналов.

Указанньш счетчик начинает считать поступающие с элемента задержки 19 тактовые импульсы, при этом к адресным входам блока 2 подключаются через коммутатор 44 каналов прямые выходы счетных триггеров 4, а к адресным входам блока 3 - инверсные выходы этих триггеров через коммутатор 45 каналов.

Таким образом на выходах элемента РЛВИОЗПА.ЧНОСТЬ 12, являющегося определителем свойства несамодвойственности, соединенных с прямыг-ш выходами -обоих оперативных запоминающих блоков, в одни и те же моменты времени оказываются значения анализируемой логической функции на противоположных на.борах.

В случае, если анализируемая функция является несамодвойственной, то хотя бы на одной паре противоположных .наборов значения функции окажутся одинаковьи-га. При этом тактовый импульс с выхода элемента И 38, опережащий моменты изменения состояний триггеров 4 на величину, определяемую элементом задержки 19, пройдет на выход элемента И 35 и установит третий триггер регистра 16 памяти в единичное состояние, фиксируемое на выходе 27 устройства.

После перебора 2 состояний на выходе п-го счетного триггера появится отрицательньй перепад напряжения, из которого формирователь 7 сформирует управляющий импульс.Последний переводит RS-триггер 21 во второе (нулевое) состояние, йри котором тактовые импульсы проходят на выход элемента И 39, соединенного с элементами И 13 и 36. Кроме того, имульс с выхода формирователя 7 записывает единицу в 1)-триггер 8 и в первьй разряд регистра 9 сдвига, при этом на выходе первого разряда регистра 9 сдвига появляется сигнал коммутации первого счетного триггера 4,по которому указаиньй триггер удерживается в нулевом состоянии. Задержанные тактовые импульсы через первый разряд коммутатора 5 триггерных сигналов проходят в обход первого счетного триггер на счетный вход второго триггера, а к nepBONry адресному входу блока 3 через коммутатор 45 каналов оказывается подключенным инверсный выход первого счетного триггера.

Укороченный таким образом на один первый разряд двоичный счетчик, образованный из счетных триггеров 4 и разрядов коммутатора 5 триггерных сигналов, продолжает считать тактовые импульсы с выхода элемента задержки 19, при этом блоки 2 и 3 поочередно подключат к первым входам элемента И 13 и элемента РАВНОЗНАЧНОСТЬ 14 значения анализируемой логической функции на всех парах склеивающихся по первой переменной наборов.

Элемент И 13 является определителеи свойства немонотонности. Его второй вход соединен с инверсным выходом блока 3, поэтоьгу в один и тот же момент времени на первых двух входах элемента И 13 оказьшаются значения анализируемой функции на двух склеиваюищхся наборах, причем значение функции на большем из них оказывается проинвертированным.

Таким образом, если логическая функция является немонотонной, то хотя бы на одной паре склеивающихся наборов значение функции на меньшем из них будет больше, чем на большем., при этом на первых двух входах элемента И 13 окажется потенциал логической 1 и тактовый импульс, посту пающий на его третий вход с вь1хода элемента И 39, пройдет на выход элемента И 13 и установит четвертый триггер регистра 16 памяти в единичное состояние, фиксируемое на выходе 28 устройства.

Одновременно с определением свойства немонотонности осуществляется определение свойства нелинейности. Определителем свойства нелинейности является элемент РАВНОЗНАЧНОСТЬ 14, входы которого подключены к прямым выходам бчокон 2 и 3, а выход сс динен с из входов элемента И 36 Поэтому V случае, е .ли логическая функция Билинейная, то хотя бы на одной паре склеивающихся по существенной п гременной наборов функции

ринимает одинаковые значения, а актовьп импульс, поступающий на ругой вход- элемента И 36 с вььчода лемента И 39, пройдет на выход элеента И 36 и поступит на счетньш ход счетчика 17.

В том случае, если ни на одной паре или на всех парах склеивающихся по первой переменной наборов функция принимает одинаковые значения, с выхода элемента И 36 па счетньш вход (п-1)-разрядного двоичного счетчика 17 не поступит ни одного или поступит ровно 2 -1 импульсов соответственно, в результате указанный счетчик будет обнулен, а на входе элемента 33 ИЛИ, подключенного своими входами к выходам всех разрядов счетчика 17, будет сформирован потенциал логического О. После перебора 2 -1 состояний на выходе п-го счет1гого триггера А вторично образуется отрицательны - перепад напряжения, который через форьшрователь 7 перебросит триггер первого разряда регистра 9 сдвига в нулевое состояние, обусловленное единичным состоянием р -триггера 8, а во второй разряд регистра запишется единица, обусловленная единичным состоянием триггера первого разряда регистра 9 сдвига. Таким образом, с выхода второго разряда ре.гистра 9 сдвига появляется сигнал ф коммутации второго счетного триггера 4, которьй действует аналогично сигналу р, т.е. удерживает в нулевом состояшга иторой счетный триггер 4, сигнал на счетньпЧ вход третьего триггера 4 поступает в обход второго триггера с выхода первого счетного триггера, п на второй адресный вход блока 3 подключается через ко шутатор 45 каналов инверсньп пыход второго счетного триггера 4.

Импульсы с выхода формирователя 7, пройдя элемент 1-ШИ 40, не пройдут далее на выход элемента И 34 и не установят пятый триггер регистра 16 памяти в единичное состояние.

В любом другом случае, когда число пар.склеивающихся наборов, на которых функ1шя принимает одинаковые значения, отличается от чисел О и 2 -1, на выходе элемента ШШ 33 будет c JOpi ipc зан потенциал логической 1, разрешающий прохождение импульса с выхода элемента 1-ШИ 40 на вход установки единицы пятого триггера регистра 16 памяти, который установится в единичное состояние,фиксируемое на выходе 29 устройства и свиде тельствующее о нелинейности анализируемой логической функции. Пройдя элемент задержки 32, имульсы с выхода элемента ИЛИ 40 произведут установку в начальное нулевое состояние счетчика 17, подготавливая его к работе по следующей переменной. Аналогично происходит работа устройства вплоть до коммутации п-го счетного триггера 4, при этом в регистре 9 сдвига через каждые тактов происходит сдвиг логической единицы в сторону старших разрядов и заполнение младших разрядов логическими нулями, После того, как образованный из счетных триггеров 4 двоичньй счетчик просчитает 2-1 состояний с момента коммутации п-го триггера, на выходе (п-1)-го счетного триггера образуется отрицательный перепад напряжения которьм после формирования с помощью формирователя 6 импульсов проходит через подготовленный элемент И 15 и элемент ИЛИ 40 на вход элемента И 34, а через элемент 32 задержки - на вход установки нуля счет чика. 17, а также на стоп-вход генера тора 18 тактов и останавливает его, при этом на выходе 30 появляется импульс окончания работы устройства сигнализируя о том, что полученные значения логической сигнатуры анализируемой логической функции могут быть считаны из регистра 16 памяти и двоичного счетчика 48. Таким образом, в предложенном устройстве определение ранга двоичной последовательности осуществляется в процессе ее ввода в два оперативных запоминающих блока, а определение набора свойств полноты осуществляется в процессе считывания информации из этих блоков путем . проверки условий полноты последовательно для определенным образом выбранных: пар наборов, причем определение свойств несозранения констант; совмещено по времени с первым тактом определения свойства несамодвойственности, для распознавания, которого осуществляется перебор всех пар противоположных наборов, а определение свойства немонотонности совмещено по времени с определением свойства нелинейности, для чего осуществляется перебор всех пар склеивающихся наборов. Поэтому через п x (п + 2) V 2 актов генератора 18 импульсов определение всех свойств полноты анализируемой логической функции будет закончено, результат определения набора свойств полноты зафиксированв регистре 16 памяти, а ранга - в двоичном счетчике 48 и вьщан сигнал окончания работы по выходу 30 устройства. Предложенное устройство позволяет вьшвить в двоичных последовательност ях 100% ошибок нечетной кра.тности, .а также многие ош1бки четной кратности. Если считать, что неисправности могут превратить любую двоичную последовательность Б любую другую из числа всех возможных заданной длины, то достоверность распознавания двоичной последовательности с помощью данного устройства в среднем составляет величину 5 1 Более точно достоверность распознавания оказывается разной для различных последовательностей. Так, минимальной достоверностью, близкой к величине , . 2 1 . 2 . обладают одновременно немонотонные, нелинейные и несамодвойственные функции, ранг которых равен 2 . В то же время имеются последовательности, достоверность распознавания которых близка к величине Z 2 -1 (например, константы нуля и единицы). Это позволяет реализовать метод терминального тестирования цифровых блоков, при котором из множества возможных контролирующих тестов выбирается тот, реакция проверяемого устройства на которьй обладает, ззданщами логическими свойствами (логической сигнатурой). Подбирая тест по логическим сигнатурам, можно значительно повысить достоверность контроля даже без изменения длины тестовой последовательности и глубины свертки выходных реакций. Так, например, реакцию любого комбинационного устройства на тривиальный тест, состояп{ий из всех возможных наборов длины п, можно сделать монотонной путем простой перестановки тестовых наборов, поскольку монотонные функщш могут обладать любым из возможных рангов от О до 2.

С помощью предложенного устройства можно проводить исследования влияния тех или иных неисправностей на характер выходных последовательноетей контролируемых изделий, что необходимо для формирования адекватных реальных математических моделей неисправностей, использующихся при синтезе самих тестов. При этом ранг показывает количество единиц, а набор свойств полноты - распределение этихединиц в двоичных последовательностях .

Преимуществом предложенного устройства является также то, что в логической сигнатуре многие комбинации логических свойств являются запрещенными. Например, из пяти свойств полноты возможны только 15 комбинаций. Можно показать также, что наборами свойств полноты № 14 и 22 обладают те и только те булевые функции,ранг которых равен соответственно 2 и О, а наборами свойств полноты К 1,

3, 10, 18, 25, 29 и 31 обладают только те булевые функции, ранг которых равен2 -1. Это служит дополнительным средством контроля за работой, устройства в процессе его функционирования.

При использовании предложенного устройства для целей контроля и поиска неисправностей предполагается, что длина анализируемой двойной последовательности равна 2.. В случае если эта длина не является степенью двойки, можно предусмотреть режим дозаполнсния оперативных запоминающих блоков, например, константашт нуля после каждого ввода информации в устройство, при этом очевидно, что емкость блоков должна быть рассчитана, исходя из максимальной длин анализируемой двоичной последовательности.

Для удобства работы оператора по поиску неисправностей в цифровых блоках методом анализа формируемых в них двоичных последовательностей и просмотром логических сигнатур обратным кодом от неправильных к правильным целесообразно выходы 2529 устройства подключить к блоку индикации набора .свойств полноты, а выходы 51 - к блоку индикации ранга анализируемой логической функции, при этом указанные блоки (не показаны) осуществляют преобразование двоичного кода составных частей логической сигнатуры в двоично-десятичньй код с последующей их индикацней в виде десятичных чисел.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распознавания на линейность булевых функций | 1990 |

|

SU1756879A1 |

| Устройство для сравнения кодов | 1982 |

|

SU1027715A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1661752A1 |

| Устройство для сравнения кодов | 1983 |

|

SU1103220A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Устройство для преобразования булевых функций | 1988 |

|

SU1532946A1 |

| Вычислительное устройство | 1985 |

|

SU1517021A1 |

| Схема сравнения кодов | 1982 |

|

SU1016778A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СВОЙСТВ ПОЛНОТЫ ЛОГИЧЕСКИХ ФУНКЦИЙ, содержащее п счетных триггеров, где п - число переменных анализируемых логических функций, п -разрядный коммутатор триггерных сигналов, два формирователя импульсов, D-триггер, п-разрядньм регистр сдвига,пятиразрядньй регистр памяти,(п-1)-разрядньй двоичньй счетчик, ждущий генератор тактов, два элемента задержки, десять элементов И, два элемента ИЛИ, два R5-триггера и два элемента РАВНОЗНАЧНОСТЬ, причем выходы счетных триггеров соединены с соответствующими первыми и вторыми за исключением первого разряда информационными, входами разрядов коммутатора триггерных сигналов, первые выходы разрядов которого подключены к соответствующим входам счетных триггеров за исключением первого триггера, счетный вход которого соединен с выходом первого элемента задержки,входом уста ювки нуля первого RS-трмггера и В, орым информационным входом первого разряда кок-гутатора триггерных сигналов, инверсные выходы счетных трип еров соединены с соответствующими третьими инфор1.шционны1 ш входами разрядов коммутатора триггерньк сигналов, первые управляющие входы разрядов которого соединены с соответствующими выходами регистра сдвига и с первыми входами установку О счетных.триггеров, а вторые управляющие ВХ.ОДЫ разрядов кo fм тaтopa триггерпых сигналов подключены к прямому выходу второго RS-триггера и первоЬгу входу первого элемента И, второй вход которого соединен с выходом ждущего генератора тактов, с входом первого элемента задержки и с первы п входам второго и третьего элементов И, вторые входы которых i подключены соответственно к инверс(Л ному выходу второго RS-триггера и к гтрямому выходу первого RS-триггера, вход установки О второго КЗ-триггера подключен к первому входу первого элемента ИЛИ, к тактовоьту входу регистра сдвига, к входу синхронизации D-триггера и к выходу первого ч1 формирователя импульсов, вход котороо 1 а го подключен к выходу счетного триг.гера, I) -вход D -триггера подключен к шине логической единицы устройства, а инверсньш выход соединен с информационным входом регистра сдвига, выход п-го разряда которого подключен к первому входу четвертого элемента И, второй вход которого соединен с вьсходом второго формирователя импульсов, вход которого соединен с выходом (n-l)-ro счетного триггера, выход четвертого элемента И является выходом сигнала окончания работы устройства и соединен с вторым входом первого элемента ИЖ и с первым стоп-вхопом ждущего генератора так

| Устройство для распознавания функциональной полноты систем логических функций | 1979 |

|

SU960795A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Рабочий ротор | 1976 |

|

SU660812A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-30—Публикация

1984-02-03—Подача