Изобретение относится к автоматике и вычислительной технике и может быть использовано в различных оптоэлектронных схемах параллельной обработки изображений при построении матричных процессоров, для вычисления логических функций изображений методами клеточной логики.

Цель изобретения - упрощение устройства, обусловленное применением биспин- фотоприемников в качестве базовых ячеек устройства, и связанное с этим повышение быстродействия устройства.

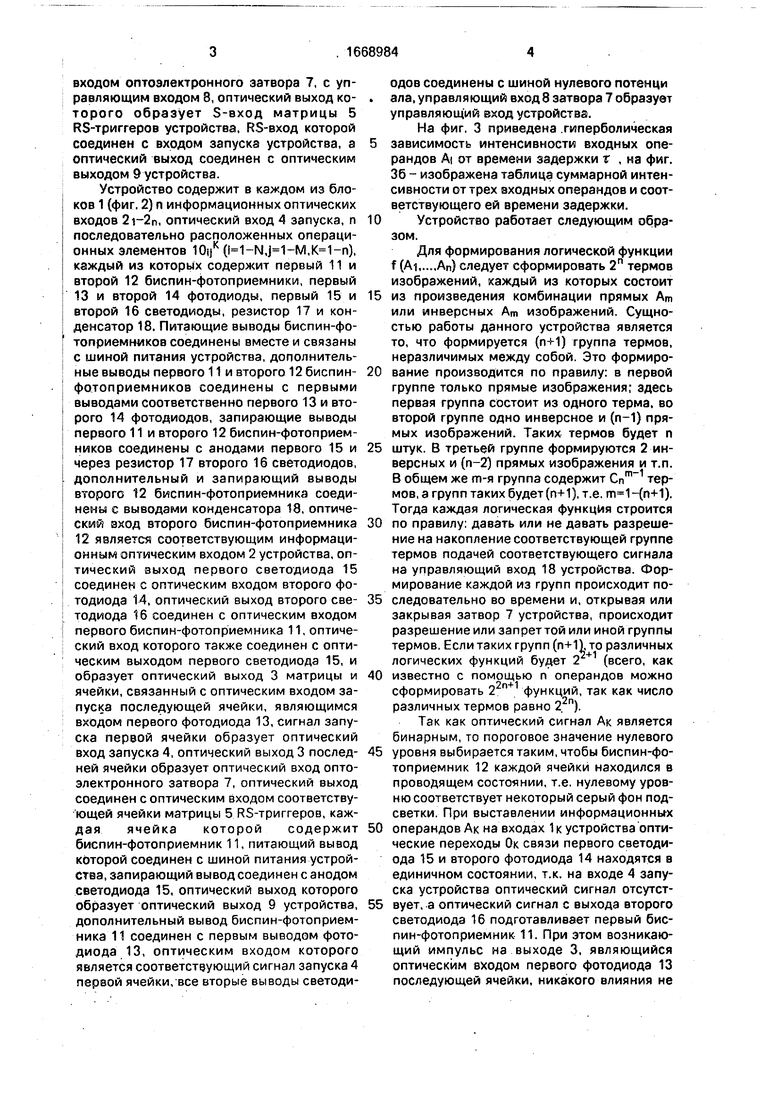

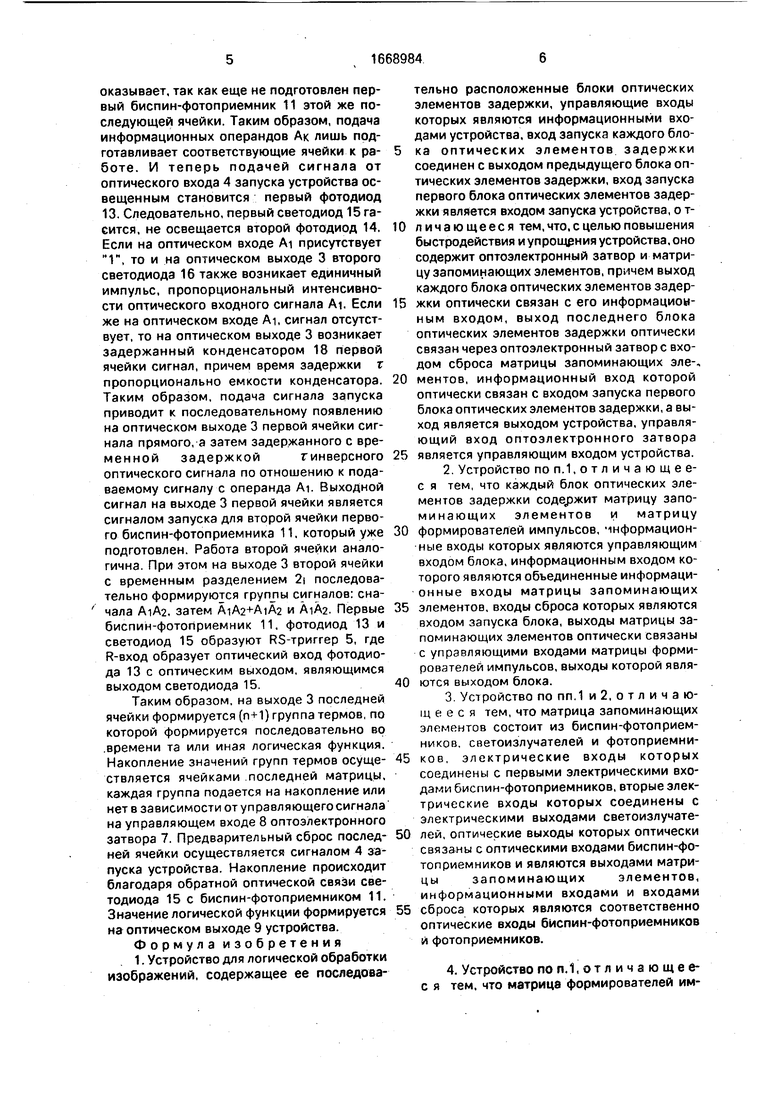

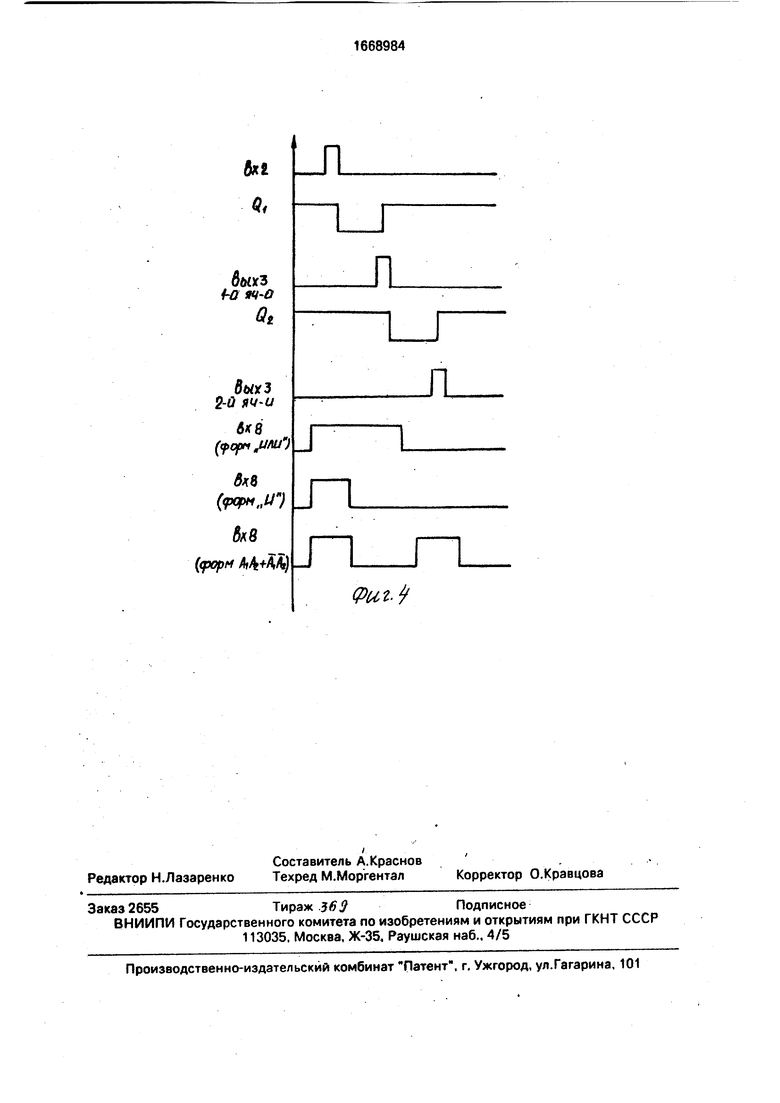

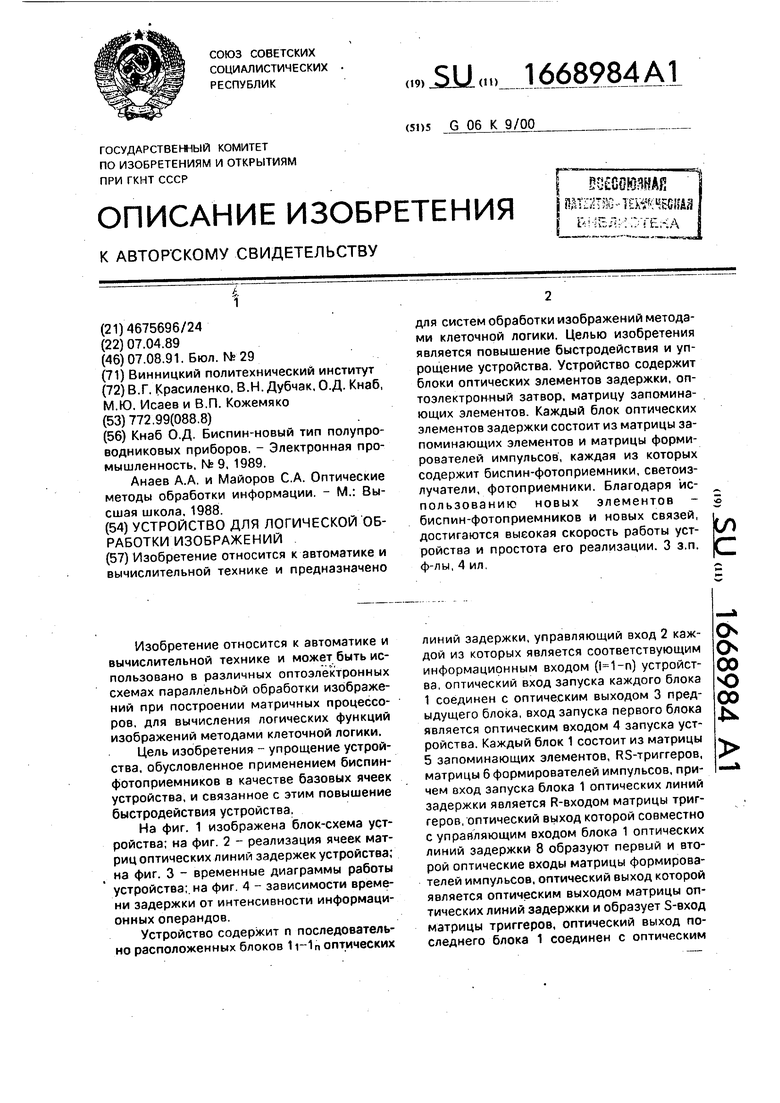

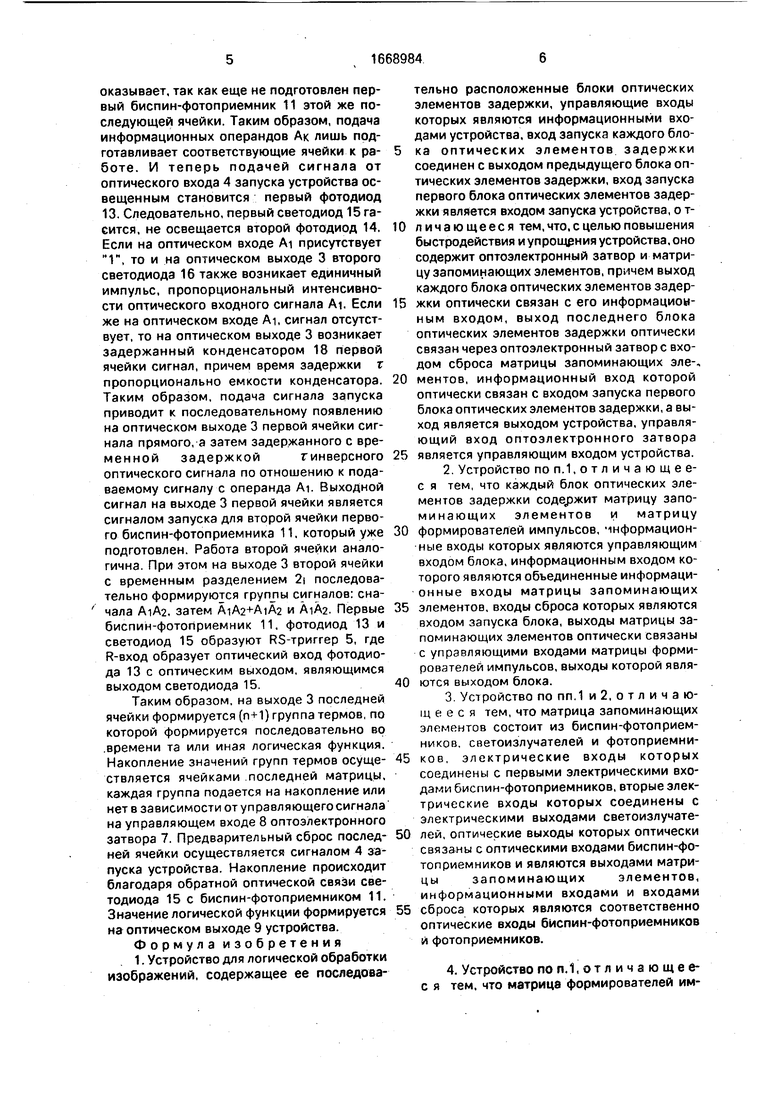

На фиг. 1 изображена блок-схема устройства: на фиг 2 - реализация ячеек матриц оптических линий задержек устройства; на фиг. 3 - временные диаграммы работы устройства: на фиг 4 - зависимости времени задержки от интенсивности информационных операндов.

Устройство содержит п последовательно расположенных блоков 1 г-1п оптических

линий задержки, управляющий вход 2 каждой из которых является соответствующим информационным входом (l-1-n) устройства, оптический вход запуска каждого блока 1 соединен с оптическим выходом 3 предыдущего блока, вход запуска первого блока является оптическим входом 4 запуска устройства. Каждый блок 1 состоит из матрицы 5 запоминающих элементов, RS-триггеров, матрицы 6 формирователей импульсов, причем оход запуска блока 1 оптических линий задержки является R-входом матрицы триггеров, оптический выход которой совместно с управляющим входом блока 1 оптических линий задержки 8 образуют первый и второй оптические входы матрицы формирователей импульсов, оптический выход которой является оптическим выходом матрицы оптических линий задержки и образует S-вход матрицы триггеров, оптический выход последнего блока 1 соединен с оптическим

СЬ

Os

00 Ю 00

ь

входом оптоэлектронного затвора 7, с управляющим входом 8, оптический выход которого образует S-вход матрицы 5 RS-триггеров устройства, RS-вход которой соединен с входом запуска устройства, а оптический выход соединен с оптическим выходом 9 устройства.

Устройство содержит в каждом из блоков 1 (фиг, 2) п информационных оптических входов 2i-2n, оптический вход 4 запуска, п последовательно расположенных операционных элементов 10ijK (,,), каждый из которых содержит первый 11 и второй 12 биспин-фотоприемники, первый 13 и второй 14 фотодиоды, первый 15 и второй 16 светодиоды, резистор 17 и конденсатор 18. Питающие выводы биспин-фо- топриемников соединены вместе и связаны с шиной питания устройства, дополнительные выводы первого 11 и второго 12 биспин- фотоприемников соединены с первыми выводами соответственно первого 13 и второго 14 фотодиодов, запирающие выводы первого 11 и второго 12 биспин-фотоприем- ников соединены с анодами первого 15 и через резистор 17 второго 16 светодиодов, дополнительный и запирающий выводы второго 12 биспин-фотоприемника соединены с выводами конденсатора 18, оптический вход второго биспин-фотоприемника 12 является соответствующим информационным оптическим входом 2 устройства, оптический выход первого светодиода 15 соединен с оптическим входом второго фотодиода 14, оптический выход второго светодиода 16 соединен с оптическим входом первого биспин-фотоприемника 11, оптический вход которого также соединен с оптическим выходом первого светодиода 15, и образует оптический выход 3 матрицы и ячейки, связанный с оптическим входом запуска последующей ячейки, являющимся входом первого фотодиода 13, сигнал запуска первой ячейки образует оптический вход запуска 4, оптический выход 3 последней ячейки образует оптический вход оптоэлектронного затвора 7, оптический выход соединен с оптическим входом соответствующей ячейки матрицы 5 RS-триггеров, каждая ячейка которой содержит биспин-фотоприемник 11, питающий вывод которой соединен с шиной питания устройства, запирающий вывод соединен с анодом светодиода 15, оптический выход которого образует оптический выход 9 устройства, дополнительный вывод биспин-фотоприемника 11 соединен с первым выводом фотодиода 13, оптическим входом которого является соответствующий сигнал запуска 4 первой ячейки, все вторые выводы светодиодов соединены с шиной нулевого потенци ала, управляющий вход 8 затвора 7 образует управляющий вход устройства.

На фиг. 3 приведена гиперболическая

зависимость интенсивности входных операндов А| от времени задержки г , на фиг, 36 - изображена таблица суммарной интенсивности от трех входных операндов и соответствующего ей времени задержки.

0 Устройство работает следующим образом.

Для формирования логической функции

f (AiAn) следует сформировать 2 термов

изображений, каждый из которых состоит

5 из произведения комбинации прямых Am или инверсных Ат изображений. Сущностью работы данного устройства является то, что формируется (п+1) группа термов, неразличимых между собой. Это формиро0 вание производится по правилу: в первой группе только прямые изображения; здесь первая группа состоит из одного терма, во второй группе одно инверсное и (п-1) прямых изображений. Таких термов будет п

5 штук. В третьей группе формируются 2 инверсных и (п-2) прямых изображения и т.п. В общем же m-я группа содержит термов, а групп таких будет (п+1), т.е. (n+1). Тогда каждая логическая функция строится

0 по правилу: давать или не давать разрешение на накопление соответствующей группе термов подачей соответствующего сигнала на управляющий вход 18 устройства. Формирование каждой из групп происходит по5 следовательно во времени и, открывая или закрывая затвор 7 устройства, происходит разрешение или запрет той или иной группы термов. Если таких групп (п+1), то различных логических функций будет 2 (всего, как

0 известно с помощью п операндов можно сформировать 22n+1 функций, так как число различных термов равно 2 ).

Так как оптический сигнал Ак является бинарным, то пороговое значение нулевого

5 уровня выбирается таким, чтобы биспин-фотоприемник 12 каждой ячейки находился в проводящем состоянии, т.е. нулевому уровню соответствует некоторый серый фон подсветки. При выставлении информационных

0 операндов Ак на входах 1 к устройства оптические переходы Ок связи первого светодиода 15 и второго фотодиода 14 находятся в единичном состоянии, т.к. на входе 4 запуска устройства оптический сигнал отсутст5 вует, а оптический сигнал с выхода второго светодиода 16 подготавливает первый биспин-фотоприемник 11. При этом возникающий импульс на выходе 3, являющийся оптическим входом первого фотодиода 13 последующей ячейки, никакого влияния не

оказывает, так как еще не подготовлен первый биспин-фотоприемник 11 этой же последующей ячейки. Таким образом, подача информационных операндов Ак лишь подготавливает соответствующие ячейки к работе. И теперь подачей сигнала от оптического входа 4 запуска устройства освещенным становится первый фотодиод 13. Следовательно, первый светодиод 15 гасится, не освещается второй фотодиод 14. Если на оптическом входе AI присутствует 1, то и на оптическом выходе 3 второго светодиода 16 также возникает единичный импульс, пропорциональный интенсивности оптического входного сигнала AL Если же на оптическом входе AI, сигнал отсутствует, то на оптическом выходе 3 возникает задержанный конденсатором 18 первой ячейки сигнал, причем время задержки т пропорционально емкости конденсатора. Таким образом, подача сигнала запуска приводит к последовательному появлению на оптическом выходе 3 первой ячейки сигнала прямого, а затем задержанного с временной задержкойгинверсного оптического сигнала по отношению к подаваемому сигналу с операнда AL Выходной сигнал на выходе 3 первой ячейки является сигналом запуска для второй ячейки первого биспин-фотоприемника 11, который уже подготовлен. Работа второй ячейки аналогична. При этом на выходе 3 второй ячейки с временным разделением 2i последовательно формируются группы сигналов: сна- чала AiA2, затем AiA2+AiA2 и AiA2. Первые биспин-фотоприемник 11, фотодиод 13 и светодиод 15 образуют RS-триггер 5, где R-вход образует оптический вход фотодиода 13 с оптическим выходом, являющимся выходом светодиода 15.

Таким образом, на выходе 3 последней ячейки формируется (п+1) группа термов, по которой формируется последовательно во времени та или иная логическая функция. Накопление значений групп термов осуществляется ячейками последней матрицы, каждая группа подается на накопление или нет в зависимости от управляющего сигнала на управляющем входе 8 оптоэлектронного затвора 7. Предварительный сброс последней ячейки осуществляется сигналом 4 запуска устройства. Накопление происходит благодаря обратной оптической связи светодиода 15 с биспин-фотоприемником 11. Значение логической функции формируется на оптическом выходе 9 устройства. Формула изобретения 1. Устройство для логической обработки изображений, содержащее ее последовательно расположенные блоки оптических элементов задержки, управляющие входы которых являются информационными входами устройства, вход запуска каждого блока оптических элементов задержки соединен с выходом предыдущего блока оптических элементов задержки, вход запуска первого блока оптических элементов задержки является входом запуска устройства, о тличающееся тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит оптоэлектронный затвор и матрицу запоминающих элементов, причем выход каждого блока оптических элементов задержки оптически связан с его информационным входом, выход последнего блока оптических элементов задержки оптически связан через оптоэлектронный затвор с входом сброса матрицы запоминающих эле-,

ментов, информационный вход которой оптически связан с входом запуска первого блока оптических элементов задержки, а выход является выходом устройства, управляющий вход оптоэлектронного затвора

является управляющим входом устройства.

2.Устройство по п.1, о т л и ч а ю щ е е- с я тем, что каждый блок оптических элементов задержки содержит матрицу запоминающих элементов и матрицу

формирователей импульсов, информационные входы которых являются управляющим входом блока, информационным входом которого являются обьединенные информационные входы матрицы запоминающих

элементов, входы сброса которых являются входом запуска блока, выходы матрицы запоминающих элементов оптически связаны с управляющими входами матрицы формирователей импульсов, выходы которой являются выходом блока.

3.Устройство по пп.1 и2,отличаю- щ е е с я тем, что матрица запоминающих элементов состоит из биспин-фотоприем- ников, светоизлучателей и фотоприемников, электрические входы которых соединены с первыми электрическими входами бисиин-фотоприемников, вторые электрические входы которых соединены с электрическими выходами светоизлучателей, оптические выходы которых оптически связаны с оптическими входами биспин-фо- топриемников и являются выходами матрицы запоминающих элементов, информационными входами и входами

сброса которых являются соответственно оптические входы биспин-фотоприемников и фотоприемников.

4.Устройство поп.1,отличающее- с я тем, что матрица формирователей импульсов состоит из биспин-фотоприемни- ков, светоиэлучателей, фотоприемников и RS-триггеров, входы которых подключены к электрическим входам биспин-фотоприемников, выходы - к электрическому входу и 5 ческие выходы светоизлучателей являются выходу фотоприемников и светоизлучате- выходами матрицы.

ле( соответственно, информационными и управляющими входами матрицы являются соответственно оптические входы биспин- фотоприемников и фотоприемников, а опти

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логической обработки изображений | 1989 |

|

SU1711201A1 |

| Устройство для коммутации оптических бинарных изображений | 1989 |

|

SU1795439A1 |

| Устройство для логической обработки изображений | 1988 |

|

SU1658181A1 |

| Устройство для логической обработки изображений | 1989 |

|

SU1679510A1 |

| Устройство для выделения эквиденсит изображений | 1989 |

|

SU1705845A1 |

| Оптоэлектронный регистр сдвига | 1988 |

|

SU1646000A1 |

| Оптоэлектронный узел матрицы для сравнения изображений | 1990 |

|

SU1746389A1 |

| Оптоэлектронная бистабильная ячейка | 1989 |

|

SU1711230A1 |

| Оптоэлектронная бистабильная ячейка | 1988 |

|

SU1635252A1 |

| Функциональный аналого-цифровой преобразователь изображений параллельного типа | 1989 |

|

SU1749882A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для систем обработки изображений методами клеточной логики. Целью изобретения является повышение быстродействия и упрощение устройства. Устройство содержит блоки оптических элементов задержки, оптоэлектронный затвор, матрицу запоминающих элементов. Каждый блок оптических элементов задержки состоит из матрицы запоминающих элементов и матрицы формирователей импульсов, каждая из которых содержит биспин-фотоприемники, светоизлучатели, фотоприемники. Благодаря использованию новых элементов - биспин-фотоприемников и новых связей достигаются высокая скорость работы устройства и простота его реализации. 3 з.п.ф-лы, 4 ил.

Фи..1

Фи.г

„о

7,

J

Q

п

бкхз

f-0 ЯЧ-О

Qt

дыхз 2-й яч-и

бхв|

) J

8

(w,;

П

ЬкВ (рорм А4МЛг)

U) J

Л

Л

г.

| Кнаб О.Д | |||

| Биспин-новый тип полупроводниковых приборов | |||

| - Электронная промышленность, № 9, 1989 | |||

| Анаев А.А | |||

| и Майоров С.А | |||

| Оптические методы обработки информации | |||

| - М.: Высшая школа | |||

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1991-08-07—Публикация

1989-04-07—Подача