Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема относительного биимпульсного сигнала | 1988 |

|

SU1614117A1 |

| Приемник биимпульсного сигнала | 1988 |

|

SU1584111A1 |

| Устройство для формирования опорной частоты | 1978 |

|

SU786033A1 |

| Устройство для приема относительного биимпульсного сигнала | 1985 |

|

SU1312748A1 |

| Устройство передачи и приема двоичных сигналов | 1985 |

|

SU1501290A1 |

| Устройство для приема относительного биимпульсного сигнала | 1988 |

|

SU1536519A1 |

| Устройство для приема относительного биимпульсного сигнала | 1988 |

|

SU1525930A1 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1406809A2 |

| Биимпульсный регенератор | 1986 |

|

SU1413727A2 |

| Устройство восстановления тактового сигнала из цифрового потока | 1991 |

|

SU1757114A1 |

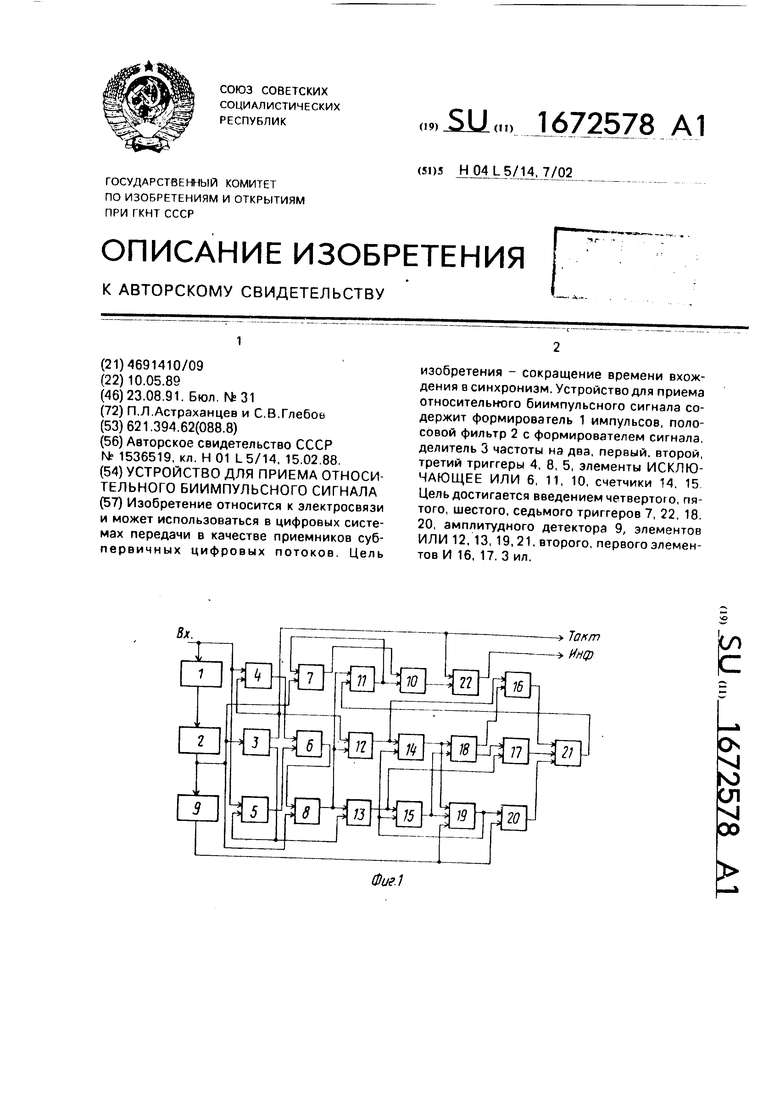

Изобретение относится к электросвязи и может использоваться в цифровых системах передачи в качестве приемников субпервичных цифровых потоков. Цель изобретения - сокращение времени вхождения в синхронизм. Устройство для приема относительного биимпульсного сигнала содержит формирователь 1 импульсов, полосовой фильтр 2 с формирователем сигнала, делитель 3 частоты на два, первый, второй, третий триггеры 4, 8, 5, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 6, 11, 10, счетчики 14, 15. Цель достигается введением четвертого, пятого, шестого, седьмого триггеров 7, 22, 18, 20, амплитудного детектора 9, элементов ИЛИ 12, 13, 19, 21, второго, первого элементов И 16, 17. 3 ил.

О

XI

го ел XI

00

Изобретение относится к электросвязи и может использоваться в цифровых системах передачи в качестве приемников субпервичных цифровых потоков.

Цель изобретения - сокращение времени вхожедния в синхронизм.

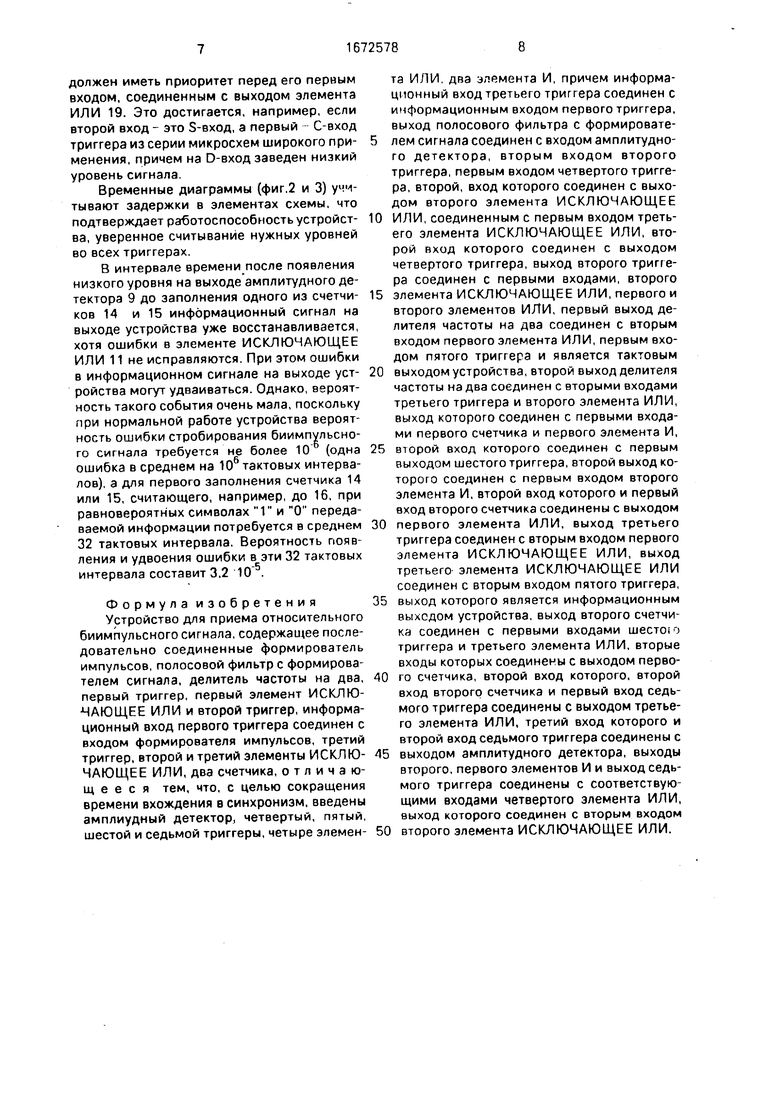

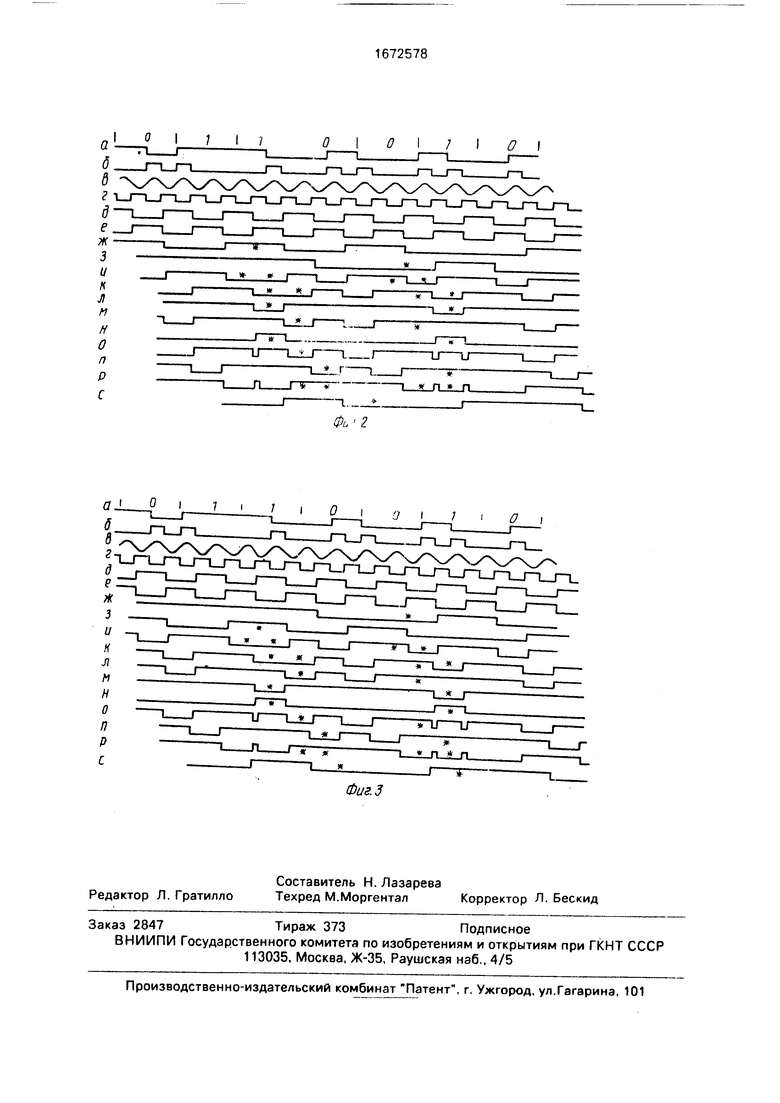

На фиг.1 изображена структурная электрическая схема предложенного устройства; на фиг.2 и 3 - временные диаграммы, поясняющие работу.

Устройство содержит формирователь 1 импульсов, полосовой фильтр 2 с формирователем сигнала, делитель 3 частоты на два, первый и третий триггеры 4 и 5, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, четвертый и второй триггеры 7 и 8, амплитудный детектор 9, третий и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и 11, первый и второй элементы ИЛИ 12 и 13, второй и первый счетчики 14 и 15, второй и первый элементы И 16 и 17, шестой триггер 18, третий элемент ИЛИ 19, седьмой триггер 20, четвертый элемент ИЛИ 21, пятый триггер 22.

Устройство работает следующим образом.

На вход устройства поступает относительный биимпульсный сигнал (фиг.2 и За), в котором на каждом тактовом интервале присутствует два импульса разного уровня с обязательным переходом от одного уровня к другому в середине интервала, причем при передаче символа 1 сохраняется, а при передаче символа О изменяется последовательность чередования уровней на очередном тактовом интервале по сравнению с предыдущим.

Входной биимпульсный сигнал подается на вход формирователя 1 импульсов, преобразующего все переходы из одного уровня в другой в этом сигнале в последовательность импульсов (фиг.2 и 36). Из полученного сигнала полосовой фильтр (фиг.2с) формирователем сигнала вырабатывает сначала синусоидальный (фиг.2 и Зв), а затем импульсный сигналы (фиг.2 и Зг) удвоенной тактовой частоты. С помощью делителя 3 частоты на два образуется восстановленный тактовый сигнал согласно диаграмме на фиг.2д либо согласно диаграмме на фиг.Зд в зависимости от начальных условий работы делителя 2, а на инверсном выходе делителя 3 формируется сигнал тактовой частоты (фиг.2 и Зе), инверсный сигналу на фиг.2 и Зд. Первый и второй триггеры 4 и 5 положительными фронтами сигналов тактовых частот(фиг.2 иЗд, е)стро- бируют входной биимпульсный сигнал (фиг.2 и За), в результате чего на их выходах образуются сигналы соответственно согласно фиг.2 и Зж,е. Эти выходные сигналы суммируются

по модулю два в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 6, образуя сигнал на фиг.2 и Зи,

Поскольку один из триггеров 4 и 5 считывает значения уровней первой половины

тактового интервала биимпульсного сигнала (фиг.2 и За), а другой триггер - значения второй половины, а моменты стробирова- ния в этих триггерах сдвинуты на половину тактового интервала, то выходной сигнал

0 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 (фиг.2и) можно рассматривать состоящим из двух последовательностей импульсов длительностью в половину тактового интервала, причем импульсы этих двух последователь5 ностей чередуются. Одна, регулярная, последовательность - это результат сравнения уровня первой половины тактового интервала с уровнем второй половины тактового интервала биимпульсного сигна0 ла (фиг.2 и За), Так как эти уровни должны быть противоположны, то в сигнале (фиг.2 и Зи) эта последовательность представляется только импульсами высокого уровня. Другая, случайная, последовательность - это реL зультат сравнения в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ буровня второй половины тактового интервала с уровнем первой половины следующего тактового интервала сигнала (фиг.2 и За), Этот результат - импульс

0 высокого уровня при передаче символа 1 и импульс низкого уровня при передаче символа О в биимпульсном сигнале.

Однако возникающие в биимпульсном сигнале (фиг.2 и За) искажения уровней на

5 половинах тактовых интервалов приводят к ошибкам стробирования в выходных сигналах триггеров 4 и 5 (фиг.2 и Зж,з) и соответственно в выходном сигнале элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 (фиг.2 и Зи. звез0 дочки). Из временных диаграмм видно, что одна ошибка попадает в обе последовательности сигнала (фиг.2 и Зи), изменяя уровни на соседних половинах тактовых интервалов.

5 В четвертом триггере 8 сигнал (фиг.2 и Зи) задерживается на половину тактового интервала (фиг.2 и Зк). Выходной сигнал триггера 8 стробиреутся в элементах ИЛИ 12 и 13 сигналами тактовых частот с прямого

0 и инверсного выходов делителя 3 частоты на два (фиг.2 и Зд,е). На выходах элемента ИЛИ 12 (сигнал нз фиг.2 и Зл) и элемента ИЛИ 13 (сигнал на фиг. 2 и Зм) выделяются по отдельности указанные ранее в сигнале (фиг.2

5 и Зм) последовательности импульсов. Ввиду того, что фаза сигналов тактовых частот (фиг,2 и Зд,е) устанавливается случайно, то любая из двух последовательностей может попасть на выход как элемент ИЛИ 12, так и элемента ИЛИ 13. На временных диаграммах(фиг.З) регулярная последовательность, в которой импульсы низкого уровня вызваны только ошибками, попадает на выход элемента ИЛИ 12 (фиг.2л), а на фиг.З, наоборот - на выход элемента ИЛИ 13 (фиг.Зм). Эти сигналы являются последовательностями ошибок. Случайные последовательности (искажаемые ошибками), имеющие импульсы низкого уровня при передаче символа О, показаны на фиг.2м, Зл.

Выходные сигналы элементов ИЛИ 12 и

13поступают на тактовые входы счетчиков

14и 15, который увеличивает свое состояние на единицу при поступлении на тактовый вход импульса низкого уровня. Выходы этих счетчиков - это выходы их n-х разрядов. После счета определенного количества импульсов на выходах счетчиков появляется высокий уровень сигнала. Поскольку при удовлетворительном качестве приема в случайной последовательности (фиг.2м. Зл) импульсов больше, чем в последоеэ ельности ошибок (фиг.2л, Зм), то первым окончит счет счетчик, на вход которого поступает случайная последовательность. Если этим счетчиком окажется счетчик 14, то сигналом высокого уровня с его выхода триггер 18 будет установлен так, что сигнал высокого уровня появится на его втором выходе и откроет элемент И 17. Если первым закончит счет счетчик 15, то триггер 18, наоборот, сформирует высокий уровень на первом выходе, и открытым окажется первый элемент И 16. Одновременно, после окончания счета какого-либо счетчика сигнал высокого уровня с его выхода пройдет через элемент ИЛИ 19 на установочные входы счетчиков 14 и 15 и вызовет их обнуление, а следовательно, снятие высокого уровня с выхода элемента ИЛИ 19. После этого процесс счета и счетчиках начинается заново. Выходной сигнал высокого уровня элемента ИЛИ 19, кроме того, устанавливает триггер 20 в состояние О. Таким образом, оказывается открытым только один из элементов И 16 и 17, причем через него на вход элемента ИЛИ 21 поступает последовательность ошибок либо с выхода элемента ИЛИ 12 (фиг.2л), либо с выхода элемента ИЛИ 13 (фиг.Зм). На другие два входа элемента ИЛИ 21 поступают сигналы низкого уровня с выхода закрытого элемента И 16 или 17 и с выхода триггера 20. На вход элемента ИЛИ 21 проходит с инверсией последовательность ошибок (фиг,2 и Зи).

Эта последовательность ошибок суммируется по модулю два. в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 11 с выходным сигналом триггера 8 (фиг.2 и Зк). В результате суммирования исправляются ошибки, попадаю-

щие в регулярную последовательность сигнала (фиг.2 и Зк) (сигнал на фиг.2 и Зо). Сигнал (фиг.2 и Зо) задерживается на половину тактового интервала в третьем триггере 7 5 (фиг.2 и Зп), затем сигналы (фиг.2 и Зо,п) суммируются по модулю два во втором элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 10. В выходном сигнале элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 (фиг.2 и Зр) импульсы случайной по10 следовательности из выходного сигнала триггера 8 (фиг.2 и Зк) занимают уже две последовательные половины тактового интервала. Это делает возможным считывание сигналов (фиг.2 и Зр) в триггер 22 сигналом

15 тактовой частоты (фиг.2 и Зд) с любой из двух его возможных фаз. Выходной сигнал триггера 22 - это восстановленный информационный сигнал (фиг.2 и Зс), в котором на одно искажение биимпульсного сигнала (фиг.2 и

0 За) приходится ошибка на одном тактовом интервале.

Для того, чтобы после включения устройства или вскоре после начала поступления входного биимпульсного сигнала не

5 происходили неэерные исправления ошибок в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 11. амплитудный детектор 9 оценивает наличие импульсов (фиг.2 и Зг) на выходе полосового фильтра 2 с формирователем сигнала. Если

0 эти импульсы отсутствуют (амплитуда сигнала меньше требуемого высокого логического уровня), то на выходе амплитудного детектора 9 образуется сигнал высокого уровня, который через элемент ИЛИ 19 об5 нуляет счетчики 14 и 15 и устанавливает триггер 20 в состояние 1. Выходной сигнал высокого уровня триггера 20 постоянно поддерживает на выходе элемента ИЛИ 21 сигнал низкого уровня, предотвращая исп0 равление ошибочных импульсов в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 11.

После начала работы устройства возникают колебания в полосовом фильтре 2 с формирователем сигнала, на выходе ампли5 тудного детектора 9 появляется сигнал низкого уровня, снимается сигнал высокого уровня с установленных входов счетчиков 14 и 15, Счетчики, находящиеся в нулевом состоянии, оказываются подготовленными

0 к счету импульсов. Однако, на выходе триггера 20 сохраняется сигнал высокого уровня до тех пор, пока первый раз не заполнится какой-либо из счетчиков 14 и 15 и пока сигнал высокого уровня с выхода счетчика, пройдя

5 через элемент ИЛИ 19, не установит триггер 20 в состояние О. Только после этого станет возможным прохождение последовательности ошибок через элемент ИЛИ 21.

Второй вход триггера 20, подключенный к выходу амплитудного детектора 9.

должен иметь приоритет перед его первым входом, соединенным с выходом элемента ИЛИ 19. Это достигается, например, если второй вход - это S-вход, а первый - С-вход триггера из серии микросхем широкого применения, причем на D-вход заведен низкий уровень сигнала.

Временные диаграммы (фиг.2 и 3) учитывают задержки в элементах схемы, что подтверждает работоспособность устройства, уверенное считывание нужных уровней во всех триггерах.

В интервале времени после появления низкого уровня на выходе амплитудного детектора 9 до заполнения одного из счетчиков 14 и 15 информационный сигнал на выходе устройства уже восстанавливается, хотя ошибки в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 11 не исправляются. При этом ошибки в информационном сигнале на выходе устройства могут удваиваться. Однако, вероятность такого события очень мала, поскольку при нормальной работе устройства вероятность ошибки стробирования биимпульсно- го сигнала требуется не более 10 (одна ошибка в среднем на 106 тактовых интервалов), а для первого заполнения счетчика 14 или 15, считающего, например, до 16, при равновероятных символах 1 и О передаваемой информации потребуется в среднем 32 тактовых интервала. Вероятность появления и удвоения ошибки в эти 32 тактовых интервала составит 3,2 10 .

Формула изобретения Устройство для приема относительного биимпульсногосигнала, содержащее последовательно соединенные формирователь импульсов, полосовой фильтр с формирователем сигнала, делитель частоты на два, первый триггер, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и второй триггер, информационный вход первого триггера соединен с входом формирователя импульсов, третий триггер, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, два счетчика, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм, введены амплиудный детектор, четвертый, пятый, шестой и седьмой триггеры, четыре элемента ИЛИ. два элемента И, причем информационный вход третьего триггера соединен с информационным входом первого триггера, выход полосового фильтра с формирователем сигнала соединен с входом амплитудного детектора, вторым входом второго триггера, первым входом четвертого триггера, второй, вход которого соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, соединенным с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом четвертого триггера, выход второго триггера соединен с первыми входами, второго

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первого и второго элементов ИЛИ, первый выход делителя частоты на два соединен с вторым входом первого элемента ИЛИ, первым входом пятого триггера и является тактовым

выходом устройства, второй выход делителя частоты на два соединен с вторыми входами третьего триггера и второго элемента ИЛИ, выход которого соединен с первыми входами первого счетчика и первого элемента И,

второй вход которого соединен с первым выходом шестого триггера, второй выход которого соединен с первым входом второго элемента И, второй вход которого и первый вход второго счетчика соединены с выходом

первого элемента ИЛИ, выход третьего триггера соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом пятого триггера,

выход которого является информационным выходом устройства, выход второго счетчика соединен с первыми входами шестого триггера и третьего элемента ИЛИ, вторые входы которых соединены с выходом первого счетчика, второй вход которого, второй вход второго счетчика и первый вход седьмого триггера соединены с выходом третьего элемента ИЛИ, третий вход которого и второй вход седьмого триггера соединены с

выходом амплитудного детектора, выходы второго, первого элементов И и выход седьмого триггера соединены с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с вторым входом

0 второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

- i о i 0

iГ i.-f

/ ,

| Устройство для приема относительного биимпульсного сигнала | 1988 |

|

SU1536519A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-08-23—Публикация

1989-05-10—Подача