4

Изобретение относится к передаче дискретной информации по каналам связи и может быть использовано в регенераторах цифровых сигналов для восстановления тактового сигнала из цифрового потока.

Целью изобретения является повышение точности восстановления тактового сигнала путем обеспечения синхронизации как от фронта, так и от спада импульсов опорной последовательности.

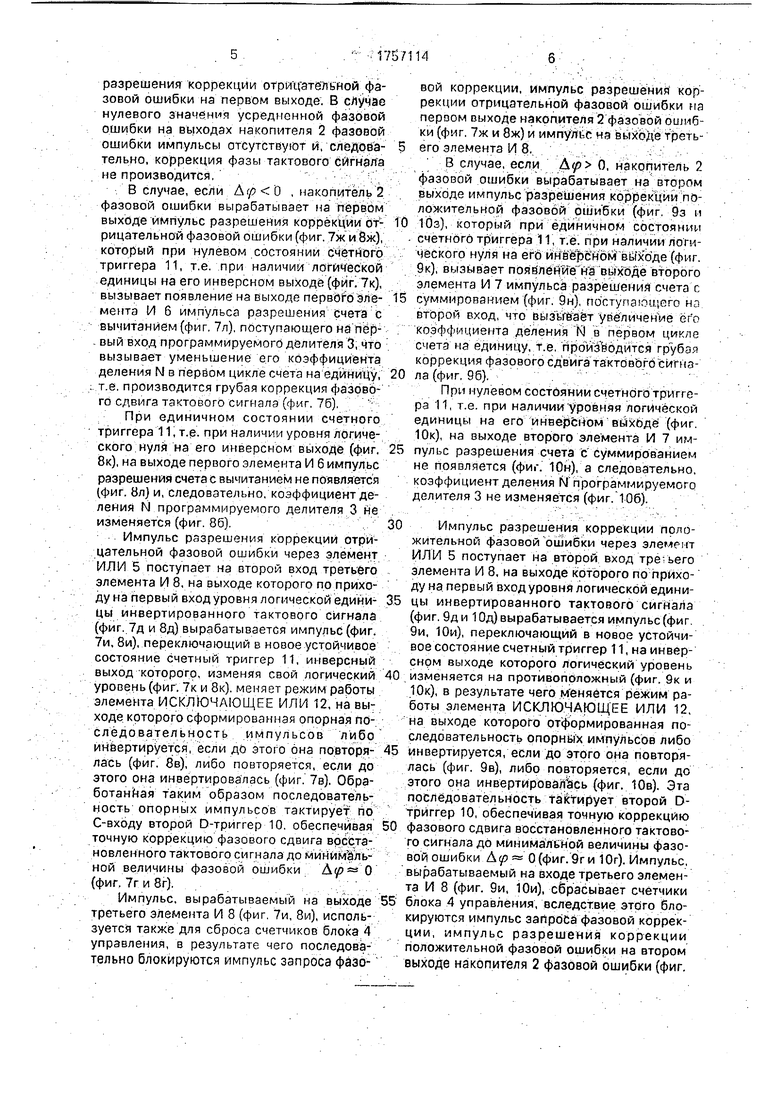

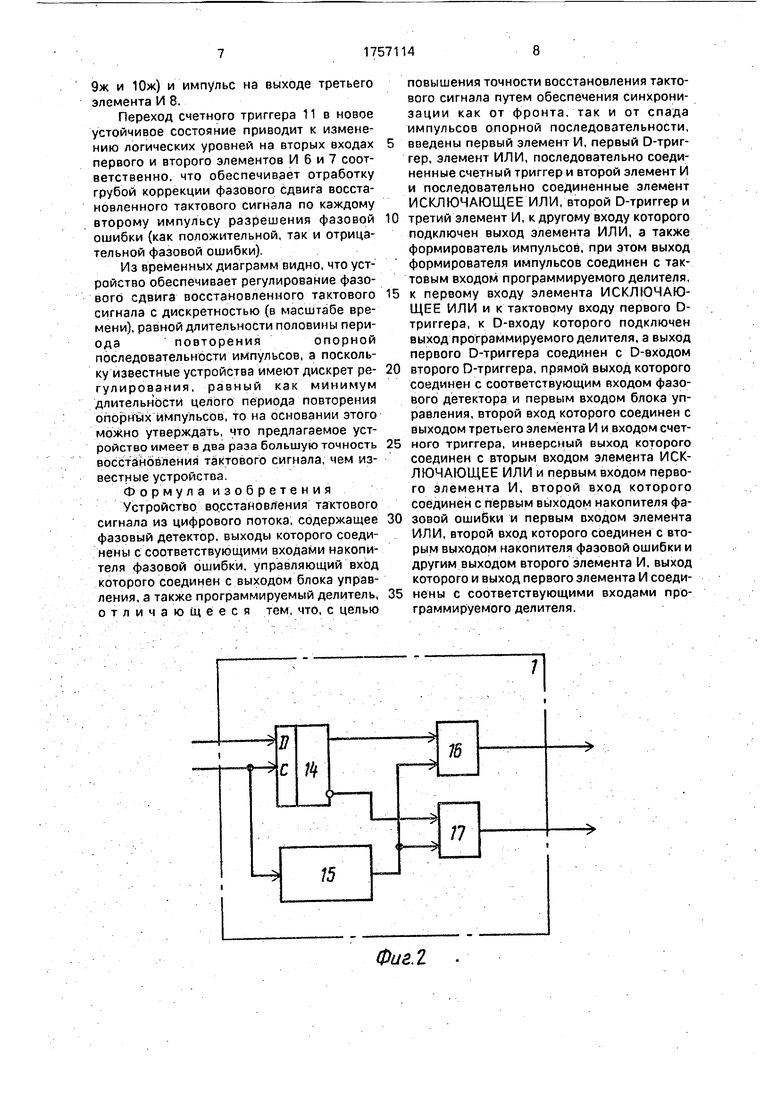

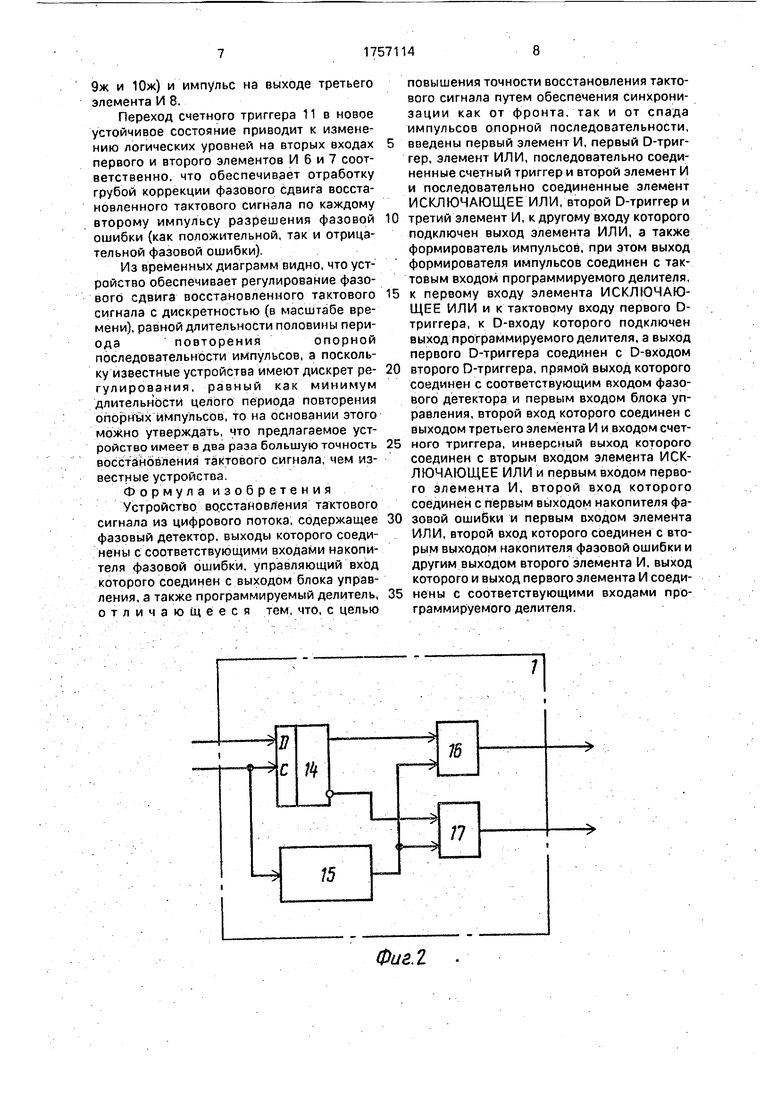

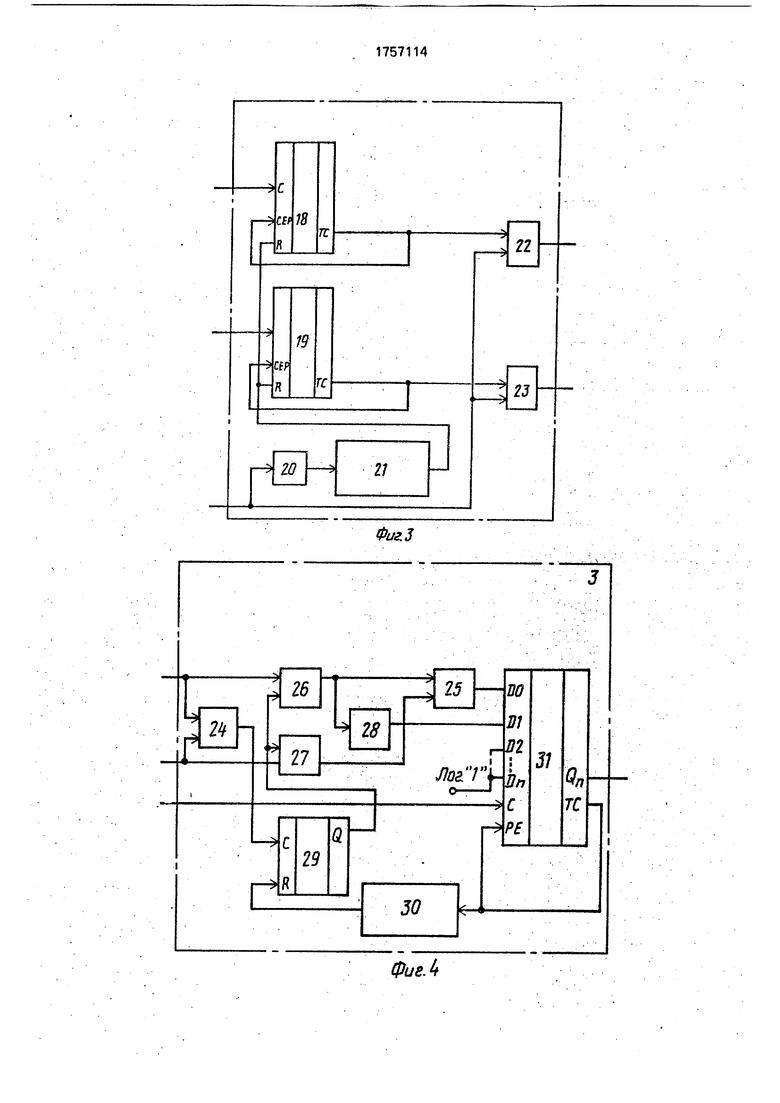

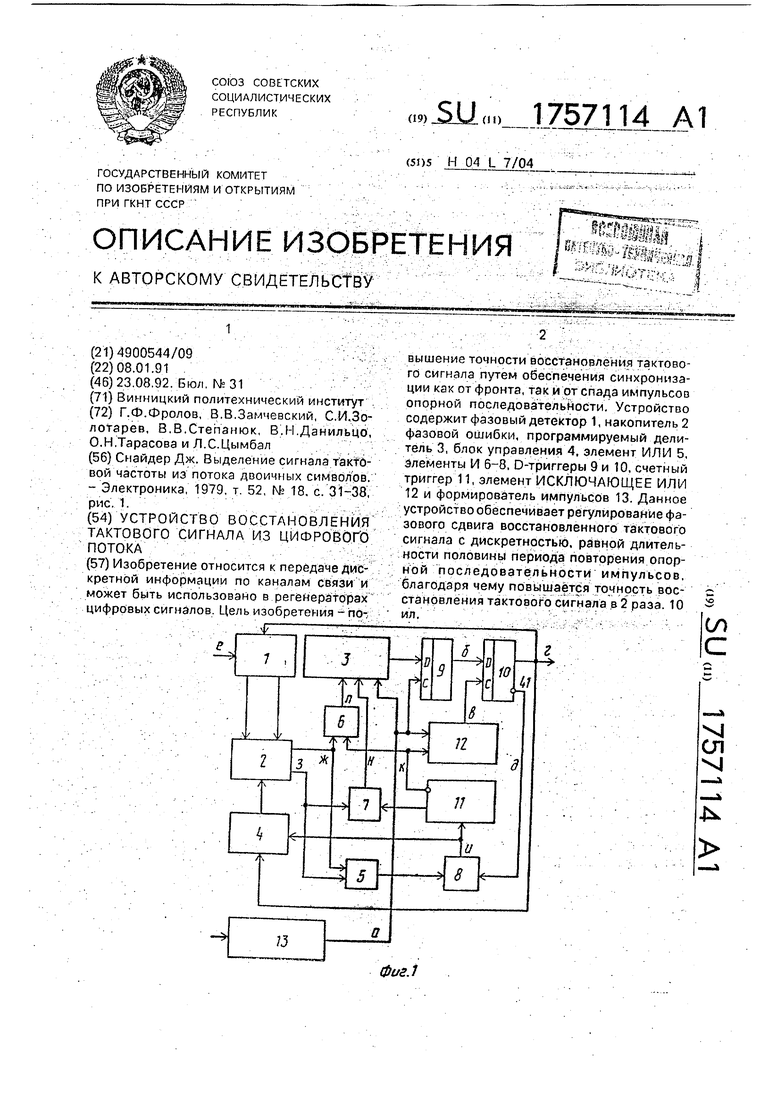

На фиг. 1 представлена структурная электрическая схема устройства восстановления тактового сигнала из цифрового потока; на фиг. 2-6 - варианты выполнения фазового детектора, накопителя фазовой ошибки, программируемого делителя, блока управления и формирователя импульсов; на фиг. 7-10 - временные диаграммы работы устройства.

Устройство содержит фазовый детектор

I,накопитель 2 фазовой ошибки, программируемый делитель 3, блок 4 управления, элемент ИЛИ 5, элементы И 6--8, первый м второй D-триггеры 9 и 10, счетный триггер

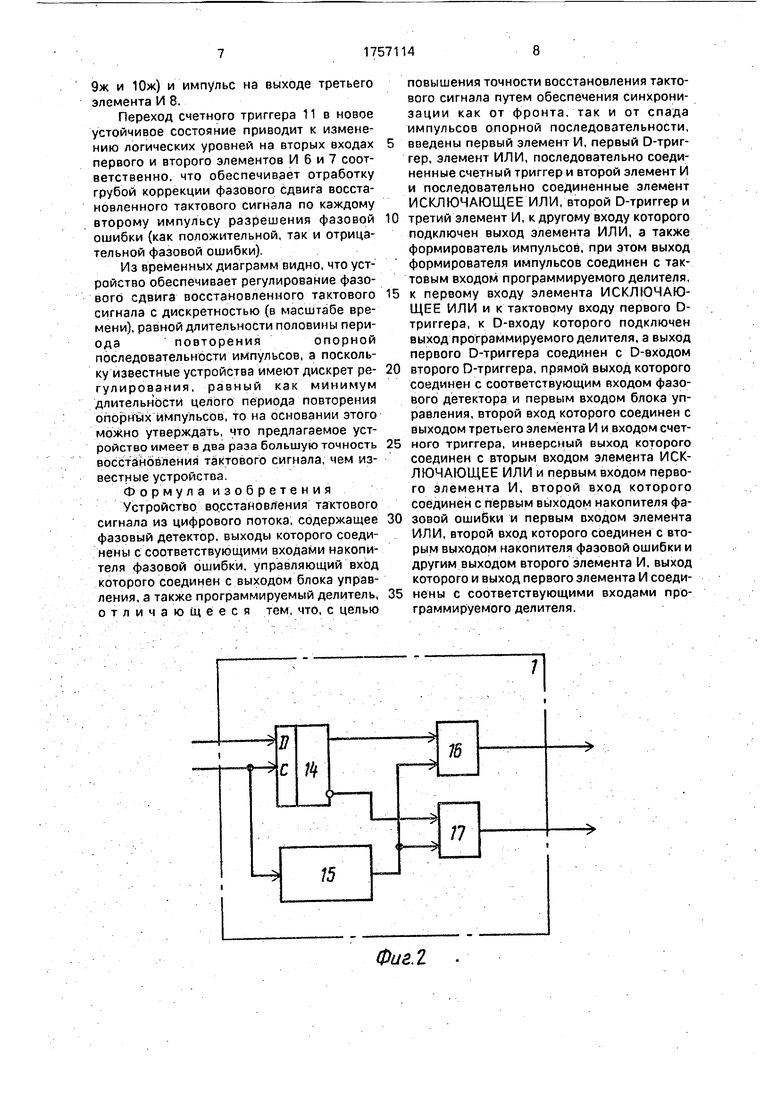

II,элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.12 и формирователь 13 импульсов. Причем в состав фазового детектора 1 входят D-триггер 14, элемент 15 задержки и элементы И 16 и

17. В состав накопителя 2 фазовой ошибки входят счетчики 18 и 19, элемент НЕ 20, формирователь 21 коротки/ импульсов и элементы И 22 и 23. В состав программируемого делителя 3 входят элементы ИЛИ 24 и 25, элементы И 26 и 27, элемент НЕ 28, триггер 29, элемент 30 задержки и счетчик 31. В состав блока управления входят счетчики 32 и 33 и переключатель 34. В состав формирователя входят одновибратор 35. конденсатор 36 и управляемый резистор 37.

Устройство работает следующим обра- зом.

На вход устройства от внешнего генератора поступает последовательность опорных импульсов с частотой повторения ton, a N раз превышающей номинальное значе- ние тактовой частоты fT:

fon-Nfr.

где N - средний коэффициент деления программируемого делителя 3.

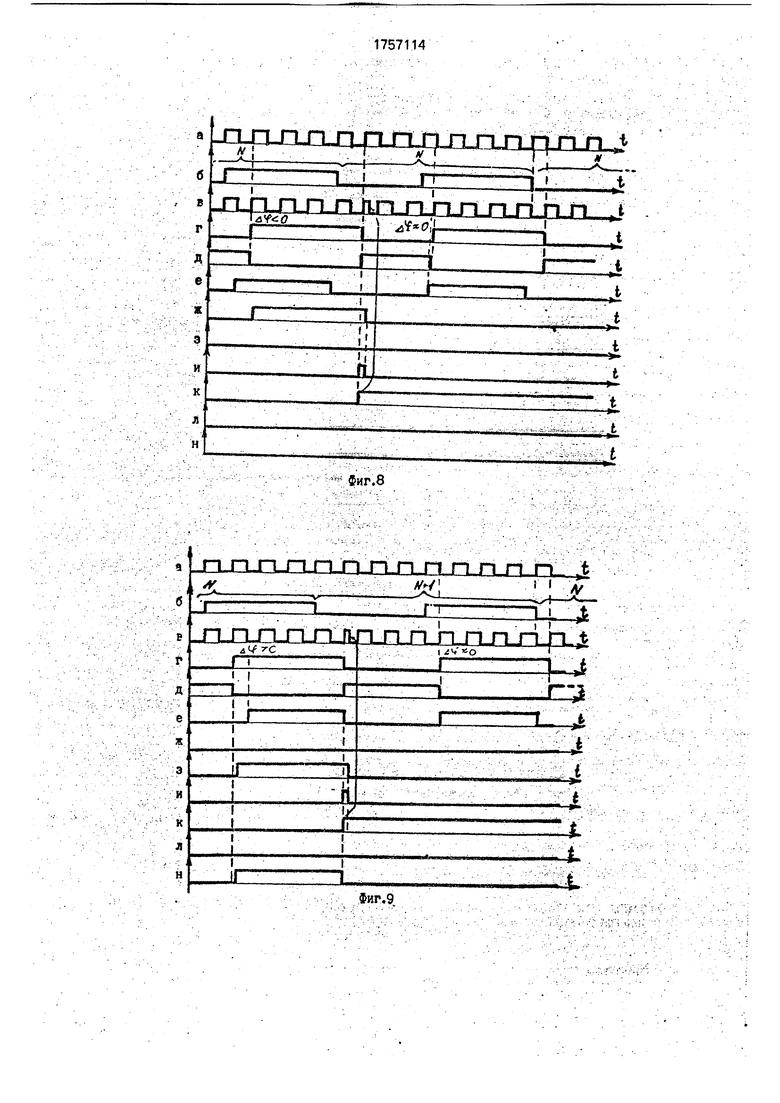

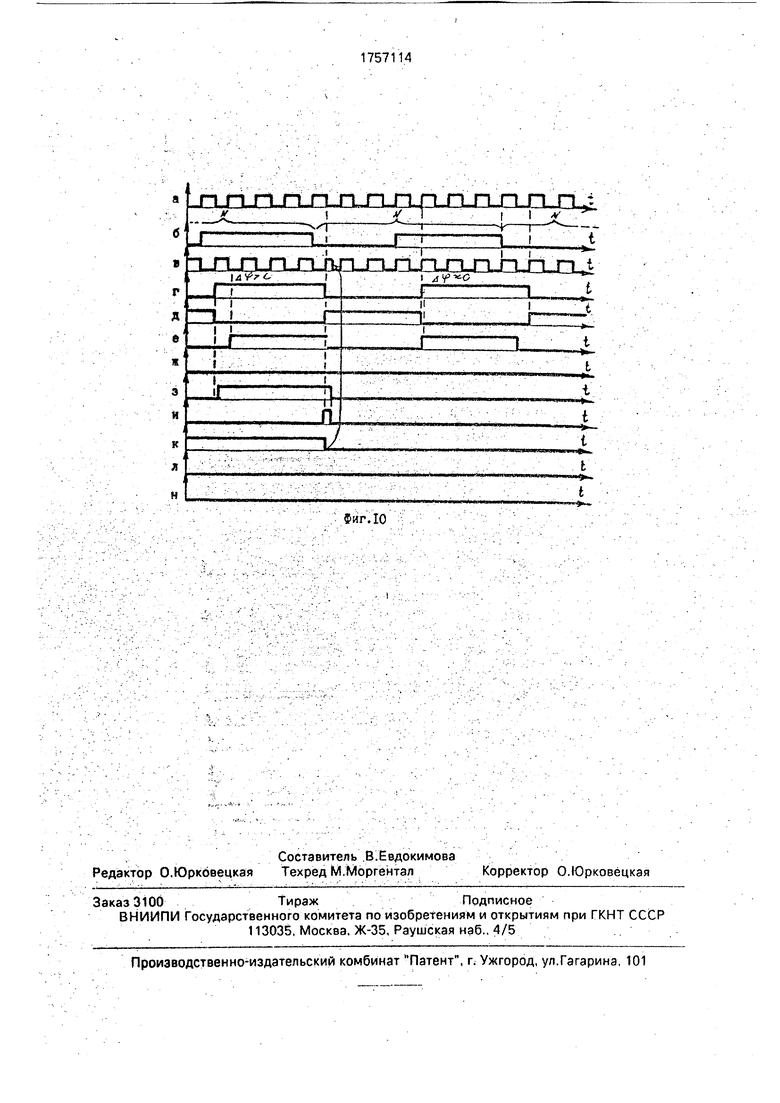

Формирователь 13 импульсов формиру- ет оптимальную скважность опорных импульсов, равную двум (фиг. 7а-10а). (Сформированная последовательность опорных импульсов тактирует программируемый делитель 3 и первый 9 и второй 10 D-триггеры, причем так как первый D-триг- гер 9 тактруется фронтом опорных импульсов, то на его выходе вырабатывается импульсная последовательность сигнала тактовой частоты, синхронная с положительным перепадом опорных импульсов (фиг. 76-106). Второй D-триггер 10 осуществляет точную коррекцию фазового сдвига сигнала тактовой частоты, так как в отличие от первого D-триггера 9 этот триггер может тактироваться как прямой, так и инвертированной последовательностью опорных импульсов, поступающей с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 (фиг. 7в-10в), используемого в качестве управляемого по первому входу (фиг, 7к-10к) инвертора-повторителя. В результате на выходе второго D-триггера 10 вырабатывается импульсная последовательность тактовой частоты, синхронная с положительным или с отрицатель- нымперепадомимпульсов

отформированной опорной последовательности, т.е. производится точная коррекция фазового сдвига восстановленного тактового сигнала (фиг. 7г-10г). Однако коррекция фазового сдвига тактового сигнала исключительно посредством переключения фронта тактирования второго D-триггера 10 не обеспечивает изменение фазового состояния тактового сигнала в диапазоне фазовых сдвигов 0-±2я рад, поэтому в устройстве используется грубая коррекция фазового сдвига тактового сигнала с помощью программируемого делителя 3, коэффициент деления Nm которого при наличии на первом входе импульса разрешения счета с суммированием увеличивается на единицу (N+1), причем только в одном цикле счета, затем устанавливается средний коэффициент деления N, а при наличии на втором входе импульса разрешения счета с вычитанием коэффициент деления в одном цикле счета уменьшается на единицу (N-1) с последующим возвратом к N.

Процесс авторегулирования фазового сдвига восстановления тактового сигнала протекает следующим образом.

Фазовый детектор 1 по приходу каждого импульса цифрового потока (фиг. 7е-10е) вырабатывает либо импульс положительной фазовой ошибки на втором выходе (если ЁОС становленный тактовый сигнал опережает по фазе сигнал цифрового потока, т.е. A(f 0), либо импульс отрицательной фа- зовой ошибки на первом выходе (если восстановленный тактовый сигнал отстает от сигнала цифрового потока, т.е. ). Накопитель 2 фазовой ошибки по каждому импульсу запроса фазовой коррекции, поступающему с блока 4 управления, в зависимости от знака усредненной фазовой ошибки вырабатывает либо импульс разрешения коррекции положительной фазовой ошибки на втором выходе, либо импульс

разрешения коррекции отрицательной фазовой ошибки на первом выходе. В случае нулевого значения усредненной фазовой ошибки на выходах накопителя 2 фазовой ошибки импульсы отсутствуют и, следова- тельно, коррекция фазы тактового сигнала не производится,

В случае, если , накопитель 2 фазовой ошибки вырабатывает на первом выходе импульс разрешения коррекции от- рицательной фазовой ошибки (фиг. 7ж и 8ж), который при нулевом состоянии счетного триггера 11, т.е. при наличии логической единицы на его инверсном выходе (фиг. 7к), вызывает появление на выходе первого эле- мента А 6 импульса разрешения счета с вычитанием (фиг. 7л), поступающего на первый вход программируемого делителя 3, что вызывает уменьшение его коэффициента деления N з первом цикле счета на единицу, т.е. производится грубая коррекция фазового сдвига тактового сигнала (фиг. 76),

При единичном состоянии счетного триггера 11, т.е. при наличии уровня логического нуля на его инверсном выходе (фиг. 8к), на выходе первого элемента И 6 импульс разрешения счета с вычитанием не появляется (фиг. 8л) и, следовательно, коэффициент деления N программируемого делителя 3 не изменяется (фиг. 86)

Импульс разрешения коррекции отрицательной фазовой ошибки через элемент ИЛИ 5 поступает на второй вход третьего элемента И 8, на выходе которого по приходу на первый вход уровня логической едини- цы инвертированного тактового сигнала (фиг. 7д и 8д) вырабатывается импульс (фиг. 7и, 8и), переключающий в новое устойчивое состояние счетный триггер 11, инверсный выход которого, изменяя свой логический уровень (фиг. 7к и 8к). меняет режим работы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12, на выходе которого сформированная опорная последовательность импульсов либо инвертируется, если до этою она повторя- лась (фиг. 8в), либо повторяется, если до этого она инвертировалась (фиг. 7в). Обработанная таким образом последовательность опорных импульсов тактирует по С-входу второй D-триггер 10. обеспечивая точную коррекцию фазового сдвига восстановленного тактового сигнала до минимйль- ной величины фазовой ошибки Ду О (фиг. 7г и 8г).

Импульс, вырабатываемый на выходе третьего элемента И 8 (фиг 7и, 8и), используется также для сброса счетчиков блока 4 управления, в результате чего последовательно блокируются импульс запроса фазовой коррекции, импульс разрешения коррекции отрицательной фазовой ошибки на перзом выходе накопителя 2 фазовой ошибки (фиг. 7ж и 8ж) и импульс ча выходе третьего элемента И 8.

В случае, если Д 0, накопитель 2 фазовой ошибки вырабатывает на втором выходе импульс разрешения коррекции положительной фазовой ошибки (фиг 9з и Юз), который при единичном состоянии счетного триггера 11, т.е. при наличии логического нуля на его инверсном вы х оде (фиг. 9к), вызывает появление на выходе второго элемента И 7 импульса разрешения счета г суммированием (фиг. 9н), поступа-ищст) на второй вход, что вызывает увеличение его коэффициента деления N в первом цикле счета на единицу, т.е. производится грубая коррекция фазового сдвига тактового сигнала (фиг, 96).

При нулевом состоянии счетного триггера И, т.е. при наличии уровняя логической единицы на его инверсном выходе (фиг 10к), на выходе второго элемента И 7 импульс разрешения счета с суммированием не появляется (фиг. Юн), а следовательно, коэффициент деления N программируемого делителя 3 не изменяется (фиг. 106).

Импульс разрешения коррекции положительной фазовой ошибки через элемент ИЛИ 5 поступает на второй вход тре ьего элемента И 8, на выходе которого по приходу на первый вход уровня логической единицы инвертированного тактового сигнала (фиг. 9д и 10д) вырабатывается импульс (фиг 9и, 10и), переключающий в новое устойчивое состояние счетный триггер 11, на инверсном выходе которого логический уровень изменяется на противоположный (фиг. 9к и 10к), в результате чего м еняется режим работы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12. на выходе которого отформированная последовательность опорных импульсов либо инвертируется, если до этого она повторялась (фиг. 9в), либо повторяется, если до этого она инвертировалась (фиг. Юв). Эта последовательность тактирует второй D- триггер 10, обеспечивая точную коррекцию фазового сдвига восстановленного тактового сигнала до минимальной величины фазовой ошибки А р 0 (фиг. 9г и 10r). Импульс, вырабатываемый на входе третьего элемента И 8 (фиг. 9и, 10и), сбрасывает счетчики блока 4 управления, вследствие этого блокируются импульс запроса фазовой коррекции, импульс разрешения коррекции положительной фазовой ошибки на втором выходе накопителя 2 фазовой ошибки (фиг.

9ж и Юж) и импульс на выходе третьего элемента И 8.

Переход счетного триггера 11 в новое устойчивое состояние приводит к изменению логических уровней на вторых входах первого и второго элементов И 6 и 7 соответственно, что обеспечивает отработку грубой коррекции фазового сдвига восстановленного тактового сигнала по каждому второму импульсу разрешения фазовой ошибки (как положительной, так и отрицательной фазовой ошибки).

Из временных диаграмм видно, что устройство обеспечивает регулирование фазового сдвига восстановленного тактового сигнала с дискретностью (в масштабе времени), равной длительности половины периодаповторенияопорнойпоследовательности импульсов, а поскольку известные устройства имеют дискрет ре- гулирования, равный как минимум длительности целого периода повторения опорных импульсов, то на основании этого можно утверждать, что предлагаемое устройство имеет в два раза большую точность восстановления тактового сигнала, чем известные устройства.

Формула изобретения

Устройство восстановления тактового сигнала из цифрового потока, содержащее фазовый детектор, выходы которого соединены с соответствующими входами накопителя фазовой ошибки, управляющий вход которого соединен с выходом блока управления, а также программируемый делитель, отличающееся тем, что, с целью

повышения точности восстановления тактового сигнала путем обеспечения синхронизации как от фронта, так и от спада импульсов опорной последовательности, введены первый элемент И, первый D-триг- гер, элемент ИЛИ, последовательно соединенные счетный триггер и второй элемент И и последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй D-триггер и третий элемент И, к другому входу которого подключен выход элемента ИЛИ, а также формирователь импульсов, при этом выход формирователя импульсов соединен с тактовым входом программируемого делителя, к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к тактовому входу первого D- триггера, к D-входу которого подключен выход программируемого делителя, а выход первого D-триггера соединен с D-входом второго D-триггера, прямой выход которого соединен с соответствующим входом фазового детектора и первым входом блока управления, второй вход которого соединен с выходом третьего элемента И и входом счетного триггера, инверсный выход которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом первого элемента И, второй вход которого соединен с первым выходом накопителя фазовой ошибки и первым входом элемента ИЛИ, второй вход которого соединен с вторым выходом накопителя фазовой ошибки и другим выходом второго элемента И, выход которого и выход первого элемента И соединены с соответствующими входами программируемого делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов с относительной фазовой модуляцией | 1989 |

|

SU1635278A1 |

| Устройство для поверки преобразователей фаза-код | 1990 |

|

SU1774298A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство для синхронизации воспроизводимой информации | 1977 |

|

SU690552A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Цифровой управляемый генератор | 1989 |

|

SU1748247A1 |

| Устройство для информации с магнитной ленты (его варианты) | 1982 |

|

SU1301326A3 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство цифровой фазовой автоподстройки частоты | 1990 |

|

SU1732466A1 |

Изобретение относится к передаче дискретной информации по каналам связи и может быть использовано в регенераторах цифровых сигналов Цель изобретения - повышение точности восстановления тактового сигнала путем обеспечения синхронизации как от фронта, так и от спада импульсов опорной последовательности. Устройство содержит фазовый детектор 1, накопитель 2 фазовой ошибки, программируемый делитель 3, блок управления 4, элемент ИЛИ 5, Элементы И 6-8. D-триггеры 9 и 10, счетный триггер 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12 и формирователь импульсов 13. Данное устройство обеспечивает регулирование фазового сдвига восстановленного тактового сигнала с дискретностью, равной длительности половины периода повторения опорной последовательности импульсов, благодаря чему повышается точность восстановления тактового сигнала в 2 раза. 10 ил. сл с

Я

и

Ъ

15

-

76

Фиг.2

HUSH

б

в г д е

ж

3

и к

л

Фиг. 5

Фиг.10

| Снайдер Дж | |||

| Выделение сигнала тактовой частоты из потока двоичных символов | |||

| - Электроника, 1979, т 52, № 18, с | |||

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-08-23—Публикация

1991-01-08—Подача