Изобретение относится к области электротехники, а именно к преобразовательной технике, и может быть использовано при проектировании источников вторичного электропитания, обладающих высокой надежностью и экономичностью.

Целью изобретения является повышение надежности преобразователя, умень- шение динамических потерь в силовых транзисторах и уменьшение излучения электромагнитных помех.f

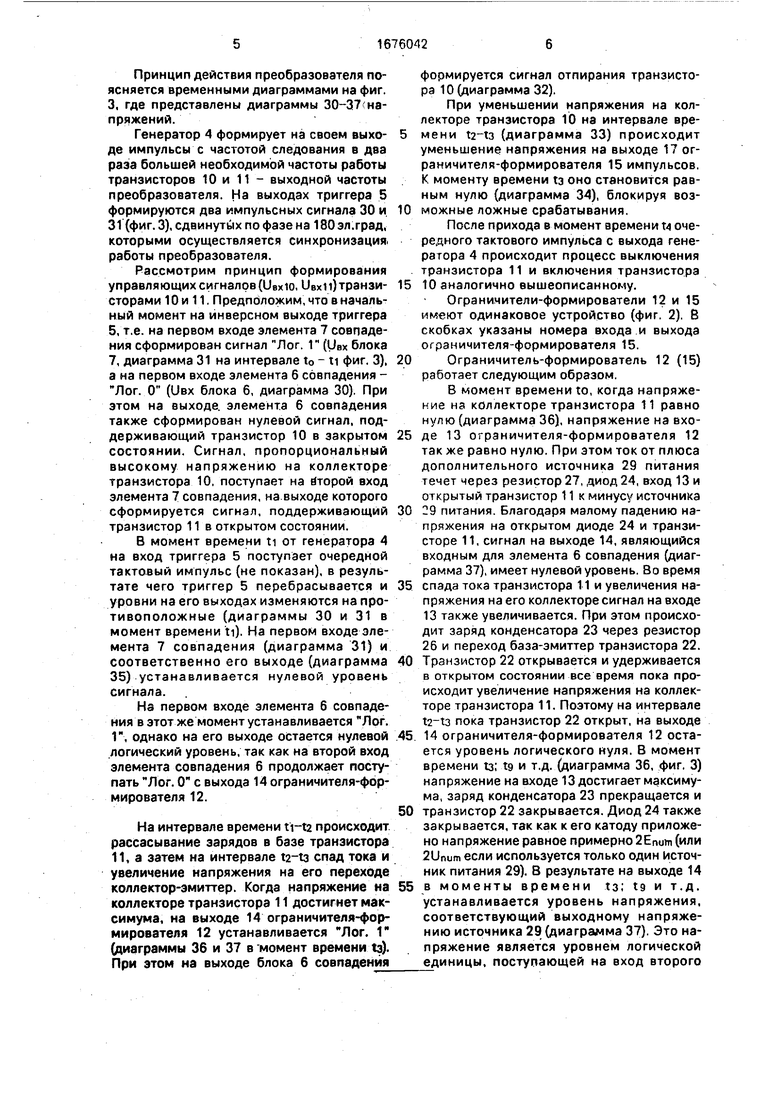

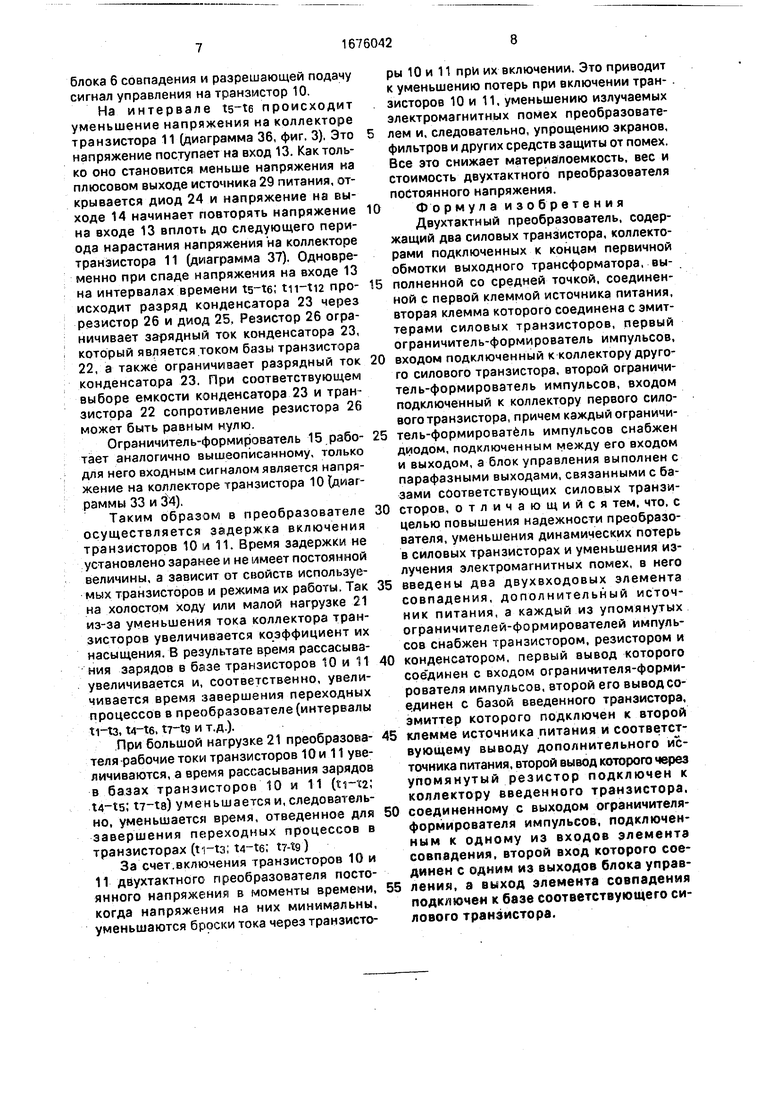

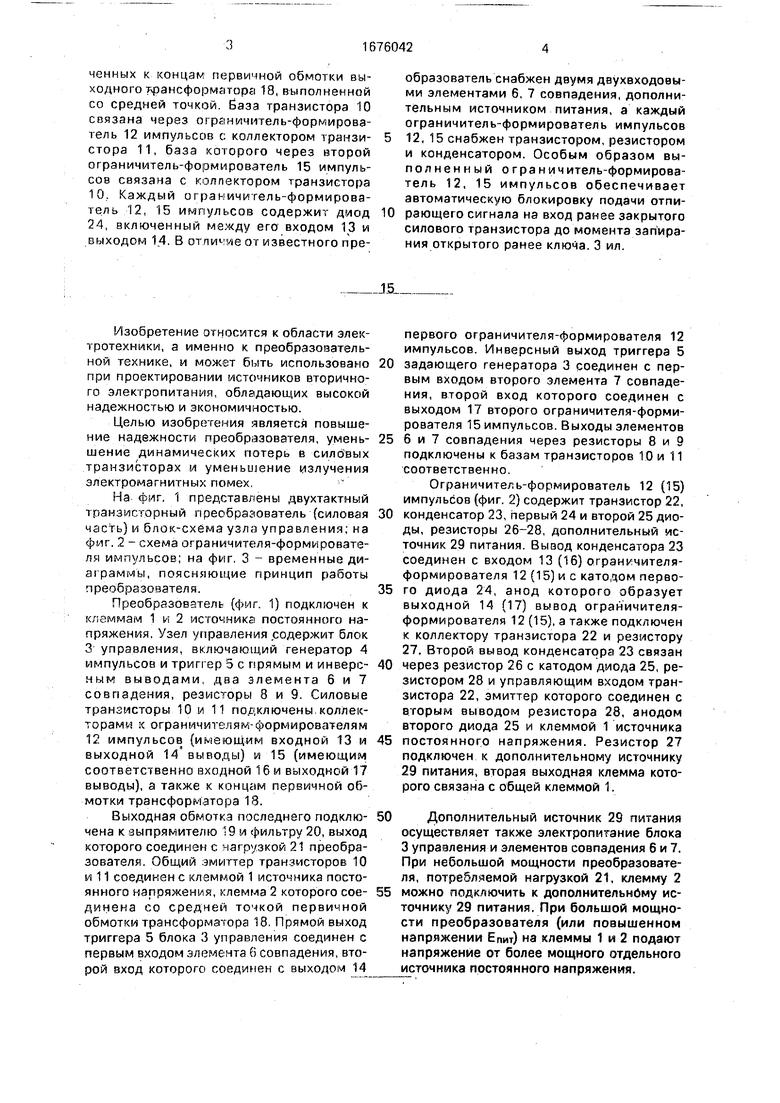

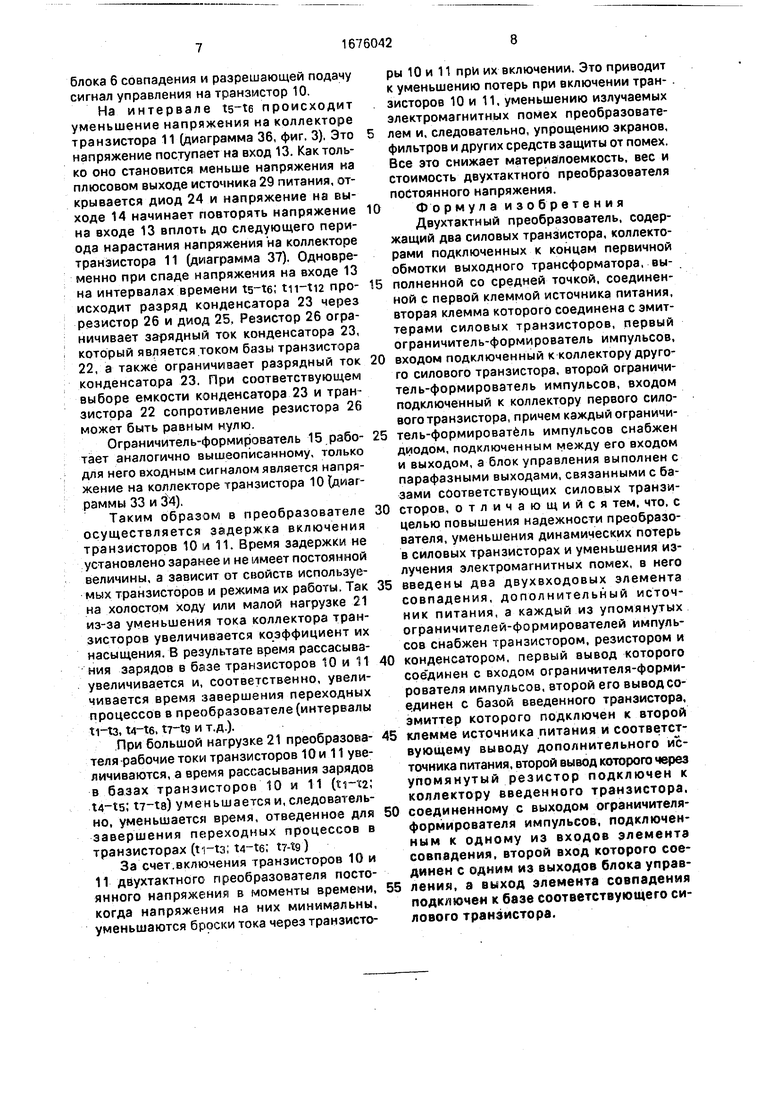

На фиг, 1 представлены двухтактный транзисторный преобразователь (силовая часть) и блок-схема узла управления; на фиг, 2 - схема ограничителя-формирователя импульсов; на фиг. 3 - временные диаграммы, поясняющие принцип работы преобразователя.

Преобразователь (фиг. 1} подключен к клеммам 1 и 2 источника постоянного напряжения. Узел управления содержит блок 3 управления, включающий генератор 4 импульсов и триггер 5 с прямым и инверс- ньш выводами, два элемента 6 и 7 совпадения, резисторы 8 и 9. Силовые транзисторы 10 и 11 подключены коллекторами к ограничителям-формирователям 12 импульсов (имеющим входной 13 и выходной 14° выводы) и 15 (имеющим соответственно входной 16 и выходной 17 выводы), а также к концам первичной обмотки трансформатора 18.

Выходная обмотка последнего подклю- чена к выпрямителю 19 и фильтру 20, выход которого соединен с нагрузкой 21 преобразователя. Общий эмиттер транзисторов 10 и 11 соединен с клеммой 1 источника постоянного напряжения, клемма 2 которого сое- динена со средней точкой первичной обмотки трансформатора 18, Прямой выход триггера 5 блока 3 управления соединен с первым входом элемента 6 совпадения, второй вход которого соединен с выходом 14

первого ограничителя-формирователя 12 импульсов. Инверсный выход триггера 5 задающего генератора 3 соединен с первым входом второго элемента 7 совпадения, второй вход которого соединен с выходом 17 второго ограничителя-формирователя 15 импульсов. Выходы элементов 6 и 7 совпадения через резисторы 8 и 9 подключены к базам транзисторов 10 и 11 соответственно.

Ограничитель-формирователь 12 (15) импульсов (фиг. 2) содержит транзистор 22, конденсатор 23, первый 24 и второй 25 диоды, резисторы 26-28, дополнительный источник 29 питания. Вывод конденсатора 23 соединен с входом 13(16) ограничителя- формирователя 12 (15) и с катодом первого диода 24, анод которого образует выходной 14 (17) вывод ограничителя- формирователя 12 (15), а также подключен к коллектору транзистора 22 и резистору 27. Второй вывод конденсатора 23 связан через резистор 26 с катодом диода 25, резистором 28 и управляющим входом транзистора 22, эмиттер которого соединен с вторым выводом резистора 28, анодом второго диода 25 и клеммой 1 источника постоянного напряжения. Резистор 27 подключен к дополнительному источнику 29 питания, вторая выходная клемма которого связана с общей клеммой 1.

Дополнительный источник 29 питания осуществляет также электропитание блока 3 управления и элементов совпадения 6 и 7. При небольшой мощности преобразователя, потребляемой нагрузкой 21. клемму 2 можно подключить к дополнительному источнику 29 питания. При большой мощности преобразователя (или повышенном напряжении Епит) на клеммы 1 и 2 подают напряжение от более мощного отдельного источника постоянного напряжения.

Принцип действия преобразователя поясняется временными диаграммами на фиг. 3, где представлены диаграммы 30-37 напряжений.

Генератор 4 формирует на своем выходе импульсы с частотой следования в два раза большей необходимой частоты работы транзисторов 10 и 11 - выходной частоты преобразователя. На выходах триггера 5 формируются два импульсных сигнала 30 и 31 (фиг. 3), сдвинутых по фазе на 180 эл.град, которыми осуществляется синхронизация работы преобразователя.

Рассмотрим принцип формирования управляющих сигналов (Uexio, ивхп)трзнзи- сторами 10 и 11. Предположим, что в начальный момент на инверсном выходе триггера 5, т.е. на первом входе элемента 7 совпадения сформирован сигнал Лог. 1 (Квх блока 7, диаграмма 31 на интервале to - ti фиг. 3), а на первом входе элемента 6 совпадения - Лог. О (DBX блока 6, диаграмма 30). При этом на выходе, элемента 6 совпадения также сформирован нулевой сигнал, поддерживающий транзистор 10 в закрытом состоянии. Сигнал, пропорциональный высокому напряжению на коллекторе транзистора 10, поступает на йторой вход элемента 7 совпадения, на выходе которого сформируется сигнал, поддерживающий транзистор 11 в открытом состоянии.

В момент времени ti от генератора 4 на вход триггера 5 поступает очередной тактовый импульс (не показан), в результате чего триггер 5 перебрасывается и уровни на его выходах изменяются на противоположные (диаграммы 30 и 31 в момент времени ti). На первом входе элемента 7 совпадения (диаграмма 31) и соответственно его выходе (диаграмма 35) устанавливается нулевой уровень сигнала.

На первом входе элемента 6 совпадения в этот же момент устанавливается Лог. 1, однако на его выходе остается нулевой логический уровень, так как на второй вход элемента совпадения 6 продолжает поступать Лог. О с выхода 14 ограничителя-формирователя 12.

На интервале времени n-t2 происходит рассасывание зарядов в базе транзистора 11, а затем на интервале t2-ta спад тока и увеличение напряжения на его переходе коллектор-эмиттер. Когда напряжение на коллекторе транзистора 11 достигнет максимума, на выходе 14 ограничителя-формирователя 12 устанавливается Лог. Г (диаграммы 36 и 37 в момент времени ta). При этом на выходе блока 6 совпадения

формируется сигнал отпирания транзистора 10 (диаграмма 32).

При уменьшении напряжения на коллекторе транзистора 10 на интервале времени (диаграмма 33) происходит уменьшение напряжения на выходе 17 ограничителя-формирователя 15 импульсов. К моменту времени ta оно становится равным нулю (диаграмма 34), блокируя воз0 можные ложные срабатывания.

После прихода в момент времени ГА очередного тактового импульса с выхода генератора 4 происходит процесс выключения транзистора 11 и включения транзистора

5 10 аналогично вышеописанному.

Ограничители-формирователи 12 и 15 имеют одинаковое устройство (фиг. 2). В скобках указаны номера входа и выхода ограничителя-формирователя 15.

0 Ограничитель-формирователь 12 (15) работает следующим образом.

В момент времени to, когда напряжение на коллекторе транзистора 11 равно нулю (диаграмма 36), напряжение на вхо5 де 13 ограничителя-формирователя 12 так же равно нулю. При этом ток от плюса дополнительного источника 29 питания течет через резистор 27, диод 24, вход 13 и открытый транзистор 11 к минусу источника

0 29 питания. Благодаря малому падению напряжения на открытом диоде 24 и транзисторе 11, сигнал на выходе 14, являющийся входным для элемента 6 совпадения (диаграмма 37), имеет нулевой уровень. Во время

5 спада тока транзистора 11 и увеличения напряжения на его коллекторе сигнал на входе 13 также увеличивается. При этом происходит заряд конденсатора 23 через резистор 26 и переход база-эмиттер транзистора 22.

0 Транзистор 22 открывается и удерживается в открытом состоянии все время пока происходит увеличение напряжения на коллекторе транзистора 11. Поэтому на интервале ta-t3 пока транзистор 22 открыт, на выходе

5 14 ограничителя-формирователя 12 остается уровень логического нуля. В момент времени ta; tg и т.д. (диаграмма 36, фиг. 3) напряжение на входе 13 достигает максимума, заряд конденсатора 23 прекращается и

0 транзистор 22 закрывается. Диод 24 также закрывается, так как к его катоду приложено напряжение равное примерно 2Enum (или 2Unum если используется только один источник питания 29). В результате на выходе 14

5 в моменты времени ta; tg и т.д. устанавливается уровень напряжения, соответствующий выходному напряжению источника 29 (диаграмма 37). Это напряжение является уровнем логической единицы, поступающей на вход второго

блока 6 совпадения и разрешающей подачу сигнал управления на транзистор 10.

На интервале ts-te происходит уменьшение напряжения на коллекторе транзистора 11 (диаграмма 36, фиг. 3). Это напряжение поступает на вход 13. Как только оно становится меньше напряжения на плюсовом выходе источника 29 питания, открывается диод 24 и напряжение на выходе 14 начинает повторять напряжение на входе 13 вплоть до следующего периода нарастания напряжения на коллекторе транзистора 11 (диаграмма 37). Одновременно при спаде напряжения на входе 13 на интервалах времени ts-te; tn-ti2 происходит разряд конденсатора 23 через резистор 26 и диод 25, Резистор 26 ограничивает зарядный ток конденсатора 23, который является током базы транзистора 22, а также ограничивает разрядный ток конденсатора 23. При соответствующем выборе емкости конденсатора 23 и транзистора 22 сопротивление резистора 26 может быть равным нулю.

Ограничитель-формирователь 15 работает аналогично вышеописанному, только для него входным сигналом является напряжение на коллекторе транзистора 10 (диаграммы 33 и 34).

Таким образом в преобразователе осуществляется задержка включения транзисторов 10 и 11. Время задержки не установлено заранее и не имеет постоянной величины, а зависит от свойств используемых транзисторов и режима их работы. Так на холостом ходу или малой нагрузке 21 из-за уменьшения тока коллектора транзисторов увеличивается коэффициент их насыщения. В результате время рассасывания зарядов в базе транзисторов 10 и 11 увеличивается и, соответственно, увеличивается время завершения переходных процессов в преобразователе(интервалы tl-ta, t4-te, tr-tg и т.д.).

При большой нагрузке 21 преобразователя рабочие токи транзисторов 10 и 11 увеличиваются, а время рассасывания зарядов в базах транзисторов 10 и 11 (ti-tz; t4-ts; t7-te) уменьшается и, следовательно, уменьшается время, отведенное для завершения переходных процессов в транзисторах (n-ta; t4-te; ty-tg)

За счет включения транзисторов 10 и 11 двухтактного преобразователя постоянного напряжения в моменты времени, когда напряжения на них минимальны, уменьшаются броски тока через транзисторы 10 и 11 при их включении. Это приводит к уменьшению потерь при включении транзисторов 10 и 11, уменьшению излучаемых электромагнитных помех преобразователем и, следовательно, упрощению экранов, фильтров и других средств защиты от помех. Все это снижает материалоемкость, вес и стоимость двухтактного преобразователя постоянного напряжения.

Ф о р му л а и з о б р е т е н и я

Двухтактный преобразователь, содержащий два силовых транзистора, коллекторами подключенных к концам первичной обмотки выходного трансформатора, выполненной со средней точкой, соединенной с первой клеммой источника питания, вторая клемма которого соединена с эмиттерами силовых транзисторов, первый ограничитель-формирователь импульсов,

входом подключенный к коллектору другого силового транзистора, второй ограничитель-формирователь импульсов, входом подключенный к коллектору первого силового транзистора, причем каждый ограничитель-формироватёль импульсов снабжен диодом, подключенным между его входом и выходом, а блок управления выполнен с парафазными выходами, связанными с базами соответствующих силовых транзисторов, отличающийся тем, что, с целью повышения надежности преобразователя, уменьшения динамических потерь в силовых транзисторах и уменьшения излучения электромагнитных помех, в него

введены два двухвходовых элемента совпадения, дополнительный источник питания, а каждый из упомянутых ограничителей-формирователей импульсов снабжен транзистором, резистором и

конденсатором, первый вывод которого сое динен с входом ограничителя-формирователя импульсов, второй его вывод соединен с базой введенного транзистора, эмиттер которого подключен к второй

клемме источника питания и соответствующему выводу дополнительного источника питания, второй вывод которого через упомянутый резистор подключен к коллектору введенного транзистора.

соединенному с выходом ограничителя- формирователя импульсов, подключенным к одному из входов элемента совпадения, второй вход которого соединен с одним из выходов блока управления, а выход элемента совпадения подключен к базе соответствующего силового транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный инвертор | 1990 |

|

SU1746502A1 |

| Преобразователь постоянного напряжения | 1988 |

|

SU1539925A1 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1988 |

|

SU1749996A1 |

| ОКТАН-КОРРЕКТОР | 1991 |

|

RU2044154C1 |

| ОКТАН-КОРРЕКТОР | 1990 |

|

RU2030617C1 |

| УСТРОЙСТВО ЭЛЕКТРОННОГО ЗАЖИГАНИЯ | 1995 |

|

RU2117817C1 |

| Инвертор со ступенчатой квазисинусоидальной формой выходного напряжения | 1989 |

|

SU1677831A1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1721749A1 |

| Преобразователь постоянного напряжения | 1989 |

|

SU1700727A1 |

| Ограничитель пускового тока инвертора | 1988 |

|

SU1534682A1 |

Изобретение относится к электротехнике и может быть использовано при проектировании источников вторичного электропитания, преобразующих постоянное напряжение преимущественно в постоянное, обладающих высокой надежностью и экономичностью. Целью изобретения является повышение надежности преобразователя, уменьшение динамических .потерь и уменьшение излучения электромагнитных помех. Двухтактный преобразователь содержит два силовых транзистора 10, 11, коллекторами подклю

| Ромаш Э.М., Драбович Ю.И., Юрченко Н.Н., Шевченко П.И | |||

| Высокочастотные транзисторные преобразователи | |||

| - М.: Радио и связь, 1988 | |||

| с | |||

| Ударно-вращательная врубовая машина | 1922 |

|

SU126A1 |

| Преобразователь переменного напряжения в переменное | 1975 |

|

SU570163A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1991-09-07—Публикация

1989-05-26—Подача