о VJ

XI

О

о о

и 18 для подключения образцовых источников напряжения, два триггера 19 и 20, дешифратор 21, генератор импульсов 22, делитель частоты 23, два элемента И 24 и 28, два счетчика 25 и 29, два регистра 26 и 31,

умножитель частоты 27 и постоянное запоминающее устройство 30. Высокая точность измерения достигается за счет того, что величина емкости измеряется при почти нулевом токе через сопротивление утечки. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электромагнитный интегрирующий толщиномер | 1986 |

|

SU1427165A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Цифровой электромагнитный толщиномер | 1986 |

|

SU1379606A1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Устройство для измерения постоянной времени | 1987 |

|

SU1504626A1 |

| Устройство для измерения отношения сопротивлений | 1988 |

|

SU1619195A1 |

| Цифровой электромагнитный толщиномер | 1988 |

|

SU1839228A1 |

| Устройство для контроля деградации МДП-структур | 1990 |

|

SU1783454A1 |

| Цифровой измеритель резистивных параметров кабеля | 1986 |

|

SU1406517A1 |

| Устройство для измерения сопротивления | 1984 |

|

SU1239608A1 |

Изобретение относится к электроизмерительной технике и может быть использовано при построении автоматических цифровых измерителей. Целью изобретения является повышение точности измерения и расширение функциональных возможностей путем измерения сопротивления утечки. Устройство содержит операционный усилитель 1, резисторы 2,5,7. клеммы 3 и 4 для подключения к источнику питания, ключи 6 и 10, клеммы 8 и 9 для подключения измеряемой емкости, четыре компаратора 11,12,13 и 14, клеммы 15,16,17

Изобретение относится к измерительной технике и может быть использовано при построении автоматических цифровых измерителей.

Цель изобретения - повышение точности измерения и расширение функциональных возможностей путем измерения сопротивления утечки.

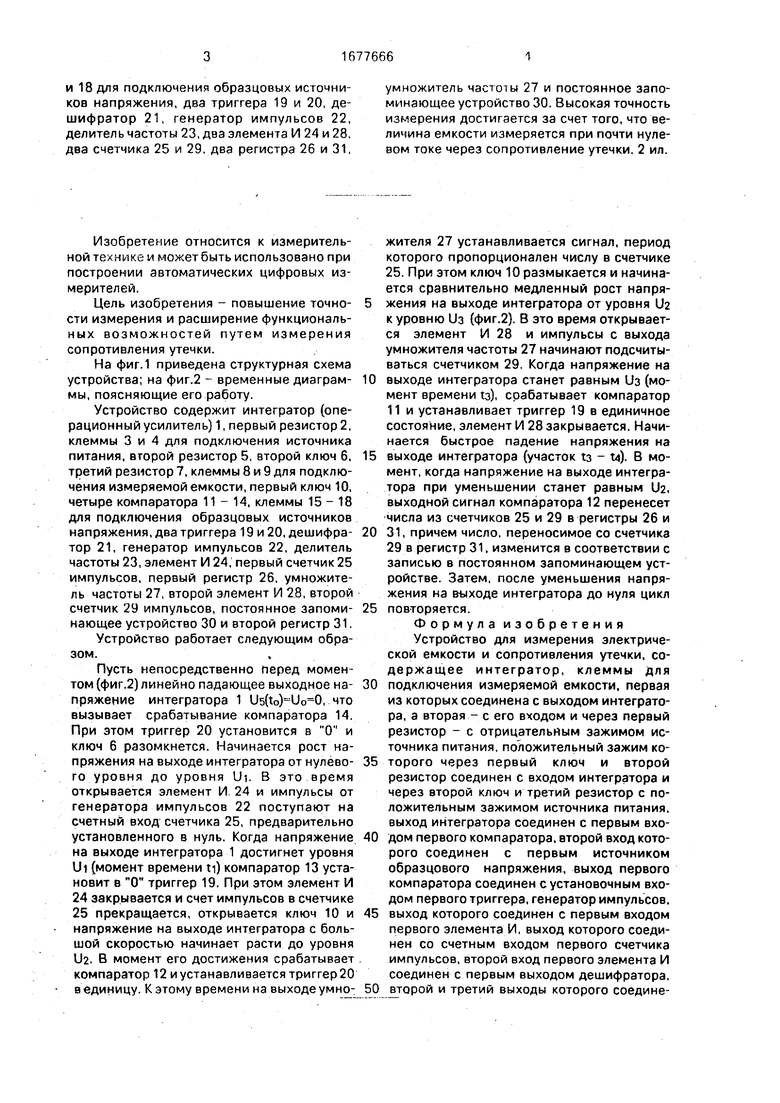

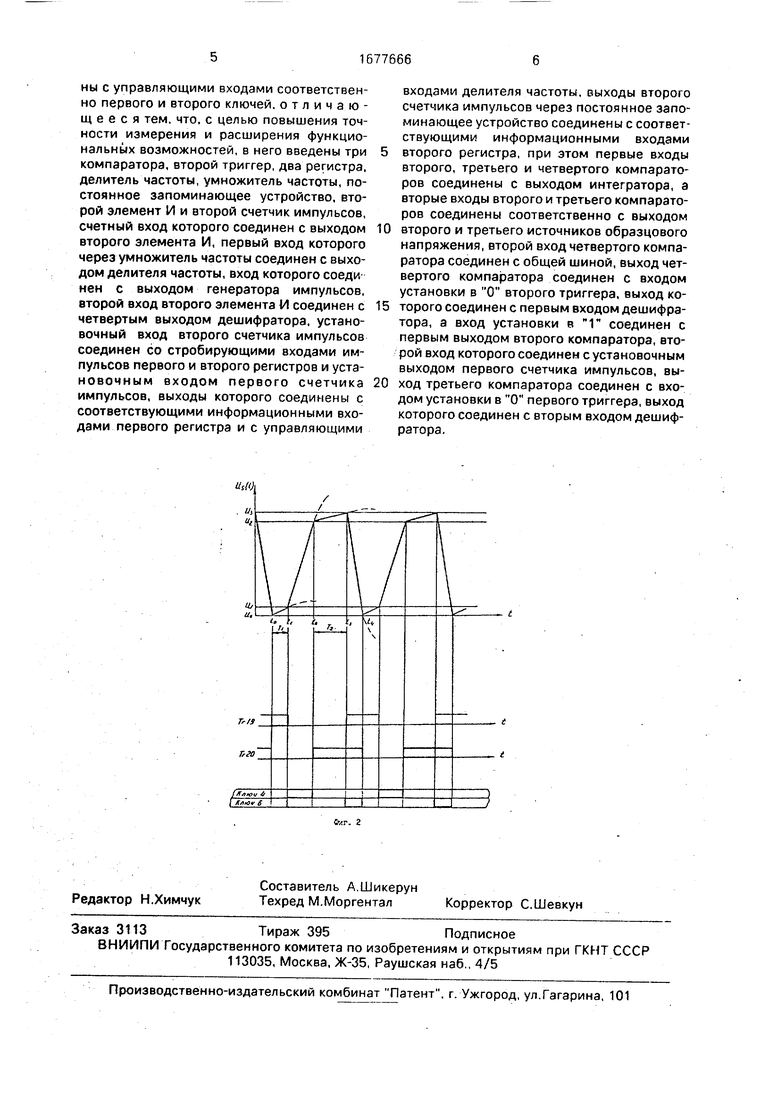

На фиг.1 приведена структурная схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство содержит интегратор (операционный усилитель) 1, первый резистор 2, клеммы 3 и 4 для подключения источника питания, второй резистор 5, второй ключ 6, третий резистор 7, клеммы 8 и 9 для подключения измеряемой емкости, первый ключ 10, четыре компаратора 11-14, клеммы 15 - 18 для подключения образцовых источников напряжения, два триггера 19 и 20, дешифратор 21, генератор импульсов 22, делитель частоты 23, элемент И 24, первый счетчик 25 импульсов, первый регистр 26. умножитель частоты 27, второй элемент И 28, второй счетчик 29 импульсов, постоянное запоминающее устройство 30 и второй регистр 31.

Устройство работает следующим образом.

Пусть непосредственно перед моментом (фиг.2) линейно падающее выходное напряжение интегратора 1 U5(to), что вызывает срабатывание компаратора 14. При этом триггер 20 установится в О и ключ б разомкнется. Начинается рост напряжения на выходе интегратора от нулевого уровня до уровня Ui. В это время открывается элемент И 24 и импульсы от генератора импульсов 22 поступают на счетный вход счетчика 25, предварительно установленного в нуль. Когда напряжение на выходе интегратора 1 достигнет уровня Ui (момент времени ti) компаратор 13 установит в О триггер 19. При этом элемент И

24закрывается и счет импульсов в счетчике

25прекращается, открывается ключ 10 и напряжение на выходе интегратора с большой скоростью начинает расти до уровня U2. В момент его достижения срабатывает компаратор 12 и устанавливается триггер 20 в единицу. К этому времени на выходе умножителя 27 устанавливается сигнал, период которого пропорционален числу в счетчике 25. При этом ключ 10 размыкается и начинается сравнительно медленный рост напряжения на выходе интегратора от уровня U2 к уровню 11з (фиг.2). В это время открывается элемент И 28 и импульсы с выхода умножителя частоты 27 начинают подсчитываться счетчиком 29. Когда напряжение на

0 выходе интегратора станет равным Уз (момент времени ta), срабатывает компаратор 11 и устанавливает триггер 19 в единичное состояние, элемент И 28 закрывается. Начинается быстрое падение напряжения на

5 выходе интегратора (участок гз - ti). В момент, когда напряжение на выходе интегратора при уменьшении станет равным Ua, выходной сигнал компаратора 12 перенесет числа из счетчиков 25 и 29 в регистры 26 и

0 31, причем число, переносимое со счетчика 29 в регистр 31, изменится в соответствии с записью в постоянном запоминающем устройстве. Затем, после уменьшения напряжения на выходе интегратора до нуля цикл

5 повторяется.

Формула изобретения Устройство для измерения электрической емкости и сопротивления утечки, содержащее интегратор, клеммы для

0 подключения измеряемой емкости, первая из которых соединена с выходом интегратора, а вторая - с его входом и через первый резистор - с отрицательным зажимом источника питания, положительный зажим ко5 торого через первый ключ и второй резистор соединен с входом интегратора и через второй ключ и третий резистор с положительным зажимом источника питания, выход интегратора соединен с первым вхо0 дом первого компаратора, второй вход которого соединен с первым источником образцового напряжения, выход первого компаратора соединен с установочным входом первого триггера, генератор импульсов,

5 выход которого соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика импульсов, второй вход первого элемента И соединен с первым выходом дешифратора.

0 второй и третий выходы которого соединены с управляющими входами соответственно первого и второго ключей, отличающееся тем, что, с целью повышения точности измерения и расширения функциональных возможностей, в него введены три компаратора, второй триггер, два регистра, делитель частоты, умножитель частоты, постоянное запоминающее устройство, второй элемент И и второй счетчик импульсов, счетный вход которого соединен с выходом второго элемента И, первый вход которого через умножитель частоты соединен с выходом делителя частоты, вход которого соеди нен с выходом генератора импульсов, второй вход второго элемента И соединен с четвертым выходом дешифратора, установочный вход второго счетчика импульсов соединен со стробирующими входами импульсов первого и второго регистров и уста- новочным входом первого счетчика импульсов, выходы которого соединены с соответствующими информационными входами первого регистра и с управляющими

т,го

входами делителя частоты, выходы второго счетчика импульсов через постоянное запоминающее устройство соединены с соответствующими информационными входами

второго регистра, при этом первые входы второго, третьего и четвертого компараторов соединены с выходом интегратора, а вторые входы второго и третьего компараторов соединены соответственно с выходом

второго и третьего источников образцового напряжения, второй вход четвертого компаратора соединен с общей шиной, выход четвертого компаратора соединен с входом установки в О второго триггера, выход которого соединен с первым входом дешифратора, а вход установки в 1 соединен с первым выходом второго компаратора, второй вход которого соединен с установочным выходом первого счетчика импульсов, выход третьего компаратора соединен с входом установки в О первого триггера, выход которого соединен с вторым входом дешифратора.

t

| Измерения в электронике | |||

| Справочник под ред.В.А.Кузнецова, М.: Энергоатомиздат, 1987 | |||

| Автоматическая акустическая блокировка | 1921 |

|

SU205A1 |

Авторы

Даты

1991-09-15—Публикация

1988-04-18—Подача