Изобретение относится к электроизмерительной технике и может быть использовано в цифровых омметрах.

Целью изобретения является расширение диапазона измерения, упрощение устройства и повышение точности за счет исключения погрешностей, вносимых нестабильностью источника ЭДС, сопротивлениями соединительных проводов, дифференциальными параметрами операционных усилителей, снижения мощности, рассеиваемой на измеряемом сопротивлении.

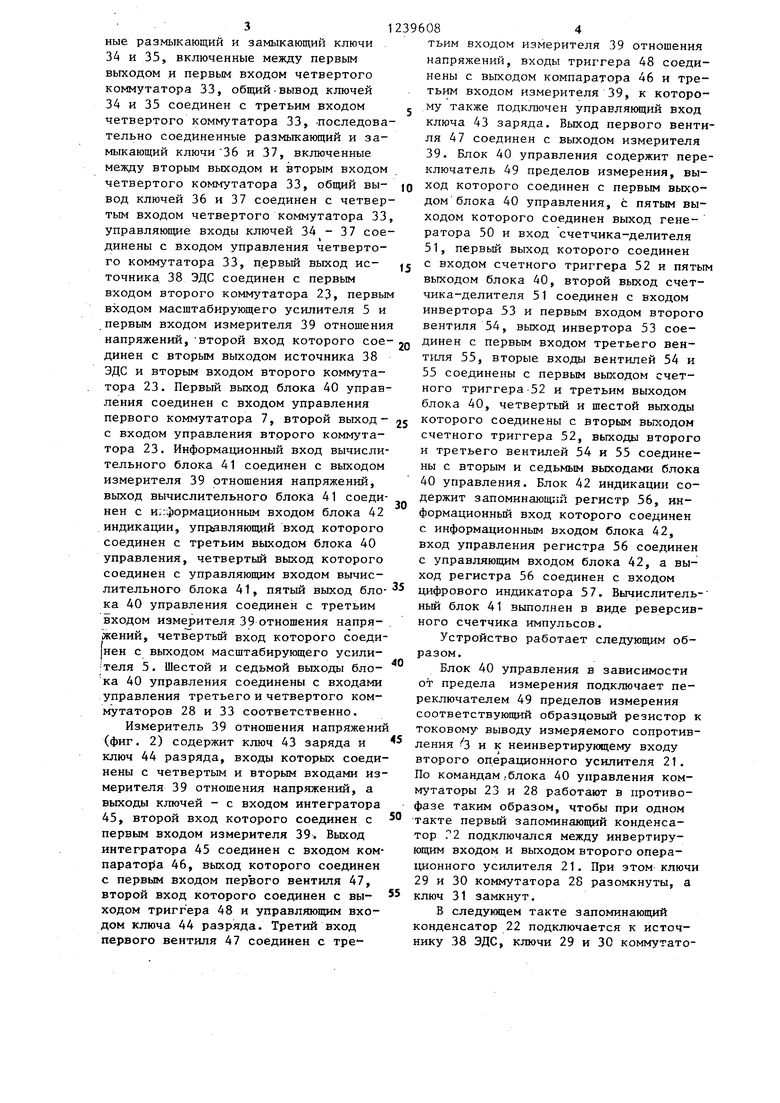

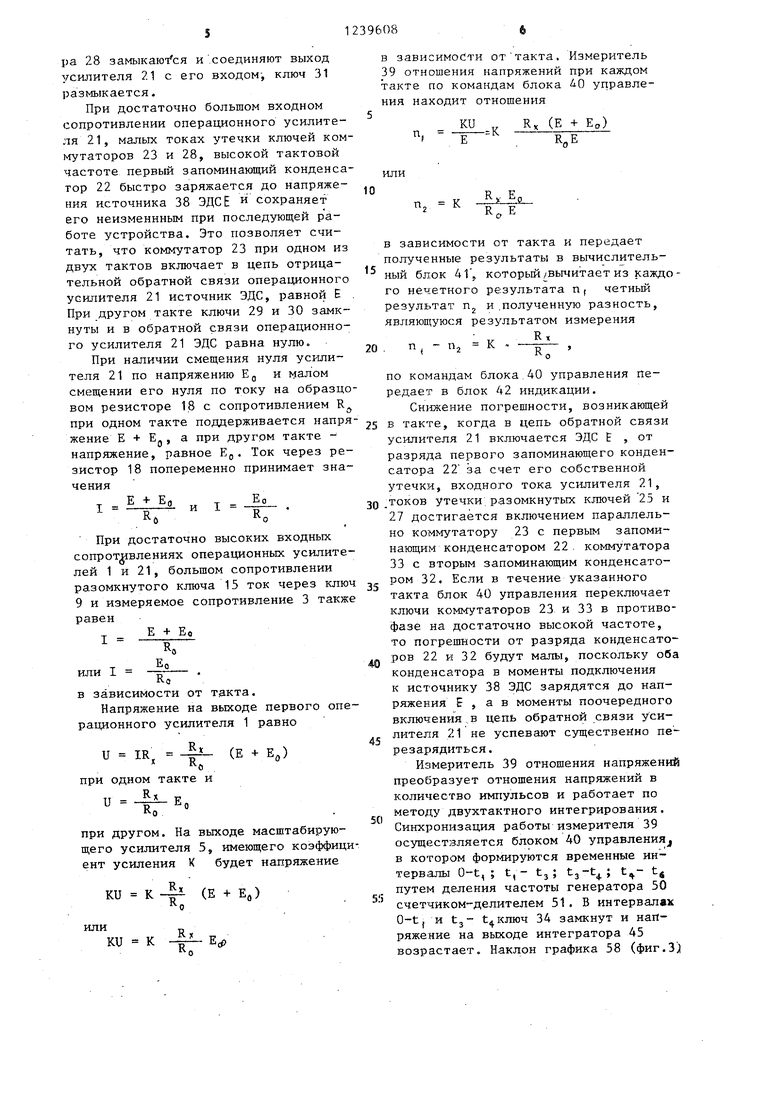

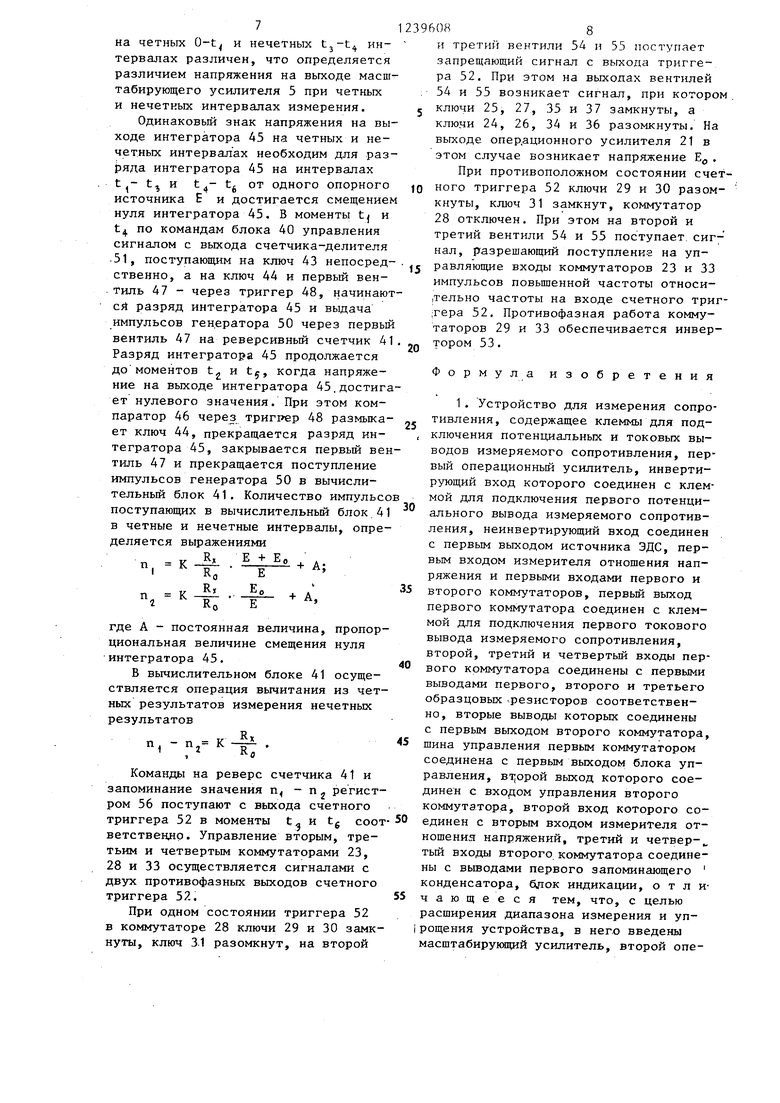

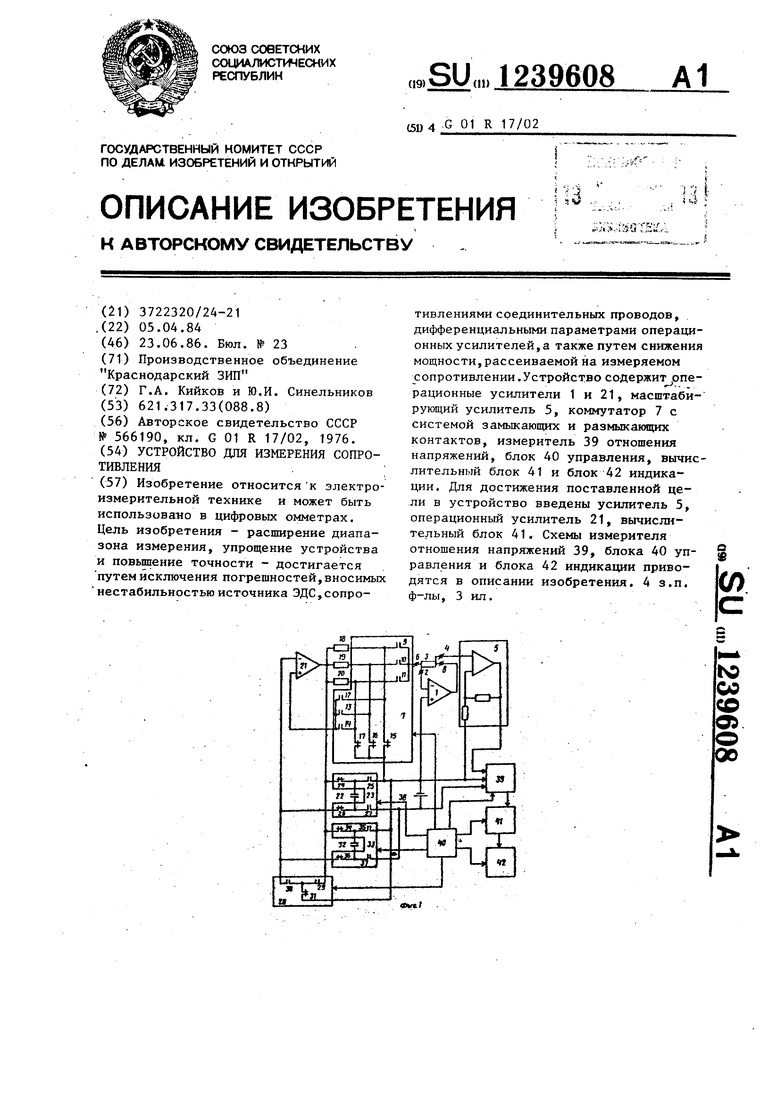

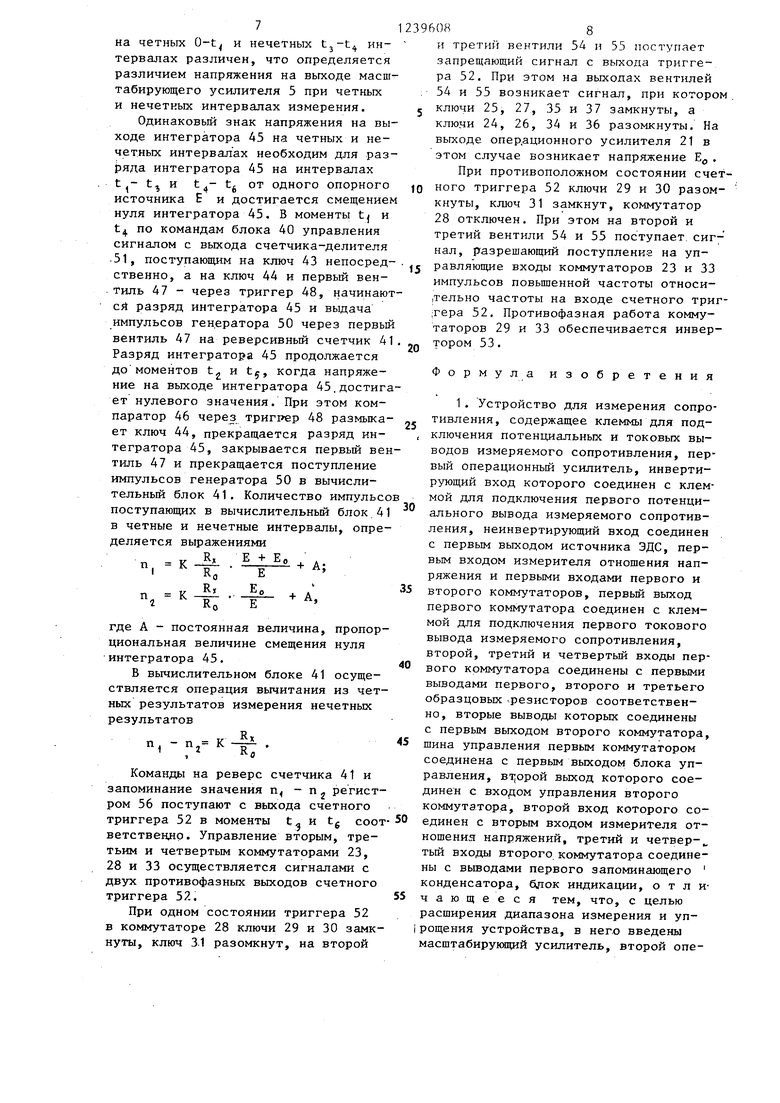

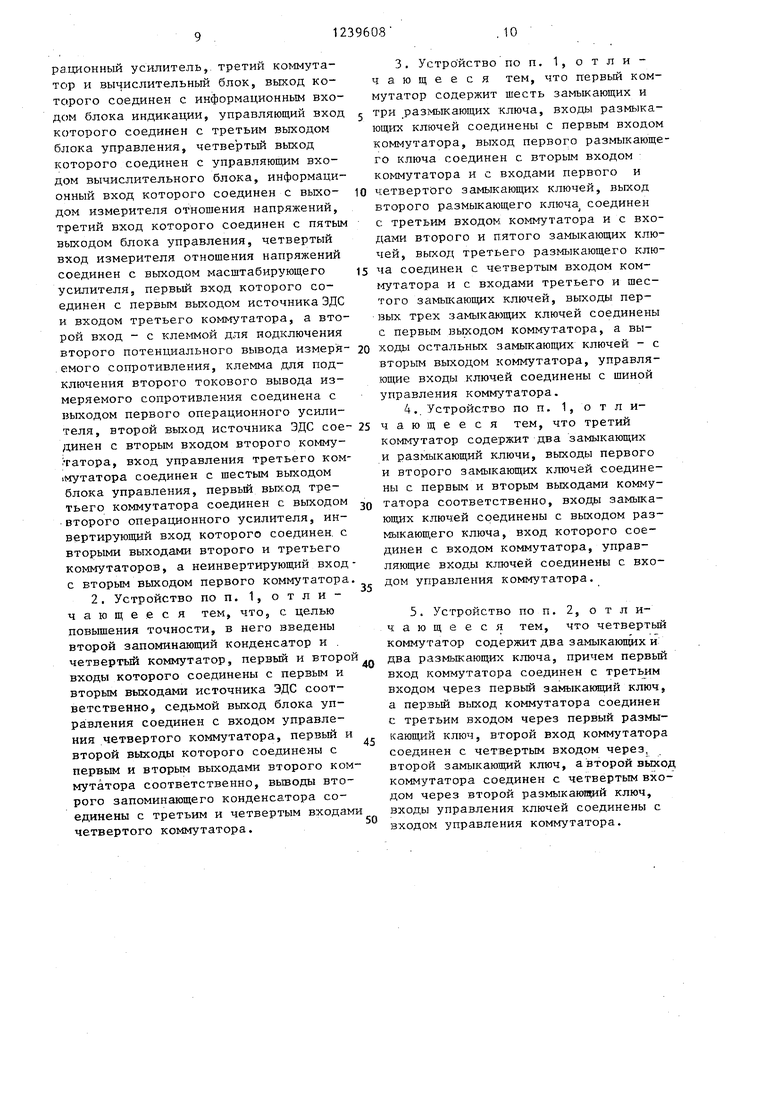

На фиг. 1 представлена схема предлагаемого устройства; на фиг, 2 - схема измерителя отношения, напряжений блока управления и блока индикации; на фиг. 3 - график изменения напряжения на выходе интегратора измерителя отношения напряжений.

Устройство содержит (фиг. 1) пер- Эый операционный усилитель 1, инвер- (Тирующий вход которого соединен с kлeммoй 2 для подключения первого потенциального вывода измеряемого сопротивления 3, клемму А для подключения второго потенциального вывода измеряемого сопротивления, которая соединена с вторым входом масштабирующего усилителя 5, клемму 6 для подключения первого токового вывода измеряемого сопротивления, которая соединена с первым выходом первого коммутатора 7, клемму 8 для подключения второго токового вывода измеряемого сопротивления, которая соединена с выходом первого операционного усилителя 1. Коммутатор 7 содержит шесть замыкающих ключей 9 - 14 и три размыкающих ключа 15 - 17, входы которых соединены с первым входом коммутатора 7, выход первого размыкающего ключа 15 соединен с вторым входом коммутатора 7 и с входами первого и четвертого замыкающих ключей 9 и 12, выход второго размыкающего ключа 16 соединен с третьим входом коммутатора 7 и с входами второго и пятого замыкакидих ключей 10 и 13, выход третьего размыкающего ключа 17 соединен с четвертым входом коммутатора 7 и с входами Tpetbero и шестого замыкающи ключей 11 и 14, выходы первьк трех замыкающих ключей 9-11 соединены с первым вькодом коммутатора .7, а выходы остальных замыкающих ключей 12- 14 - с вторым выходом коммутатора 7, управляющие входы включей 9-17 соединены с входом управления коммутато

5

0

pa 7. Второй, третий и четвертый входы коммутатора 7 соединены с первыми выводами первого, второго и третьего образцовых резисторов 18 - 20, вторые выводы которых соединены с выходом второго операционного усилителя 21, неинвертирующий вход которого соединен с вторым выходом первого коммутатора 7.

Выводы первого запоминающего конденсатора 22 соединены с третьим и четвертым входами второго коммутатора 23, первьш вход которого соединен с первьм входом первого коммутатора 7 и неинвертирующим входом первого операционного усилителя 1.

Второй комментатор 23 содержит последовательно соединенные размыкающий и 3ам1)1Какиций ключи 24 и 25, включенные между первым выходом и первым входом второго коммутатора 23, общий вывод ключей 24 и 25 соединен с третьим входом второго коммутатора 23, последовательно соединенные размыкаю5 щий и замыкающий ключи 26 и 27, включенные между вторым выходом и вторым входом второго коммутатора 23, общий вывод ключей 26 и 27 соединен с четвертым входом второго коммутатора 23.

JJ Управляющие входы ключей 24-27 сое- ринены с входом управления второго Коммутатора 23. Третий коммутатор 28 (Содержит два замыкающих ключа 29 и 30 и размыкающий ключ 31, вход которого с входом третьего коммутато- ра 28, выходы первого и второго замыкающих ключей 29 и 30 соединены с первым и вторым выходами третьего коммутатора 28 соответственно, входы замыкаю1цих ключей 29 и 30 соединены с выходом разг-ыкающего ключа 31, управляющие входы ключей 29-31 соединены с входом управления третьего коммутатора 28, вход которого соединен с первым входом второго коммутатора 23. Выводы второго запоминающего конденсатора 32 соединены с третьим и четвертым входами четвертого коммутатора 33, первый и второй входы которого соединены с первым и вторым входами второго коммутатора 23 соответственно, а первый и второй выходы четвертого коммутатора 33 соединены с первым и вторым выходами второго коммутатора 23, третьего коммутатора 55 28, вьп-содом и инвертирующим входом второго операционного усилителя 21 соответственно. Четвертый коммутатор 33 содержит последовательно соединен0

0

ные размыкающий и замыкающий ключи 34 и 35, включенные между первым выходом и первым входом четвертого коммутатора 33, общийвывод ключей 34 и 35 соединен с третьим входом четвертого коммутатора 33, -последовательно соединенные размыкающий и замыкающий ключи 36 и 37, включенные между вторым выходом и вторым входом четвертого коммутатора 33, общий вы- вод ключей 36 и 37 соединен с четвертым входом четвертого коммутатора 33 управляющие входы ключей 34-37 соединены с входом управления четвертого коммутатора 33, п.ервый выход ис- точника 38 ЭДС соединен с первым входом второго коммутатора 23, первым входом масштабирующего усилителя 5 и первым входом измерителя 39 отношения напряжений, второй вход которого сое- динен с вторым выходом источника 38 ЭДС и вторым входом второго коммутатора 23, Первый выход блока 40 управления соединен с входом управления первого коммутатора 7, второй выход- с входом управления второго коммутатора 23. Информационный вход вычислительного блока 41 соединен с выходом измерителя 39 отношения напряжений, выход вычислительного блока 41 соединен с и;::формационным входом блока 42 индикации, управляющ 1й вход которого соединен с третьим выходом блока 40 управления, четвертый выход которого соединен с управляющим входом вычислительного блока 41, пятый выход блока 40 управления соединен с третьим 1ходом измерителя 39 отношения напря- жений, четвертый вход которого соеди- |нен с выходом масштабирующего усили- теля 5. Шестой и седьмой выходы бло- ка 40 управления соединены с входами управления третьего и четвертого коммутаторов 28 и 33 соответственно.

Измеритель 39 отношения напряжений (фиг. 2) содержит ключ 43 заряда и ключ 44 разряда, входы которых соединены с четвертым и вторым входами измерителя 39 отношения напряжений, а выхода ключей - с входом интегратора 45, второй вход которого соединен с первым входом измерителя 39. Выход интегратора 45 соединен с входом ком- napaTOiJa 46, выход которого соединен с первым входом первого вентиля 47, второй вход которого соединен с вы- ходом триггера 48 и управляющим входом ключа 44 разряда. Третий вход первого вентиля 47 соединен с

, ю 2Q 5

О 5

0

0

тьим входом измерителя 39 отношения напряжений, входы триггера 48 соединены с выходом компаратора 46 и третьим входом измерителя 39, к которому также подключен управляющий вход ключа 43 заряда. Выход первого вентиля 47 соединен с выходом измерителя 39. Блок 40 управления содержит переключатель 49 пределов измерения, выход которого соединен с первым выходом блока 40 управления, с пятым выходом которого соединен выход генератора 50 и вход счетчика-делителя 51, первый выход которого соединен с входом счетного триггера 52 и пятьп выходом блока 40, второй выход счетчика-делителя 51 соединен с входом инвертора 53 и первым входом второго вентиля 54, выход инвертора 53 соединен с первым входом третьего вентиля 55, вторые входы вентилей 54 и 35 соединены с первым выходом счетного триггера-52 и третьим выходом блока 40, четвертый и шестой выходы которого соединены с вторым выходом счетного триггера 52, выходы второго и третьего вентилей 54 и 55 соединены с вторым и седьмым выходами блока 40 управления. Блок 42 индикации содержит запоминающий регистр 56, информационный вход которого соединен с информационным входом блока 42, вход управления регистра 56 соединен с управляющим входом блока 42, а выход регистра 56 соединен с входом цифрового индикатора 57. Вычислитель- ный блок 41 вьшолнен в виде реверсивного счетчика импульсов.

Устройство работает следующим образом.

Блок 40 управления в зависимости от предела измерения подключает переключателем 49 пределов измерения соответствующий образцовый резистор к токовому выводу измеряемого сопротивления f 3 и к неинвертирующему входу второго операционного усилителя 21. По командам,блока 40 управления коммутаторы 23 и 28 работают в противо- фазе таким образом, чтобы при одном такте первый запоминающий конденсатор Г2 подключался между инвертирующим входом и выходом второго операционного усилителя 21. При этом ключи 29 и 30 коммутатора 28 разомкнуты, а ключ 31 замкнут.

В следующем такте запоминающий конденсатор 22 подключается к источнику 38 ЭДС, ключи 29 и 30 коммутатоpa 28 замыкают ся и соединяют выход усилителя 21 с его входом-, ключ 31 размыкается.

При достаточно большом входном сопротивлении операционного усилителя 21, малых токах утечки ключей коммутаторов 23 и 28, высокой тактовой частоте первый запоминающий конденсатор 22 быстро заряжается до напряжения источника 38 ЭДСЕ и сохраняет его неизменнным при последующей работе устройства. Это позволяет считать, что коммутатор 23 при одном из двух тактов включает в цепь отрицательной обратной связи операционного усилителя 21 источник ЭДС, равной Е . При другом такте ключи 29 и 30 замкнуты и в обратной связи операционного усилителя 21 ЭДС равна нулю.

При наличии смещения нуля yci-ши- теля 21 по напряжению Eg и малом смещении его нуля по току на образцовом резисторе 18 с сопротивлением R,. при одном такте поддерживается напряжение Е + Е., а при другом такте - напряжение, равное Eg. Ток через резистор 18 попеременно принимает значения

Е + ЕО .. ЕО

J

R,

I

R,

ч о При достаточно высоких входных сопротивлениях операционных усилителей 1 и 21, большом сопротивлении разомкнутого ключа 15 ток через ключ 9 и измеряемое сопротивление 3 также равен

Е + ЕО

J -

Кл

или I

ЕС

RC

В зависимости от такта.

Напряжение на выходе первого операционного усилителя 1 равно

и IR

R.

R,

(Е + EJ

при одном такте RX

и

Кл

Е,

при другом. На выходе масштабирующего усилителя 5, имеющего коэффициент усиления К будет напряжение

ки К

-| (Н + Е,)

или

ки к

в зависимости от такта. Измеритель 39 отношения напряжений при каждом такте по командам блока 40 управления находит отношения

п,

RX (Е + ЕО) RgE

или

10

К

R. ЕО

К„Е

15

20

в зависимости от такта и передает полученные результаты в вычислитель- блок 41 j который/вычитает из кажд го нечетного результата П( четный результап: п и .полученную разность, являющуюся результатом измерения

RX

.2

п , - п.

к

R,

0

5

0

по командам блока.40 управления передает в блок 42 индикации.

Снижение погрешности, возникающей 5 в такте, когда в цепь обратной связи усилителя 21 включается ЭДС Е , от разряда первого запоминающего конденсатора 22 за счет его собственной утечки, входного тока усилителя 21, токов утечки разомкнутых ключей 25 и 27 достигается включением параллельно коммутатору 23 с первым запоминающим конденсатором 22. коммутатора 33 с вторым запоминающим конденсатором 32, Если в течение указанного такта блок 40 управления переключает ключи коммутаторов 23 и 33 в противо- фазе на достаточно высокой частоте, то погрешности от разряда конденсаторов 22 и 32 будут малы, поскольку оба конденсс1тора в моменты подключения к источнику 38 ЭДС зарядятся до напряжения Е , а в моменты поочередного включения в цепь обратной связи усилителя 21 не успевают существенно перезарядиться.

Измеритель 39 отношения напряжений преобразует отношения напряжений в количество импульсов и работает по методу двухтактного интегрирования. Синхронизация работы измерителя 39 осуществляется блоком 40 yпpaвлeнияJ в котором форгетруются временные ин- терв.алы 0-t, ; t, - tj; t путем деления частоты генератора 50 счетчиком-делителем 51. В интервалах 0-t, и tj- Ц ключ 34 замкнут и напряжение на выходе интегратора 45 возрастает. Наклон графика 58 (фиг.З)

ц-ц

Инна четных 0-t и нечетных тервалах различен, что определяется различием напряжения на выходе масштабирующего усилителя 5 при четных и нечетных интервалах измерения.

Одинаковый знак напряжения на выходе интегратора 45 на четных и нечетных интервалах необходим для разряда интегратора 45 на интервалах

ьи

Ч- ч

от одного опорного

источника Е и достигается смещением нуля интегратора 45. В моменты tj и t по командам блока 40 управления

сигналом с выхода счетчика-делителя .51, поступающим на ключ 43 непосред-. ственно, а на ключ 44 и первый вентиль 47 - через триггер 48, начинают- сй разряд интегратора 45 и выдача импульсов генератора 50 через первый вентиль 47 на реверсивный счетчик 41, Разряд интегратора 45 продолжается до моментов t и t, когда напряжение на выходе интегратора 45.достигает нулевого значения/При этом компаратор 46 через тригрер 48 размыкает ключ 44, прекращается разряд интегратора 45, закрывается первый вентиль 47 и прекращается поступление импульсов генератора 50 в вычислительный блок 41. Количество импульсов поступающих в вычислительный блок 41 в четные и нечетные интервалы, определяется выражениями

К

К

А.

RO

JRj

R.

Е + Е, Е

АО

Е

- + А; + А,

где А - постоянная величина, пропорциональная величине смещения нуля интегратора 45.

В вычислительном блоке 41 осуществляется операция вычитания из четных результатов измерения нечетных результатов

RX

П

- п к

Команды на реверс счетчика 41

1

и

запоминание значения п г Р г ист- ром 56 поступают с выхода счетного триггера 52 в моменты t- и tg соответственно . Управление вторым, третьим и четвертым коммутаторами 23, 28 и 33 осуществляется сигналами с двух противофазных выходов счетного триггера 52.

При одном состоянии триггера 52 в коммутаторе 28 ключи 29 и 30 замкнуты, ключ 31 разомкнут, на второй

. , 2396088

н третий вентили 54 и 55 поступает запрещающий сигнал с выхода триггера 52. При этом на выходах вентилей . 54 и 55 возникает сигнал, при котором. с ключи 25, 27, 35 и 37 замкнуты, а ключи 24, 26, 34 и 36 разомкнуты. На выходе операционного усилителя 21 в этом случае возникает напряжение Е.

При противоположном состоянии счет- 10 ного триггера 52 ключи 29 и 30 разомкнуты, ключ 31 замкнут, коммутатор 28 отключен. При этом на второй и третий вентили 54 и 55 поступает сиг- нал, разрешающий поступление на управляющие входы коммутаторов 23 и 33 импульсов повьшенной частоты относи- ,тельно частоты на входе счетного триг- ,тера 52. Противофазная работа коммутаторов 29 и 33 обеспечивается инвертором 53.

15

20

. - , в25

30

35

40

45

50

55

Форму л а изобретения

1. Устройство для измерения сопротивления, содержащее клеммы для подключения потенциальных и токовых выводов измеряемого сопротивления, первый операционный усилитель, инвертирующий вход которого соединен с клеммой для подключения первого потенциального вывода измеряемого сопротивления, неинвертирующий вход соединен с первым выходом источника ЭДС, первым входом измерителя отношения напряжения и первыми входами первого и второго коммутаторов, первый выход первого коммутатора соединен с клеммой для подключения первого токового вывода измеряемого сопротивления, второй, третий и четвертый входы первого коммутатора соединены с первыми выводами первого, второго и третьего образцовых -резисторов соответственно, вторые выводы которых соединены с первым выходом второго коммутатора, шина управления первым коммутатором соединена с первым выходом блока управления, в 1;орой выход которого соединен с входом управления второго коммутатора, второй вход которого соединен с вторым входом измерителя отношения напряжений, третий и четвер- тый входь второго коммутатора соединены с вьшодами первого запоминающего конденсатора, йдок индикации, отличающееся тем, что, с целью расширения диапазона измерения и уп- I рощения устройства, в нег.о введены масштабирукмций усилитель, второй oneрационный усилитель,, третий коммутатор и вычислительный блок, выход которого соединен с информационным входом блока индикации, управляющий вход которого соединен с третьим выходом блока управления, четвертый выход которого соединен с управляющим входом вычислительного блока, информационный вход которого соединен с выхо- дом измерителя отношения напряжений, третий вход которого соединен с пятым выходом блока управления, четвертый вход измерителя отношения напряжений соединен с выходом масштабирующего усилителя, первый вход которого соединен с первым выходом источника ЭДС и входом третьего коммутатора, а второй вход - с клеммой для подключения второго потенциального вывода измеря- .емого сопротивления, клемма для подключения второго токового вывода измеряемого сопротивления соединена с выходом первого операционного усилителя, второй выход источника ЭДС сое- динен с вторым входом второго коммутатора, вход управления третьего ком 1мутатора соединен с щестым выходом блока управления, первый вькод третьего коммутатора соединен с выходом второго операционного усилителя, инвертирующий вход которого соединен, с вторыми выходами второго и третьего коммутаторов, а неинвертирующий вход с вторым выходом первого коммутатора

2. Устройство по п. 1, отличающееся тем, что, с целью повышения точности, в него введены второй запоминающий конденсатор и . четвертый коммутатор, первый и второ входы которого соединены с первым и вторым выходами источника ЭДС соответственно, седьмой выход блока уп- ра вления соединен с входом управления четвертого коммутатора, первый и второй выходы которого соединены с первым и вторым выходами второго коммутатора соответственно, выводы второго запоминающего конденсатора соединены с третьим и четвертым входам четвертого коммутатора.

s 0 5 д

5

5

0

3. Устро йство по п. 1, отличающееся тем, что первый коммутатор содержит шесть замыкающих и три раз1мыкающих ключа, входы размыкающих ключей соединены с первым входом коммутатора, выход первого размыкающего ключа соединен с вторым входом коммутатора и с входами первого и четвертого замыкающих ключей, выход второго размыкающего ключа соединен с третьим входом коммутатора и с входами второго и пятого замыкающих ключей, выход третьего размыкающего ключа соединен с четвертым входом ком- {-гутатора и с входами третьего и шестого замыкающих ключей, выходы первых трех замыкакзщих ключей соединены с первым выходом коммутатора, а выходы остальных замьжающих ключей - с вторым выходом коммутатора, управляющие входы ключей соединены с щиной управления комм гтатора.

4,. Устройство по п, 1, о т л и- чающееся тем, что третий коммутатор содержит два замыкающих и размыкающий ключи, выходы первого и второго замыкающих ключей соединены с первым и вторым выходами коммутатора соответственно, входы замыкающих ключей соединены с выходом раз- мыкаюш,его ключа, вход которого соединен с входом коммутатора, управляющие входы ключей соединены с входом управления коммутатора.

5. Устройство по п. 2, о т л и- чающееся тем, что четвертвж коммутатор содержит два замыкающих и два размыкающ-их ключа, причем первый вход коммутатора соединен с третьим входом через первый замыкающий ключ, а первьй выход коммутатора соединен с третьим входом через первый размыкающий ключ, второй вход коммутатора соединен с четвертым входом через, второй замыкаюящй ключ, а второй выход коммутатора соединен с четвертым входом через второй размыкающий ключ, входы управления ключей соединены с входом управления коммутатора.

Фб/г.2

tj tztj tif-tf te Фыг.д

X t

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель температуры | 1988 |

|

SU1560987A1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| Устройство для измерения сопротивлений | 1976 |

|

SU566190A1 |

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

| Преобразователь емкостных параметров двухполюсника в интервал времени | 1988 |

|

SU1564569A1 |

| Преобразователь сопротивления постоянному току в интервал времени | 1984 |

|

SU1237993A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1569590A1 |

| Аналого-цифровой преобразователь сопротивления | 1983 |

|

SU1108369A1 |

| Устройство для измерения давления | 1985 |

|

SU1322158A1 |

| Цифровой измеритель температуры | 1984 |

|

SU1224609A1 |

Изобретение относится к электроизмерительной технике и может быть использовано в цифровых омметрах. Цель изобретения - расширение диапазона измерения, упрощение устройства и повышение точности - достигается путем исключения погрешностей,вносимых нестабильностью источника ЭДС,сопротивлениями соединительных проводов, дифференциальными параметрами операционных усилителей, а также путем снижения мощности,рассеиваемой на измеряемом сопротивлении.Устройство содержит операционные усилители 1 и 21, масштабирующий усилитель 5, коммутатор 7 с системой замыкающих и размыкающих контактов, измеритель 39 отношения напряжений, блок 40 управления, вычислительный блок 41 и блок 42 индикации. Для достижения поставленной цели в устройство введены усилитель 5, операционный усилитель 21, вычислительный блок 41. Схемы измерителя отношения напряжений 39, блока 40 управления и блока 42 индикации приводятся в описании изобретения. 4 з.п. ф-лы, 3 шт. (Л с 1C со ;о 00 «м;

Редактор .л. Гратилло

Составитель Б. Тогунов

Техред О.Сопко Корректор И. Муска

Заказ 3390/44Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,г. Ужгород, ул. Проектная, 4

| Устройство для измерения сопротивлений | 1976 |

|

SU566190A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-06-23—Публикация

1984-04-05—Подача