Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано в качестве логического коммутатора, аналогового мультиплексора и демультиплексора с коммутацией каналов по адресным признакам первого и второго срединных аналоговых сигналов четырех переменных, в качестве устройства для параллельного выделения первого и второго срединных сигналов с идентификацией номеров их входов, в качестве четырехвходового идентификатора срединных сигналов, для воспроизведения операций взвешенного суммирования первого и второго срединных сигналов четырех переменных, в качестве формирователя функции медианы четырех переменных, для повышения точности взаиморезервирующей системы из четырех датчиков, в качестве формирователя нелинейных функций и др. Цель изобретения - расширение функциональных возможностей путем идентифи

Ю

ел о

00

3 16795084

кации входов, на которые воздействуютZ22 y22. при

первый и второй срединные сигналы., при

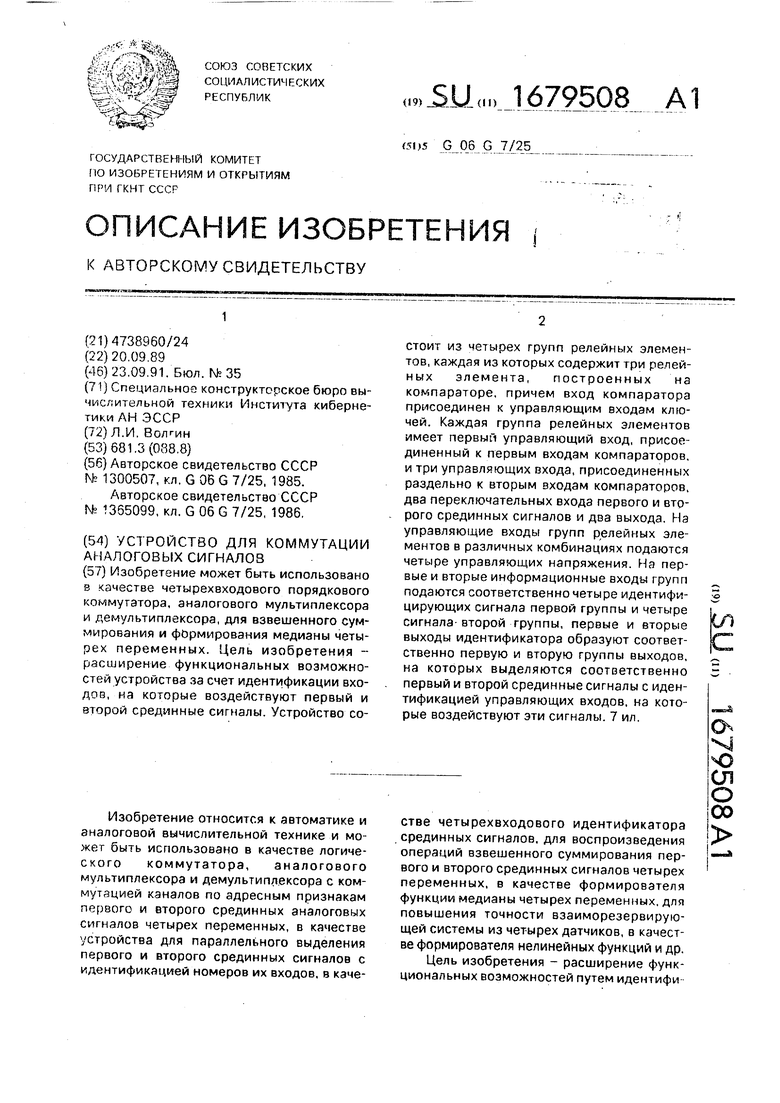

На фиг. 1 изображена базовая схема242 У42, 2 при

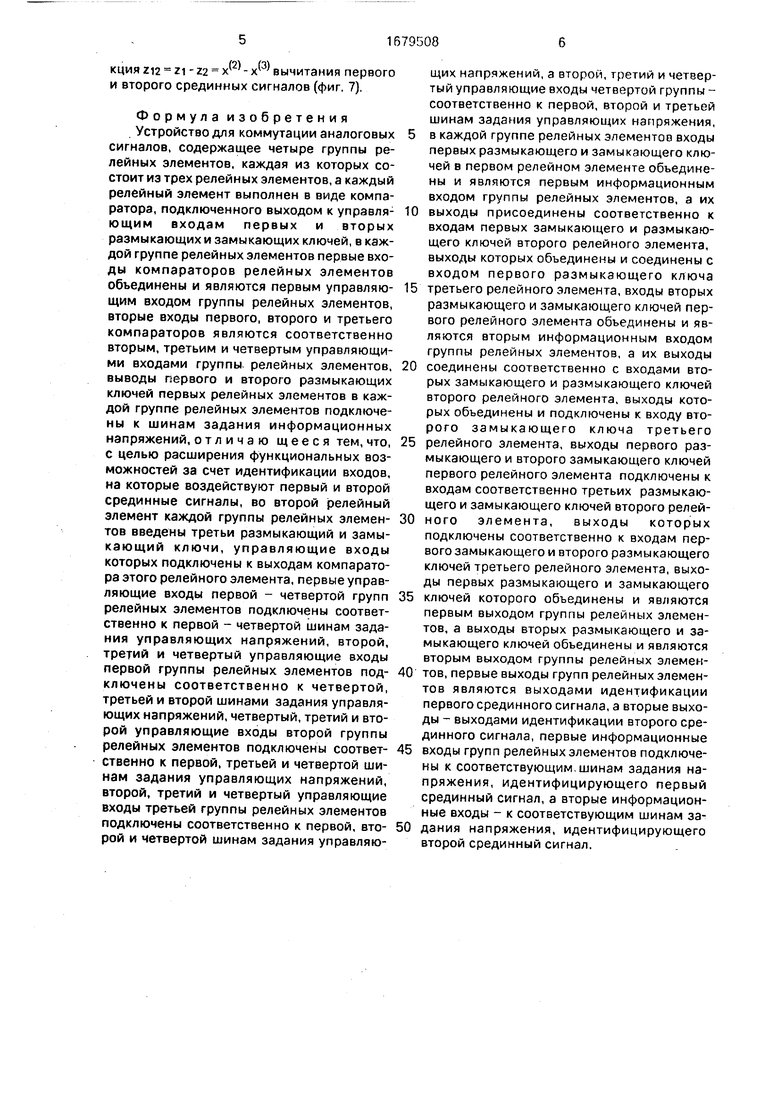

устройства, содержащая четыре группы ре-по признаку принадлежности одного из сиглейных элементов; на фиг. 2-схема группы5 налов xi, Х2, хз, Х4 к второму срединному

релейных элементов: на фиг. 3 - условноесигналу {XL X2, хз, Х4}, который является

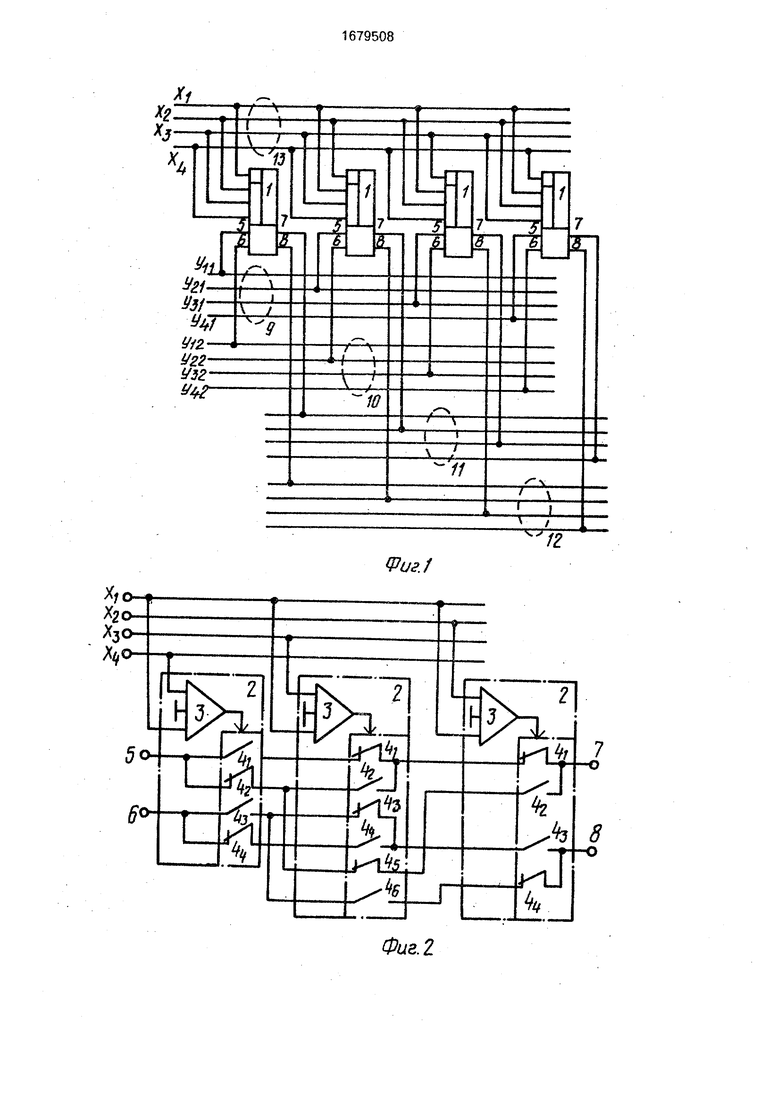

изображение устройства; на фиг. 4 - муль-третьей порядковой статистикой в вариацитиплексорное включение устройства; наонном ряде х х®, х®, х л

фиг. 5 - демультиплексорное включение ус-Таким образом, базовая схема (фиг. 1)

тройства; на фиг. 6 - схема включения уст-10 является логическим коммутатором с комройства при его работе в режиме выделениямутацией каналов по признаку принадлежпервого и второго срединных сигналов сности двух сигналов из управляющих

идентификацией входов, на которые воз-напряжений xi, Х2, хз, Х4 первому х® и втодействуют выделенные сигналы; на фиг. 7 -рому х™ срединному сигналу,

то же, при его работе в режиме выделения15 В схеме включения базовой схемы (фиг.

первого и второго срединных сигналов с4) при работе в мультиплексорном режиме

формированием функции медианы четырехвоспроизводимые мультиплексором по перпеременных.вому и второму выходам функции определяУстройство содержит четыре группы ре-ются соответственно выражениями:

лейных элементов 1, каждая из которых со-20 {уи при ««« ппм )держит релейные элементы 2, выполненныеzi 1у21 при 22

У12 при у 22 прих2 хг;

на компараторе 3 и ключах 4,каждая группа(уз1 при

релейных элементов имеет информацией-I у41 при

,(2)

У32 При L У42 При

ные входы 5 и б и выходы 7 и 8, первыеВ схеме включения базовой схемы при

информационные входы 5 групп, соединен-25 его работе в демультиплексорном режиме

ные шинами 9 задания напряжения иденти-(фиг. 5) воспроизводимые демультиплексофицирующего первый срединный сигнал, аром функции определяются приведенными

вторые входы 6 - шину 10 задания напряже-для фиг. 1 (для фиг. 3) выражениями при

НИЯ идентифицирующего ВТОРОЙ СреДИННЫЙУН У21 У31 У41 У1, У12 У22 У32

сигнал, первые 7 и вторые 8 выходы групп30 у42 У2.

соединены соответственно с шинами идеи-В схеме включения базовой схемы (фиг. тификации первого 11 и второго 12 средин-6) при ее работе в режиме выделения перво- ных сигналов, в устройстве имеется шина 13го и второго х™ срединного сигналов с задания управляющих напряжений xi. Наидентификацией входов, на которые воз- шины 9 и 10 подаются соответственно сиг-35 действуют выделенные сигналы (селектор налы уи и yi2.первого и второго срединных сигналов с

Устройство работает следующим обра-идентификацией входов, на которые воззом.действуют выделенные сигналы), воспроизЕсли напряжение на неинвертирующемводимые селектором функции

входе компаратора больше напряжения на40 определяются приведенными для фиг. 1 выего инвертирующем входе, то ключи нахо-ражениями при

дятся в положении, указанном на фиг. 2уи yi2 xi; У21 У22 Х2; уз1 уз2 хз.

(замыкающие ключи замкнуты, размыкаю-У41 У42 Х4.

щие ключи разомкнуты). В противном слу-Для соединения выводов устройства

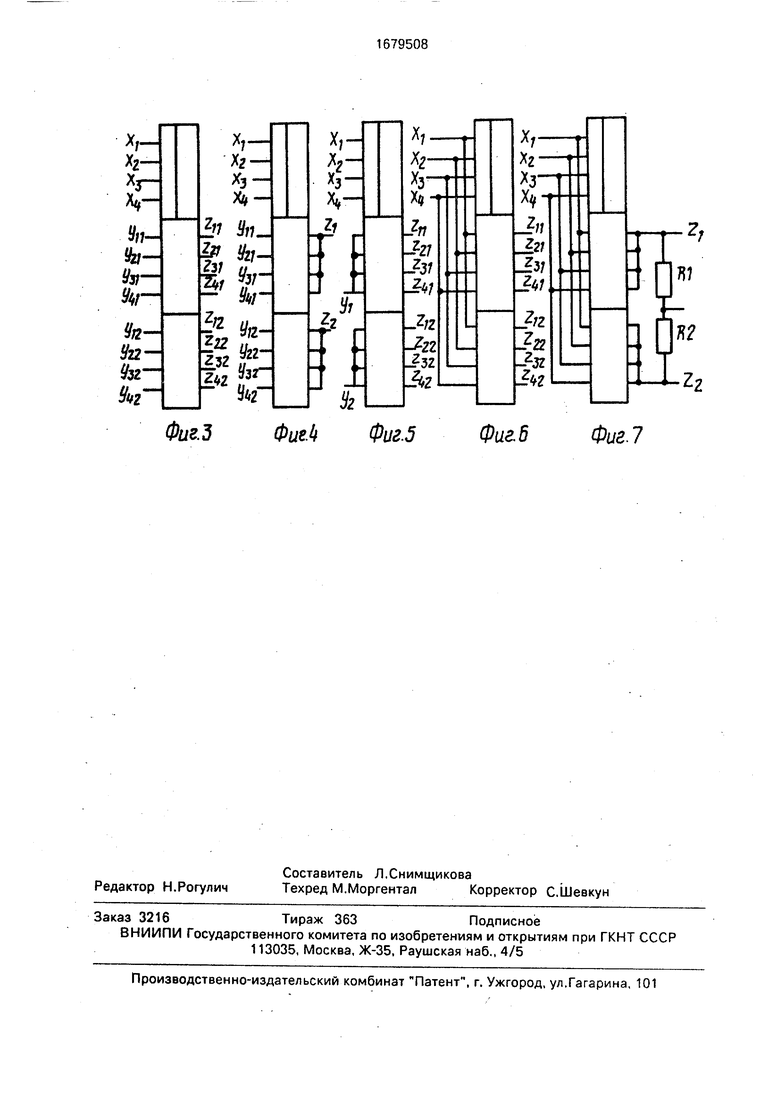

чае имеем обратную картину.45 (фиг, 7) при его работе в режимах выделения

По шинам 11 устройство (фиг. 1)воспро-первого и второго срединных сигналов и

изводит функцию логического коммутирова-формирования взвешенной суммы срединнияных сигналов на резисторах собран дели2ц уц, 221 231 241 0 при xi х|2 ;тель напряжения, вход которого

221 У21, zii 231 241 0 при Х2 х 2 ;50 присоединен между первым и вторым выхо231 У31, 211 221 241 О При ХЗ X 2JДЭМИ.

241 У41, 2ц 221 231 0 при Х4 х™.При равенстве сопротивлений на схеме

по признаку принадлежности одного из сиг-(фиг. 7) по взвешенносуммирующему выхоналовх1, Х2, хз, Х4 к первому срединномуду воспроизводит функцию медианы 2 сигналу б {xi, Х2, хз, Х4}, который явля- 55 0,5(х + х 0 четырех переменных xi. X2, хз,

ется второй порядковой статистикой в вари-Х4. ационном ряде х 2т.х™:х объема m 4.

По шинам 12 устройство воспроизводитПо симметрическому выходу (выходное

««« ппм )22

У12 при у 22 прих2 хг;

У32 При L У42 При

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор- распределитель экстремального сигнала | 1989 |

|

SU1622888A1 |

| Устройство для воспроизведения функции медианы | 1989 |

|

SU1674168A1 |

| Многопороговый функциональный преобразователь | 1989 |

|

SU1689972A2 |

| Устройство для регулирования преобразователя переменного тока в постоянный | 1987 |

|

SU1525809A1 |

| Устройство для ранговой идентификации аналоговых сигналов | 1989 |

|

SU1619318A1 |

| Способ управления инвертором напряжения | 1989 |

|

SU1679590A1 |

| Цифровое устройство для управления тиристорным выпрямителем | 1991 |

|

SU1799494A3 |

| Устройство для раздельного управления реверсивным тиристорным преобразователем | 1987 |

|

SU1503055A1 |

| ГЕНЕРАТОР ПРЕДИКАТНЫХ И АРГУМЕНТНЫХ ФУНКЦИЙ ДВУХ ПЕРЕМЕННЫХ | 1991 |

|

RU2029366C1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2282937C1 |

Изобретение может быть использовано в качестве четырехвходового порядкового коммутатора, аналогового мультиплексора и демультиплексора, для взвешенного суммирования и формирования медианы четырех переменных. Цель изобретения - расширение функциональных возможностей устройства за счет идентификации входов, на которые воздействуют первый и второй срединные сигналы. Устройство состоит из четырех групп релейных элементов, каждая из которых содержит три релей- ных элемента, построенных на компараторе, причем вход компаратора присоединен к управляющим входам ключей. Каждая группа релейных элементов имеет первый управляющий вход, присоединенный к первым входам компараторов, и три управляющих входа, присоединенных раздельно к вторым входам компараторов, два переключательных входа первого и второго срединных сигналов и два выхода. На управляющие входы групп релейных элементов в различных комбинациях подаются четыре управляющих напряжения. На первые и вторые информационные входы групп подаются соответственно четыре идентифицирующих сигнала первой группы и четыре сигнала- второй группы, первые и вторые выходы идентификатора образуют соответственно первую и вторую группы выходов, на которых выделяются соответственно первый и второй срединные сигналы с идентификацией управляющих входов, на которые воздействуют эти сигналы. 7 ил.

функцию логического коммутированиянапряжение снимается между первым zi и

, Z при

вторым Z2 выходами) воспроизводится фуннапряжение снимается между первым zi и

вторым Z2 выходами) воспроизводится фун(2 (-л

кция zi2 zi - Z2 x - xl вычитания первого и второго срединных сигналов (фиг. 7).

Формула изобретения Устройство для коммутации аналоговых сигналов, содержащее четыре группы релейных элементов, каждая из которых состоит из трех релейных элементов, а каждый релейный элемент выполнен в виде компаратора, подключенного выходом к управляющим входам первых и вторых размыкающих и замыкающих ключей, в каждой группе релейных элементов первые входы компараторов релейных элементов объединены и являются первым управляющим входом группы релейных элементов, вторые входы первого, второго и третьего компараторов являются соответственно вторым, третьим и четвертым управляющими входами группы релейных элементов, выводы первого и второго размыкающих ключей первых релейных элементов в каждой группе релейных элементов подключены к шинам задания информационных напряжений, отличаю щееся тем, что, с целью расширения функциональных возможностей за счет идентификации входов, на которые воздействуют первый и второй срединные сигналы, во второй релейный элемент каждой группы релейных элементов введены третьи размыкающий и замыкающий ключи, управляющие входы которых подключены к выходам компаратора этого релейного элемента, первые управляющие входы первой - четвертой групп релейных элементов подключены соответственно к первой - четвертой шинам задания управляющих напряжений, второй, третий и четвертый управляющие входы первой группы релейных элементов подключены соответственно к четвертой, третьей и второй шинами задания управляющих напряжений, четвертый, третий и второй управляющие входы второй группы релейных элементов подключены соответственно к первой,третьей и четвертой шинам задания управляющих напряжений, второй, третий и четвертый управляющие входы третьей группы релейных элементов подключены соответственно к первой, второй и четвертой шинам задания управляющих напряжений, а второй, третий и четвертый управляющие входы четвертой группы - соответственно к первой, второй и третьей шинам задания управляющих напряжения,

в каждой группе релейных элементов входы первых размыкающего и замыкающего ключей в первом релейном элементе объединены и являются первым информационным входом группы релейных элементов, а их

выходы присоединены соответственно к входам первых замыкающего и размыкающего ключей второго релейного элемента, выходы которых объединены и соединены с входом первого размыкающего ключа

третьего релейного элемента, входы вторых размыкающего и замыкающего ключей первого релейного элемента объединены и являются вторым информационным входом группы релейных элементов, а их выходы

соединены соответственно с входами вторых замыкающего и размыкающего ключей второго релейного элемента, выходы которых объединены и подключены к входу второго замыкающего ключа третьего

релейного элемента, выходы первого размыкающего и второго замыкающего ключей первого релейного элемента подключены к входам соответственно третьих размыкающего и замыкающего ключей второго релейного элемента, выходы которых подключены соответственно к входам первого замыкающего и второго размыкающего ключей третьего релейного элемента, выходы первых размыкающего и замыкающего

ключей которого объединены и являются первым выходом группы релейных элементов, а выходы вторых размыкающего и замыкающего ключей объединены и являются вторым выходом группы релейных элементов, первые выходы групп релейных элементов являются выходами идентификации первого срединного сигнала, а вторые выходы - выходами идентификации второго срединного сигнала, первые информационные

входы групп релейных элементов подключены к соответствующим, шинам задания напряжения, идентифицирующего первый срединный сигнал, а вторые информационные входы - к соответствующим шинам задания напряжения, идентифицирующего второй срединный сигнал.

Х;о- Х20Х3о-tyo

Фиг.1

А

Чг

Ъ

jS и

Г

8

Фиг. 2

Фиг.З

ФиеА Фиг.5

Фаг 6

Фиг.7

| Многопороговый функциональный преобразователь | 1985 |

|

SU1300507A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для коммутации аналоговых сигналов | 1986 |

|

SU1365099A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-23—Публикация

1989-09-20—Подача