Изобретение относится к импульсной технике и предназначено для построения функциональных узлов цифровой техники и дискретной автоматики.

Цель изобретения - упрощение, снижение потребляемой мощности и повышение быстродействия счетчика,

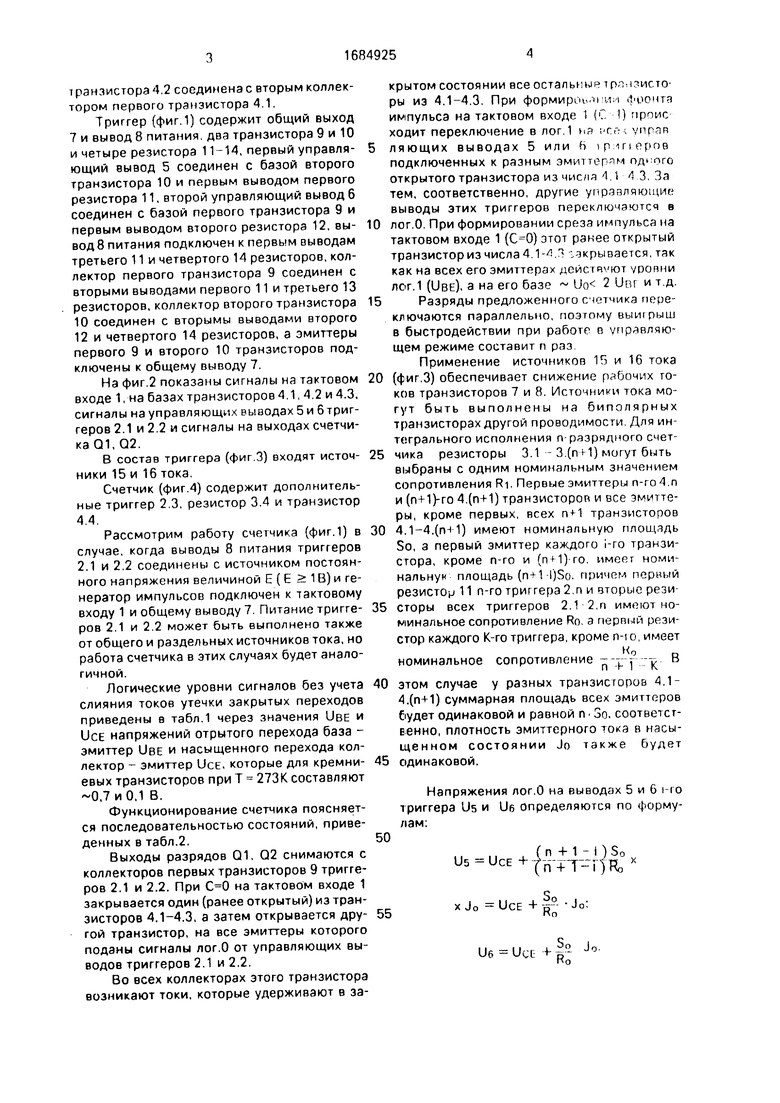

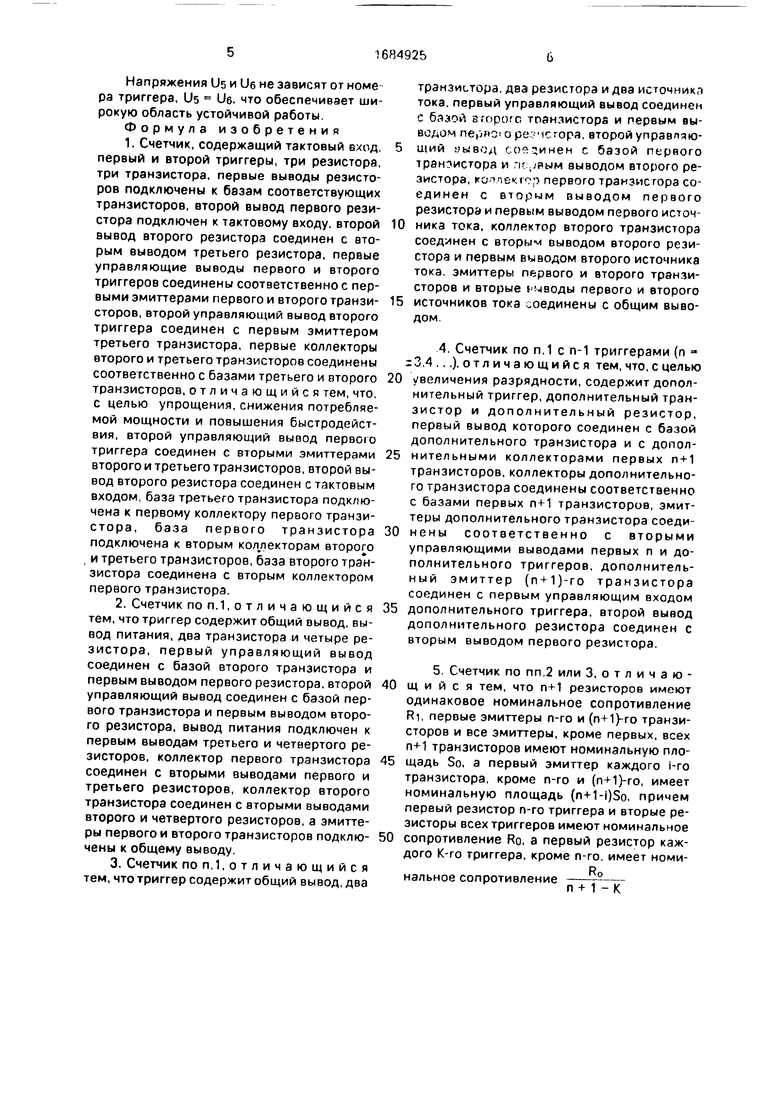

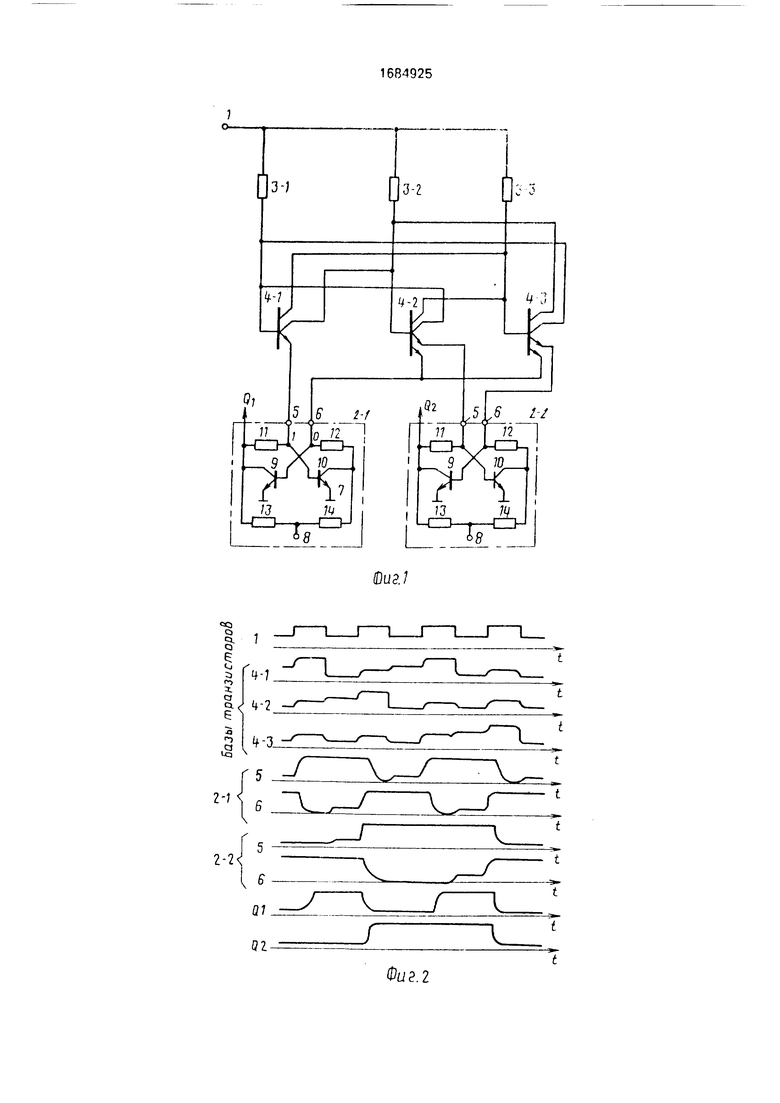

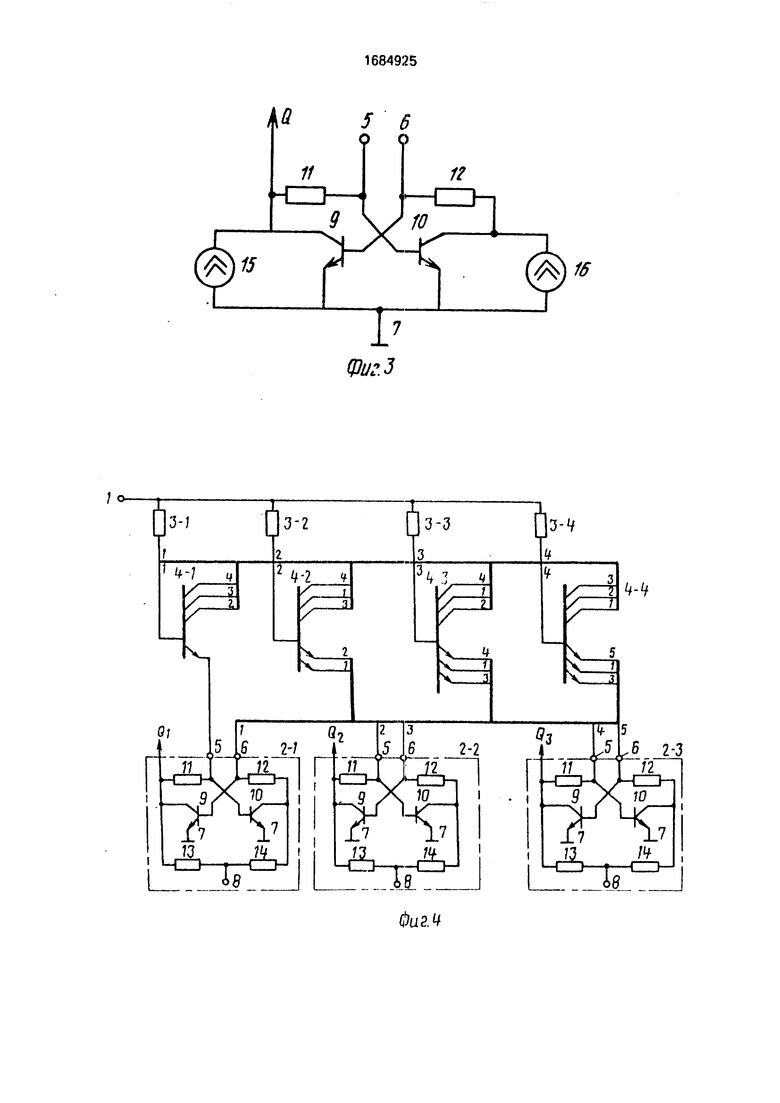

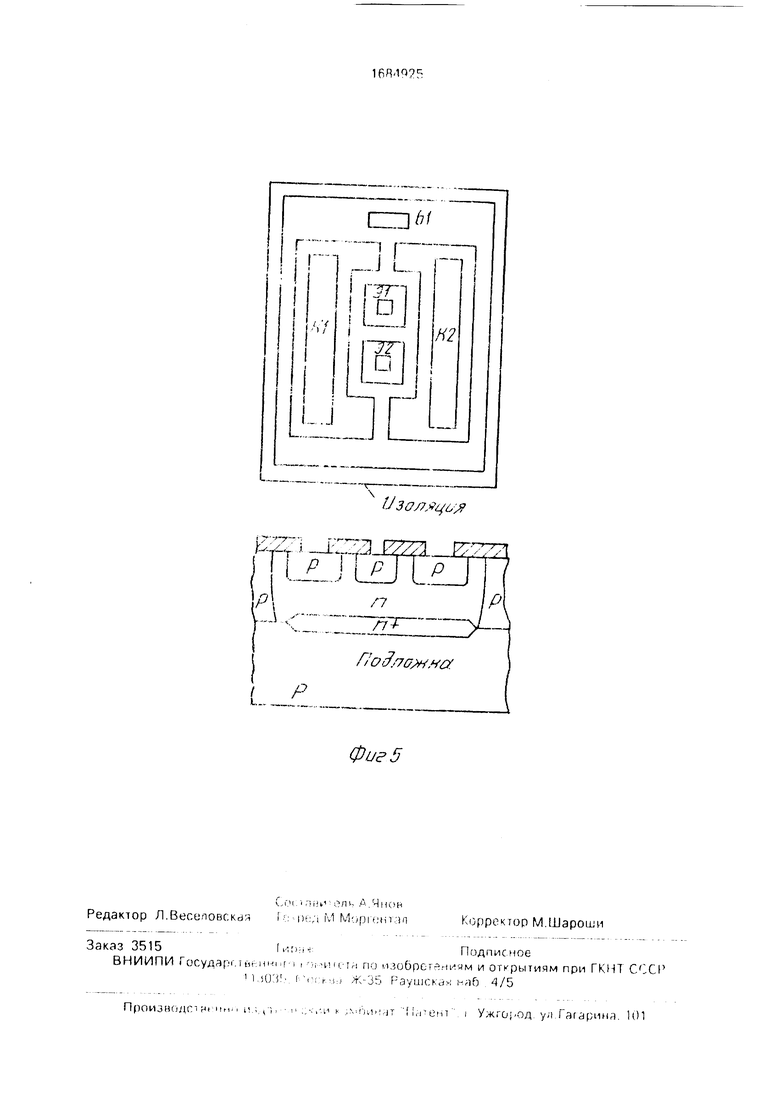

На фиг.1 приведена схема двухразрядного счетчика; на фиг.2 - временная диаграмма работы двухразрядного счетчика; на фиг.З - схема триггера с источниками тока; на фиг.4 - схема счетчика для на фиг.5 - пример реализации двухэмиттерного и двухколлекторного транзистора.

Счетчик (фиг.1) содержит тактовый вход 1, первый и второй триггеры 2.1 и 2,2, три резистора 3.1-3.3, три транзистора 4.1-4.3, первые выводы резисторов 3.1-3.3 подключены к базе соответствующих транзисторов 4.1-4.3, второй вывод первого резистора 3.1 подключен к тактовому входу

Ё

1, второй вывод второго резистора 3.2 сое- с динен с вторым выводом третьего резисто- ра 3.3, первые управляющие выводы первого 2.1 и второго 2.2 триггеров соединены соответственно с первыми эмиттерами первого 4.1 и второго 4.2 транзисторов, а второй управляющий вывод 6 второго триггера 2.2 соединен с первым эмиттером третьего транзистора 4.3, первые коллекторы второго 4.2 и третьего 4.3 транзисторов соединены соответственно с базами третьего 4.3 и второго 4.2 транзисторов. Второй управляющий вывод 6 первого триггера 2.1 соединен с вторыми эмиттерами второго 4.2 и третьего 4.3 транзисторов, второй вывод второго резистора 3.3 подключен к тактовому входу 1, база третьего транзистора 4.3 подключена к первому коллектору первого транзистора 4.1, база первого транзистора 4.1 - к вторым коллекторам второго 4.2 и третьего 4.3 транзисторов, база второго

транзистора 4.2 соединена с вторым коллектором первого транзистора 4.1.

Триггер (фиг.1) содержит общий выход 7 и вывод 8 питания, два транзистора 9 и 10 и четыре резистора 11-14, первый управляющий вывод 5 соединен с базой второго транзистора 10 и первым выводом первого резистора 11, второй управляющий вывод 6 соединен с базой первого транзистора 9 и первым выводом второго резистора 12, вывод 8 питания подключен к первым выводам третьего 11 и четвертого 14 резисторов,коллектор первого транзистора 9 соединен с вторыми выводами первого 11 и третьего 13 резисторов, коллектор второго транзистора 10 соединен с вторымы выводами второго 12 и четвертого 14 резисторов, а эмиттеры первого 9 и второго 10 транзисторов подключены к общему выводу 7.

На фиг.2 показаны сигналы на тактовом входе 1, на базах транзисторов 4.1, 4.2 и 4.3, сигналы на управляющих выводах 5 и бтриг- геров 2.1 и 2.2 и сигналы на выходах счетчика Q1, Q2.

В состав триггера (фиг.З) входят источники 15 и 16 тока,

Счетчик (фиг.4) содержит дополнительные триггер 2.3, резистор 3.4 и транзистор 4.4.

Рассмотрим работу счетчика (фиг.1) в случае, когда выводы 8 питания триггеров 2.1 и 2.2 соединены с источником постоянного напряжения величиной Е ( Е 1 В) и генератор импульсов подключен к тактовому входу 1 и общему выводу 7. Питание триггеров 2.1 и 2.2 может быть выполнено также от общего и раздельных источников тока, но работа счетчика в этих случаях будет аналогичной.

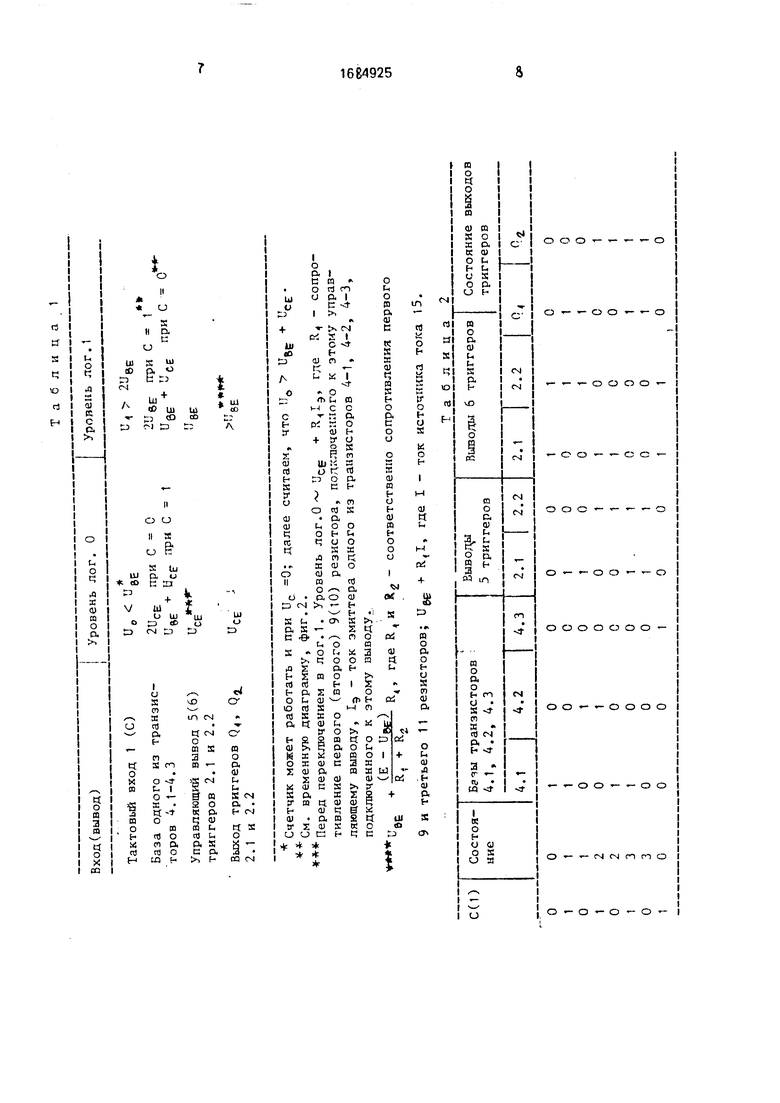

Логические уровни сигналов без учета слияния токов утечки закрытых переходов приведены в табл.1 через значения UBE и UCE напряжений отрытого перехода база - эмиттер UBE и насыщенного перехода коллектор - эмиттер UCE, которые для кремниевых транзисторов при Т 273К составляют 0,7 и 0,1 В.

Функционирование счетчика поясняется последовательностью состояний, приведенных в табл.2.

Выходы разрядов Q1, Q2 снимаются с коллекторов первых транзисторов 9 триггеров 2.1 и 2.2. При на тактовом входе 1 закрывается один (ранее открытый) из транзисторов 4.1-4.3, а затем открывается другой транзистор, на все эмиттеры которого поданы сигналы лог.О от управляющих выводов триггеров 2.1 и 2.2.

Во всех коллекторах этого транзистора возникают токи, которые удерживают в закрытом состоянии все остальныр трл-пистоРЫ ИЗ 4.1-4.3. ПрИ фОрМИрт-.МЧЛ. rt OOHm

импульса на тактовом входе I (С } пропс ходит переключение в лог.1 ня сгг управ

ляющих выводах 5 или h piriepns подключенных к разным эмиттег м пд ото открытого транзистора из числя 41 43. За тем, соответственно, другие управляющие выводы этих триггеров переключаются в

лог.О. При формировании среза импульса на тактовом входе 1 () этот ранее открытый транзисторизчисла4.1-. ;зкрывается, так как на всех его эмиттерах действуют уровни лог.1 (UBE), а на его базе Uo 2 11вг и т.д.

Разряды предложенного счетчика переключаются параллельно, поэтому вышрыш в быстродействии при работе о управляющем режиме составит п раз

Применение источников 15 и 16 тока

(фиг.З) обеспечивает снижение рабочих токов транзисторов 7 и 8. Источники тока могут быть выполнены на биполярных транзисторах другой проводимости. Для интегрального исполнения п-разрядного счетчика резисторы 3.1 - З.(п И) могут быть выбраны с одним номинальным значением сопротивления RL Первые эмиттеры n-го 4.п и (п+1)-го 4.(п+1) транзисторов и все эмиттеры, кроме первых, всех п+1 транзисторов

4.1-4.(ги1) имеют номинальную площадь So, а первый эмиттер каждого 1-го транзистора, кроме n-го и (п + 1) го, имеет номи- нальнуи площадь (nM-ljSo, причем первый резистор 11 n-го триггера 2,п и вторые резисторы всех триггеров 2.1 2.п имеют номинальное сопротивление RO, а первый резистор каждого К-го триггера, кроме n-i о, имеет

Ко

номинальное сопротивление --г г -с В

этом случае у разных транзисторов 4.1- 4.(п+1) суммарная площадь всех эмиттеров будет одинаковой и равной п Зо. соответственно, плотность эмиттерного тока в насы- щенном состоянии Jo также будет

одинаковой.

Напряжения лог.О на выводах 5 и 6 ыо триггера Us и Ue определяются по формулам:

55

2

х J0 UCE + -5° J°:

Ro

U6 UgE ff J HO

Напряжения Us и Ue не зависят от номера триггера, Us Ue. что обеспечивает широкую область устойчивой работы.

Формула изобретения

1.Счетчик, содержащий тактовый вход, первый и второй триггеры, три резистора, три транзистора, первые выводы резисторов подключены к базам соответствующих транзисторов, второй вывод первого резистора подключен к тактовому входу, второй вывод второго резистора соединен с вторым выводом третьего резистора, первые управляющие выводы первого и второго триггеров соединены соответственно с первыми эмиттерами первого и второго транзисторов, второй управляющий вывод второго триггера соединен с первым эмиттером третьего транзистора, первые коллекторы второго и третьего транзисторов соединены соответственно с базами третьего и второго транзисторов, отличающийся тем, что, с целью упрощения, снижения потребляемой мощности и повышения быстродействия, второй управляющий вывод первого триггера соединен с вторыми эмиттерами второго и третьего транзисторов, второй вывод второго резистора соединен с тактовым входом, база третьего транзистора подключена к первому коллектору первого транзистора, база первого транзистора подключена к вторым коллекторам второго и третьего транзисторов, база второго транзистора соединена с вторым коллектором первого транзистора.

2.Счетчик по п.1,отличающийся тем, что триггер содержит общий вывод, вывод питания, два транзистора и четыре резистора, первый управляющий вывод соединен с базой второго транзистора и первым выводом первого резистора, второй управляющий вывод соединен с базой первого транзистора и первым выводом второго резистора, вывод питания подключен к первым выводам третьего и четвертого резисторов, коллектор первого транзистора соединен с вторыми выводами первого и третьего резисторов, коллектор второго транзистора соединен с вторыми выводами второго и четвертого резисторов, а эмиттеры первого и второго транзисторов подключены к общему выводу.

3.Счетчик по п. 1,отличающийся тем, что триггер содержит общий вывод, два

транзистора, деа резистора и два источника тока, первый управляющий вывод соединен с базой второго тоанзистора и первым выводом ne(jfio--o pec.icгора, второй управляюший УЫВОД соединен с базой первого транзистора и первым выводом второго резистора, коллектор первого транзистора соединен с вторым выводом первого резистора и первым выводом первого источника тока, коллектор второго транзистора соединен с вторым выводом второго резистора и первым выводом второго источника тока, эмиттеры первого и второго транзисторов и вторые 1 лводы первого и второго

источников тока соединены с общим выводом.

4.Счетчик по п.1 с п-1 триггерами (п - г 3,4 ...), отличающийся тем, что, с целью

увеличения разрядности, содержит дополнительный триггер, дополнительный транзистор и дополнительный резистор, первый вывод которого соединен с базой дополнительного транзистора и с дополнительными коллекторами первых п+1 транзисторов,коллекторы дополнительного транзистора соединены соответственно с базами первых п+1 транзисторов, эмиттеры дополнительного транзистора соединены соответственно с вторыми управляющими выводами первых п и дополнительного триггеров, дополнительный эмиттер (п + 1)-го транзистора соединен с первым управляющим входом

дополнительного триггера, второй вывод дополнительного резистора соединен с вторым выводом первого резистора.

5.Счетчик по пп.2 или 3, отличаю- щ и и с я тем, что п+1 резисторов имеют

одинаковое номинальное сопротивление RI, первые эмиттеры n-го и (п+1)-го транзисторов и все эмиттеры, кроме первых, всех п+1 транзисторов имеют номинальную площадь So, а первый эмиттер каждого i-ro транзистора, кроме n-го и (п+1}-го, имеет номинальную площадь (n+1-i)So, причем первый резистор n-го триггера и вторые резисторы всех триггеров имеют номинальное

сопротивление RO, а первый резистор каждого К-го триггера, кроме n-го. имеет номиRO

нальное сопротивление -----

п + 1 - К

Вход(вывод)

Тактовый вход 1 (С)

База одного из транзисторов 4.1-4.3

Управляющий вывод 5(6) триггеров 2.1 и 2.2

Выход триггеров Q, Q 2.1 и 2.2

ровень лог. О

1

Uo V

Таблица 1 Уровень лог.1

U, 2U,

BE

2U

СЕ

при С О

UftE + Нсг при С 1

2U6E при С 1

U6g + UCE при С О

IT LCE

J

BE

СЕ

s 1

1J8E

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор напряжения постоянного тока | 1989 |

|

SU1677703A1 |

| Кольцевой счетчик | 1988 |

|

SU1539998A1 |

| Коммутатор переменного напряжения | 1986 |

|

SU1338052A1 |

| Высоковольтный переключатель | 1989 |

|

SU1709511A1 |

| Устройство контроля сопротивления резистивного элемента | 1988 |

|

SU1700744A1 |

| Кольцевой счетчик | 1988 |

|

SU1539997A1 |

| Транзисторный инвертор | 1988 |

|

SU1615854A1 |

| Счетчик с неразрушающейся информацией | 1989 |

|

SU1651380A1 |

| Стабилизирующий конвертор напряжения постоянного тока | 1988 |

|

SU1557648A1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1457115A1 |

Изобретение относится к импульсной технике и может быть использовано для построения функциональных узлов цифровой техники и дискретной автоматики. Счетчик содержит тактовый вход, первый и второй триггеры, три резистора и три транзистора. Каждый из триггеров содержит общий вывод, вывод питания, два транзистора и четыре резистора, при этом вместо двух резисторов в каждом триггере могут быть использованы два источника тока. Введение дополнительных эмиттеров и коллекторов транзисторов счетчика, а также новых связей позволяет упростить счетчик, снизить потребляемую мощность и повысить быстродействие счетчика. 4 з.п.ф-лы, 2 табл. 5 ил.

Счетчик может работать и при Uc 0; далее считаем, что Ue 1тВе + UCE . См. временную диаграмму, фиг.2.

w JLi,

Перед переключением в лог.1. Уровень лог.О - TJCg + , где R - сопротивление первого (второго) 9(10) резистора, подключенного к этому управляющему выводу, Ig - ток эмиттера одного из транзисторов 4-1, 4-2, 4-3, подключенного к этому выводу.

(Е - U№)

R, +

R,

9 и третьего 11 резисторов; + Н.1, где I - ток источника тока 15.

Таблица 2

вого (второго) 9(10) резистора, подключенного к этому управду, Ig - ток эмиттера одного из транзисторов 4-1, 4-2, 4-3, о к этому выводу.

U№)

R,

R

4

где R,, и Rg - соответственно сопротивления первого

OJ

S

(О ГО

ел

Пзч

ч,

Пз-г

Фаз. 2

o

от

2

to

NO (Л

Г

Ј

Y iгГ. v7 V/ ,

FLf. J im.

/9

V.i , -

.... f---,

-J l

I

L°

m

-j i

H2

j

изолщья

/7

T/T

О

/7o(/7GJrt#&

Фиг 5

f:

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| М.: Сов | |||

| радио, 1975, с.99, рис.3.17 | |||

| Crebene A.B | |||

| Bipolar and Mos Analog Integrated Circuit Deslng | |||

| New York: John Wiley & Sons, 1984 | |||

| НОЖЕВАЯ ПОЧВООБРАБАТЫВАЮЩАЯ ФРЕЗА С ПРИСОБЛЕНИЕМ ДЛЯ ИЗВЛЕЧЕНИЯ СОРНЫХ ТРАВ И КАМНЕЙ | 1922 |

|

SU611A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-10-15—Публикация

1989-03-20—Подача