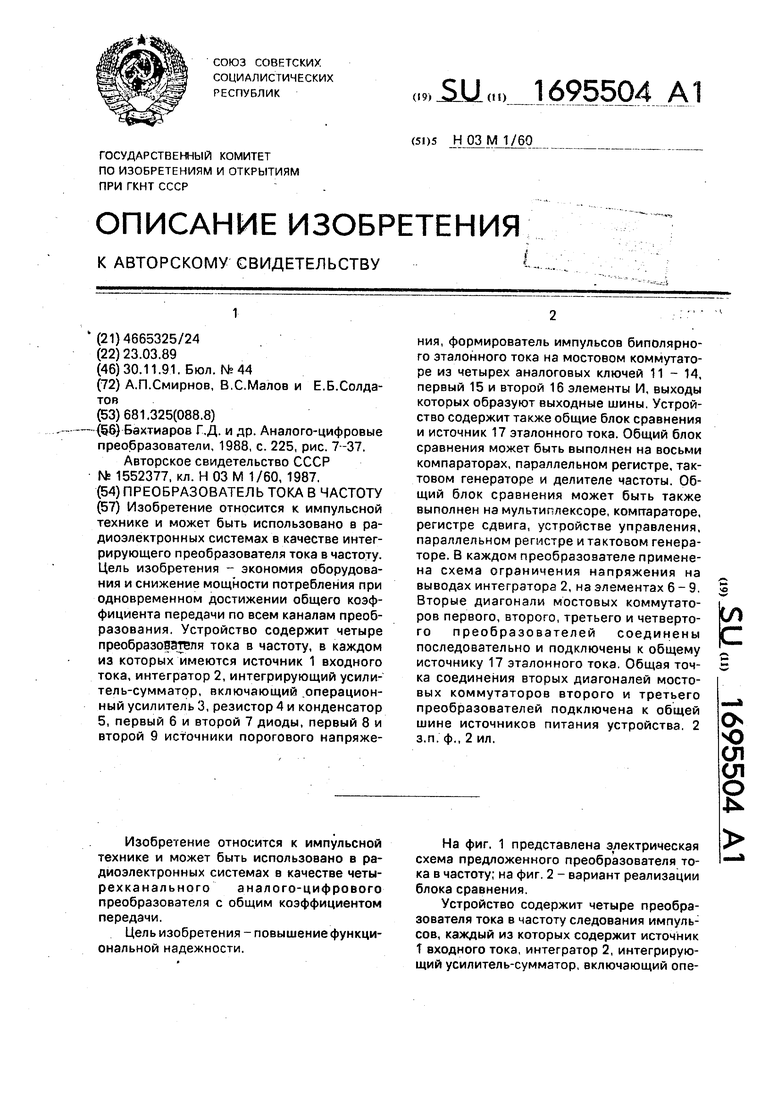

Изобретение относится к импульсной технике и может быть использовано в радиоэлектронных системах в качестве четы- рехканального аналого-цифрового преобразователя с общим коэффициентом передачи.

Цель изобретения - повышение функциональной надежности.

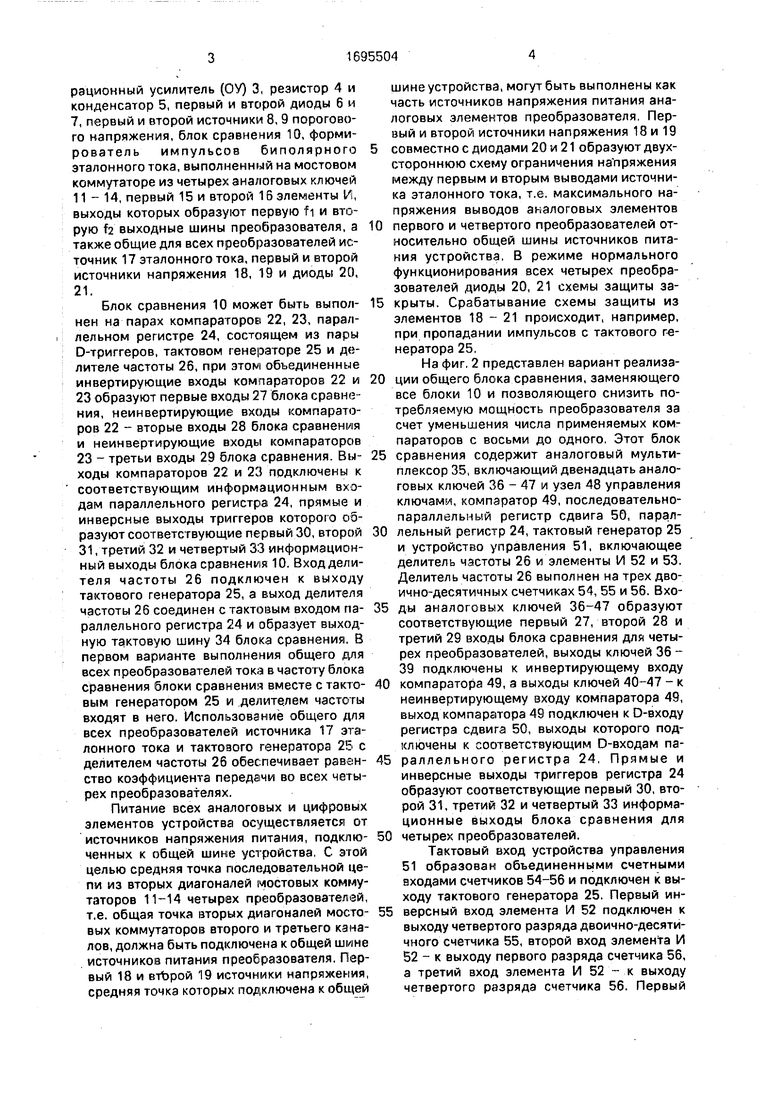

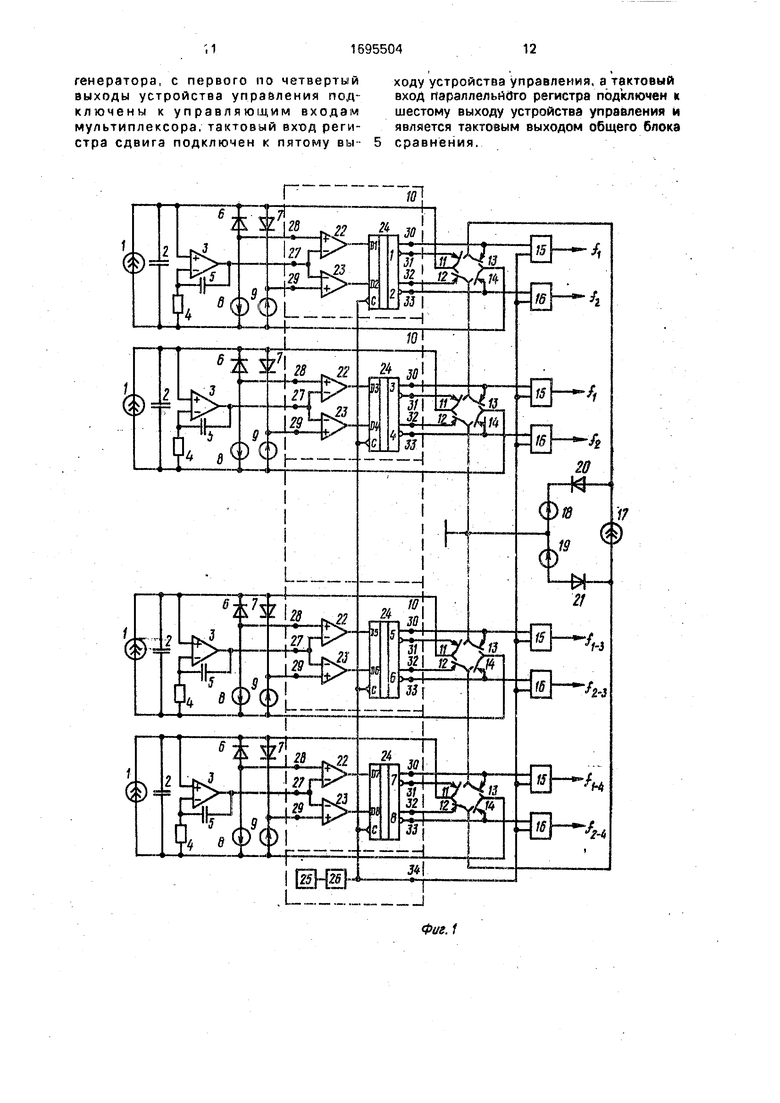

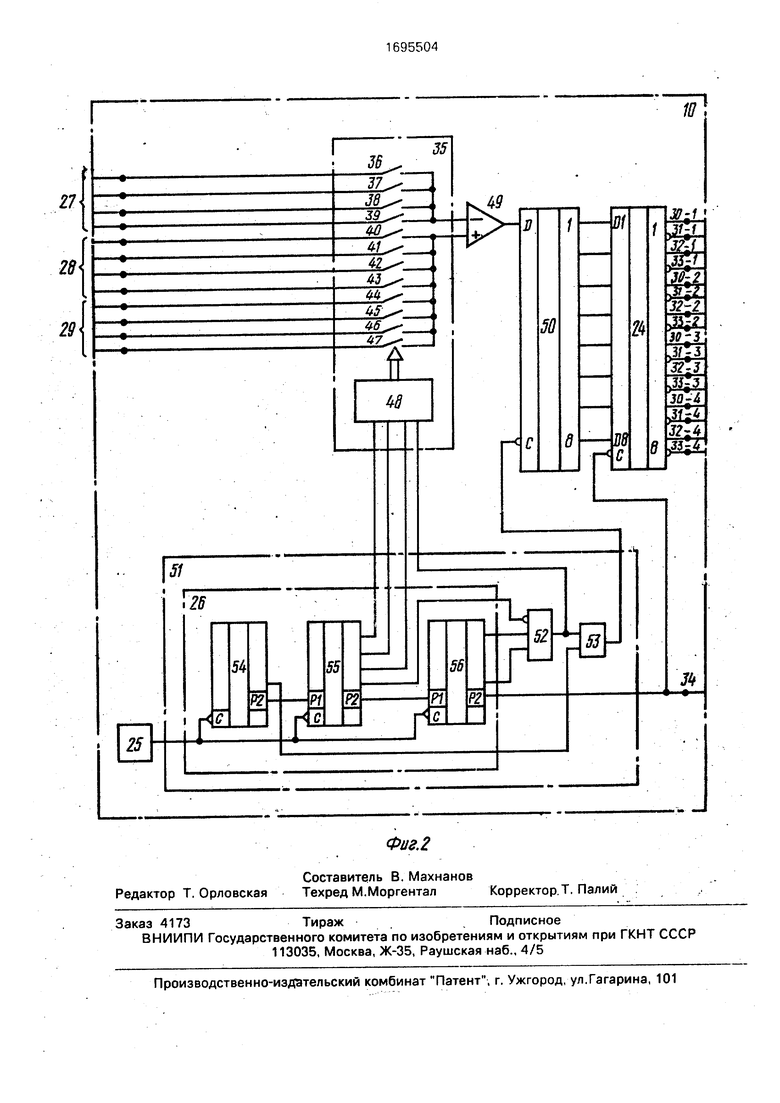

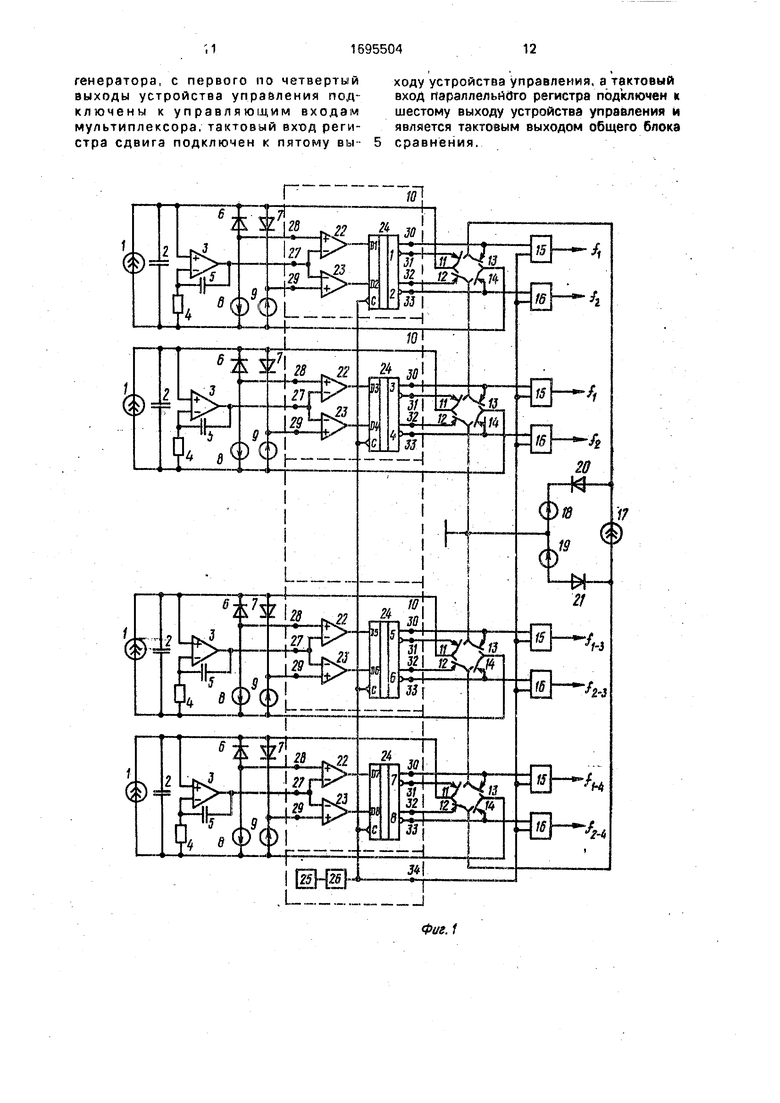

На фиг. 1 представлена электрическая схема предложенного преобразователя тока в частоту; на фиг. 2 - вариант реализации блока сравнения.

Устройство содержит четыре преобразователя тока в частоту следования импульсов, каждый из которых содержит источник 1 входного тока, интегратор 2, интегрирующий усилитель-сумматор, включающий oneрационный усилитель (ОУ) 3, резистор 4 и конденсатор 5, первый и второй диоды 6 и 7, первый и второй источники 8, 9 порогового напряжения, блок сравнения 10, формирователь импульсов биполярного эталонного тока, выполненный на мостовом коммутаторе из четырех аналоговых ключей 11-14, первый 15 и второй 16 элементы И, выходы которых образуют первую fi и вторую h выходные шины преобразователя, а также общие для всех преобразователей источник 17 эталонного тока, первый и второй источники напряжения 18, 19 и диоды 20, 21.

Блок сравнения 10 может быть выполнен на парах компараторов 22, 23, параллельном регистре 24, состоящем из пары D-триггеров, тактовом генераторе 25 и делителе частоты 26, при этом объединенные инвертирующие входы компараторов 22 и 23 образуют первые входы 27 блока сравнения, неинвертирующие входы компараторов 22 - вторые входы 28 блока сравнения и неинвертирующие входы компараторов 23 - третьи входы 29 блока сравнения. Выходы компараторов 22 и 23 подключены к соответствующим информационным входам параллельного регистра 24, прямые и инверсные выходы триггеров которого образуют соответствующие первый 30, второй 31, третий 32 и четвертый 33 информационный выходы блока сравнения 10. Вход делителя частоты 26 подключен к выходу тактового генератора 25, а выход делителя частоты 26 соединен с тактовым входом параллельного регистра 24 и образует выходную тактовую шину 34 блока сравнения. В первом варианте выполнения общего для всех преобразователей тока в частоту блока сравнения блоки сравнения вместе с тактовым генератором 25 и делителем частоты входят в него. Использование общего для всех преобразователей источника 17 эталонного тока и тактового генератора 25 с делителем частоты 26 обеспечивает равенство коэффициента передачи во всех четырех преобразователях.

Питание всех аналоговых и цифровых элементов устройства осуществляется от источников напряжения питания, подключенных к общей шине устройства. С этой целью средняя точка последовательной цепи из вторых диагоналей мостовых коммутаторов 11-14 четырех преобразователей, т.е. общая точка вторых диагоналей мостовых коммутаторов второго и третьего каналов, должна быть подключена к общей шине источников питания преобразователя. Первый 18 и втЪрой 19 источники напряжения, средняя точка которых подключена к общей

шине устройства, могут быть выполнены как часть источников напряжения питания аналоговых элементов преобразователя. Первый и второй источники напряжения 18 и 19

совместно с диодами 20 и 21 образуют двухстороннюю схему ограничения напряжения между первым и вторым выводами источника эталонного тока, т.е. максимального напряжения выводов аналоговых элементов

0 первого и четвертого преобразователей относительно общей шины источников питания устройства. В режиме нормального функционирования всех четырех преобразователей диоды 20, 21 схемы защиты за5 крыты. Срабатывание схемы защиты из элементов 18-21 происходит, например, при пропадании импульсов с тактового генератора 25.

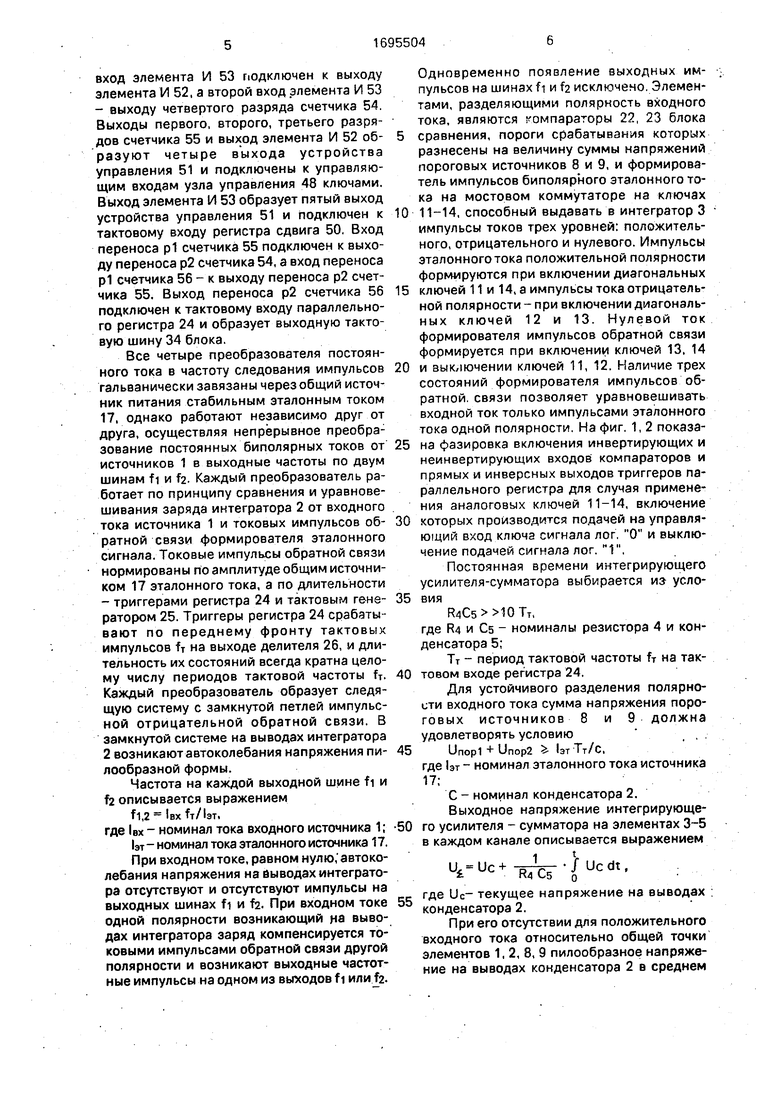

На фиг. 2 представлен вариант реализа0 ции общего блока сравнения, заменяющего все блоки 10 и позволяющего снизить потребляемую мощность преобразователя за счет уменьшения числа применяемых компараторов с восьми до одного. Этот блок

5 сравнения содержит аналоговый мультиплексор 35, включающий двенадцать аналоговых ключей 36 - 47 и узел 48 управления ключами, компаратор 49, последовательно- параллельный регистр сдвига 50, парал0 лельный регистр 24, тактовый генератор 25 и устройство управления 51, включающее делитель частоты 26 и элементы И 52 и 53. Делитель частоты 26 выполнен на трех двоично-десятичных счетчиках 54, 55 и 56. Вхо5 ды аналоговых ключей 36-47 образуют соответствующие первый 27, второй 28 и третий 29 входы блока сравнения для четырех преобразователей, выходы ключей 36 - 39 подключены к инвертирующему входу

0 компаратора 49, а выходы ключей 40-47 - к неинвертирующему входу компаратора 49, выход компаратора 49 подключен к D-входу регистра сдвига 50, выходы которого подключены к соответствующим D-входам па5 раллельного регистра 24. Прямые и инверсные выходы триггеров регистра 24 образуют соответствующие первый 30, второй 31, третий 32 и четвертый 33 информационные выходы блока сравнения для

0 четырех преобразователей.

Тактовый вход устройства управления

51образован объединенными счетными входами счетчиков 54-56 и подключен к выходу тактового генератора 25. Первый ин5 версный вход элемента И 52 подключен к выходу четвертого разряда двоично-десятичного счетчика 55, второй вход элемента И

52- к выходу первого разряда счетчика 56, а третий вход элемента И 52 - к выходу четвертого разряда счетчика 56. Первый

вход элемента И 53 подключен к выходу элемента И 52, а второй вход элемента И 53

-выходу четвертого разряда счетчика 54. Выходы первого, второго, третьего разрядов счетчика 55 и выход элемента И 52 образуют четыре выхода устройства управления 51 и подключены к управляющим входам узла управления 48 ключами. Выход элемента И 53 образует пятый выход устройства управления 51 и подключен к тактовому входу регистра сдвига 50. Вход переноса р1 счетчика 55 подключен к выходу переноса р2 счетчика 54, а вход переноса р1 счетчика 56 - к выходу переноса р2 счетчика 55. Выход переноса р2 счетчика 56 подключен к тактовому входу параллельного регистра 24 и образует выходную тактовую шину 34 блока.

Все четыре преобразователя постоянного тока в частоту следования импульсов гальванически завязаны через общий источник питания стабильным эталонным током 17, однако работают независимо друг от друга, осуществляя непрерывное преобра: зование постоянных биполярных токов от источников 1 в выходные частоты по двум шинам fi и Т2. Каждый преобразователь работает по принципу сравнения и уравновешивания заряда интегратора 2 от входного тока источника 1 и токовых импульсов обратной связи формирователя эталонного сигнала. Токовые импульсы обратной связи нормированы по амплитуде общим источником 17 эталонного тока, а по длительности

-триггерами регистра 24 и тактовым генератором 25. Триггеры регистра 24 срабатывают по переднему фронту тактовых импульсов fr на выходе делителя 26, и длительность их состояний всегда кратна целому числу периодов тактовой частоты fT. Каждый преобразователь образует следящую систему с замкнутой петлей импульсной отрицательной обратной связи. В замкнутой системе на выводах интегратора 2 возникают автоколебания напряжения пилообразной формы.

Частота на каждой выходной шине fi и h описывается выражением

fl,2 UxfT/Ur,

где Ux - номинал тока входного источника 1;

эт номинал тока эталонного источника 17.

При входном токе, равном нулю, автоколебания напряжения на вы водах интегратора отсутствуют и отсутствуют импульсы на выходных шинах fi и fa. При входном токе одной полярности возникающий на выводах интегратора заряд компенсируется токовыми импульсами обратной связи другой полярности и возникают выходные частотные импульсы на одном из выходов f 1 или h.

Одновременно появление выходных импульсов на шинах fi и тг исключено. Элементами, разделяющими полярность входного тока, являются компараторы 22, 23 блока 5 сравнения, пороги срабатывания которых разнесены на величину суммы напряжений пороговых источников 8 и 9, и формирователь импульсов биполярного эталонного тока на мостовом коммутаторе на ключах

10 11-14, способный выдавать в интегратор 3 импульсы токов трех уровней: положительного, отрицательного и нулевого, Импульсы эталонного тока положительной полярности формируются при включении диагональных

15 ключей 11 и 14, а импульсы тока отрицательной полярности - при включении диагональ- ных ключей 12 и 13. Нулевой ток формирователя импульсов обратной связи формируется при включении ключей 13, 14

0 и выключении ключей 11, 12. Наличие трех состояний формирователя импульсов обратной, связи позволяет уравновешивать входной ток только импульсами эталонного тока одной полярности. На фиг. 1, 2 показа5 на фазировка включения инвертирующих и неинвертирующих входов компараторов и прямых и инверсных выходов триггеров параллельного регистра для случая применения аналоговых ключей 11-14, включение

0 которых производится подачей на управляющий вход ключа сигнала лог. О и выключение подачей сигнала лог. 1.

Постоянная времени интегрирующего усилителя-сумматора выбирается из усло5 вия

R4Cs 10TT,

где RA и Сз - номиналы резистора 4 и конденсатора 5;

Тт - период тактовой частоты fr на так0 товом входе регистра 24.

Для устойчивого разделения полярности входного тока сумма напряжения пороговых источников 8 и 9 должна удовлетворять условию

5Unop1 + Unop2 1этТт/С,

где 1Эт - номинал эталонного тока источника 17;

С - номинал конденсатора 2. Выходное напряжение интегрирующе- 0 го усилителя - сумматора на элементах 3-5 в каждом канале описывается выражением

UЈ Uc+Wcr Ucdt

е где Uc- текущее напряжение на выводах . конденсатора 2.

При его отсутствии для положительного входного тока относительно общей точки элементов 1, 2, 8, 9 пилообразное напряжение на выводах конденсатора 2 в среднем

будет уравновешиваться около напряжения Unop2 источника 9, а для отрицательного входного тока - около напряжения Unopi источника 8. Применение интегрирующего усилителя-сумматора позволяет непрерывно чувствовать, среднее значение напряжения интегратора и автоматически сводить его к нулю путем выработки напряжения коррекции Укорр, выделяемого на выводах конденсатора 5. Напряжение коррекции Укорр включено последовательно в контуре: выходы интегратора - источник порогового напряжения - входы компаратора. Поскольку постоянная времени выработки Укорр намного превышает период повторения Uc, определяемый целым числом периодов Тт,

то U

корр

1

о ----- / Uc dt является пракК4 L5 о

тически постоянным напряжением по сравнению с пилообразным переменным напряжением Uc и.выполняет функцию дополнительного управляемого источника порогового напряжения, изменением которого можно компенсировать и уменьшать среднее значение Uc.

В каждом преобразователе устройства применена двусторонняя схема ограничения напряжения на выводах интегратора 2, реализованная на элементах 6-9 и срабатывающая в том случае, когда величина входного тока lex источника 1 превышает величину эталонного тока источника 17, т.е. (lex | эт Напряжение на выводах конденсатора 2 не может превысить напряжения порогового источника 8 или 9 в зависимости от полярности входного тока с точностью до прямого напряжения диода 6 или 7,

В устройстве устойчивость и независимость работы четырех преобразователей ос- нована на независимом протекании эталонного тока одного источника 17 через последовательную цепь соединения вторых диагоналей мостовых коммутаторов 11-14 всех четырех преобразователей. Внутри одного преобразователя неразрывность протекания эталонного тока обеспечивается тем, что в диапазоне линейного преобразования входного тока в пределах эталонный ток протекает либо через диагональные ключи 11, 14 и конденсатор 2, либо через диагональные ключи 12, 13 и конденсатор 2, либо прямо через ключи 13, 14, при этом падение напряжения на второй диагонали мостового коммутатора будет определяться суммой падения напряжения на двух открытых ключах, так как среднее напряжение на выводах интегратора 2 близко к нулю, Когда входной ток,1Вх превышает 1зт, срабатывает схема ограничения напряжения на элементах б - 9 и падение напряжения на второй диагонали мостового коммутатора изменится на величину напряжения ограничения интегратора 2, однако это не приводит к

разрыву последовательной цепи подачи эталонного тока на другие преобразователи.

Таким образом, одной из составляющей положительного эффекта технического ре0 шения является экономия оборудования и мощности потребления трех источников эталонного тока на четыре преобразователя.

Другой составляющей является приме5 нение общего на четыре преобразователя источника питания аналоговых и цифровых элементов, подключенных к общей шине устройства. С этой целью средняя точка соединения вторых диагоналей мостовых

0 коммутаторов второго и третьего преобразователей подключена к общей шине указанных источников питания. Возможность реализации такой структуры преобразователя, при которой одни и те же элементы

5 разных преобразователей находятся под разными потенциалами напряжений относительно общей шины устройства, достигнута применением усилителей, интегрирующих усилителей сумматоров и компараторов с

0 дифференциальными входами и «МОП аналоговых ключей.

Общий блок сравнения на фиг. 2 по выполняемой функции и выходным сигналам полностью эквивалентен общему блоку

5 сравнения на фиг. 1, однако отличается меньшим числом энергопотребляемых элементов. Входы компаратора 49 последовательно во времени за цикл меньший, чем период Тт тактовой частоты на С-входе па0 раллельного регистра 24, через соответствующие ключи 36-47 аналогового мультиплексора 35 подключаются поочередно к соответствующим входам блока сравнения (см, фиг. 3). При этом компаратор

5 49 последовательно во времени выполняет функцию компараторов 23,22, общего блока сравнения на фиг. 1, Результат сравнения на выходе компаратора 49 подачей сигнала на тактовый вход регистра сдвига 50 по0 следовательно записывается в него и далее после окончания цикла сравнения тактовой частотой fT переписывается в параллельный регистр 24. Необходимо отметить, что к компаратору 49 предъявляются

5 меньшие требования по уровню входных токов, чем к соответствующим компараторам 22, 23 блока сравнения 10 на фиг. 1, так как уменьшено время подключения его входов к выходам интеграторов 2 разных каналов,

Формула изобретения 1. Преобразователь тока ц частоту, являющийся основным и содержащий интегратор, интегрирующий усилитель-сумматор, блок сравнения, первый и второй источники пороговых напряжений, первый и второй элементы И и формирователь импульсов биполярного эталонного тока, выполненный на мостовом коммутаторе, первая диагональ которого подключена к выводам интегратора, первый вывод второй диагонали соединен с первым выходом источника эталонного тока, а первый и второй выводы интегратора подключены к первому и второму выходам источника входного тока и объединены с первым и вторым входами интегрирующего усилителя-сумматора, выход которого подключен к первому информационному входу блока сравнения, а второй вход объединен с входами первого и второго источников пороговых напряжений, выходы которых соединены соответственно с вторым и третьим информационными входами блока сравнения, тактовый выход которого соединен с первыми входами первого и второго элементов И, выходы которых являются соответственно первой и второй выходными шинами, а вторые входы элементов И объединены с первым и вторым управляющими входами мостового коммутатора и подключены к первому и второму выходам блока сравнения соответственно, третий и четвертый выходы которого соединены с третьим и четвертым управляющими входами мостового коммутатора, отличающийся тем, что, с целью повышения функциональной надежности преобразователя, в него введены первый и второй диоды, первый и второй источники напряжения и три дополнительных преобразователя тока в частоту, выполненных аналогично основному, в каждый из которых введены два диода, анод первого из которых и катод второго объединены и подключены к первому выводу интегратора, второй и третий информационные входы блока сравнения соединены соответственно с катодом первого диода и анодом второго диода, а второй вывод второй диагонали мостового коммутатора основного преобразователя тока в частоту соединен с первым выводом второй диагонали мостового коммутатора первого дополнительного преобразователя тока в частоту, второй вывод второй диагонали мостового коммутатора которого является общей шиной, объединен с первыми выводами первого и второго источников напряжения и с первым выводом второй диагонали мостового коммутатора второго дополнительного преобразователя в частоту,

второй вывод второй диагонали мостового коммутатора которого соединен с первым выводом второй диагонали мостового коммутатора третьего дополнительного преоб5 разователя тока в частоту, второй вывод второй диагонали которого соединен со вторым выходом источника эталонного тока и через первый диод подключен ко второму выводу первого источника напряжения, вто0 рой вывод второго источника напряжения через второй диод соединен с первым выходом источника эталонного тока.

2.Преобразователь поп. 1, о т л и ч а ю- щ и и с я тем, что все блоки сравнения

5 совместно образуют общий блок сравнений, выполненный на четырех парах компараторов, параллельном регистре, тактовом генераторе и делителе частоты, при этом инвертирующие входы первой, второй,

0 третьей и четвертой пар компараторов являются соответственно первыми информационными входами общего блока сравнения, неинвертирующие входы первой, второй, третьей и четвертой пары компараторов яв5 ляются соответственно вторыми и третьими информационными входами общего блока сравнения, выход тактового генератора через делитель частоты пЬдключен к тактовому входу регистра и является тактовым

0 выходом общего блока сравнения, причем информационные входы параллельного регистра подключены к соответствующим выходам компараторов пар, а прямые и инверсные выходы параллельного регистра

5 являются соответствующими выходами с первых по четвертые общего блока сравнения.

3.Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что, с целью уменьшения

0 потребляемой мощности, все блоки сравнения образуют общий блок сравнения, выполненный на аналоговом мультиплексоре, компараторе, последовательно-параллельном регистре сдвига, параллельном регист5 ре, тактовом генераторе и устройстве управления, при этом входы мультиплексора являются соответственно первыми, вто- . рыми и третьими информационными входами общего блока сравнения, первый и

0 второй выходы мультиплексора подключены к соответствующим первому и второму входам компаратора, выход которого соединен с информационным входом регистра сдвига, выходы которого подключены к со5 ответствующим входам параллельного регистра, прямые и инверсные выходы которого являются соответствующими с первых по четвертые выходами общего блока сравнения, причем вход устройства управления подключен к выходу тактового

генератора, с первого по четвертый ходу устройства управления, а тактовый

. - ....,....... . A vЈi4Mnr«Ms%Mt nnntfit i

выходы устройства управления подключены к управляющим входам мультиплексора, тактовый вход регистра сдвига подключен к пятому вы- 5 сравнения.

вход параллельного регистра подключен к шестому выходу устройства управления и является тактовым выходом общего блока

ходу устройства управления, а тактовый

. A vЈi4Mnr«Ms%Mt nnntfit i

вход параллельного регистра подключен к шестому выходу устройства управления и является тактовым выходом общего блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь ток-частота с импульсной обратной связью | 1986 |

|

SU1451863A1 |

| Интегрирующий преобразователь тока в код | 1989 |

|

SU1741264A1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1510087A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1559407A2 |

| Аналого-цифровой преобразователь неэлектрических величин | 1985 |

|

SU1403374A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Биполярный преобразователь ток-частота | 1985 |

|

SU1277400A1 |

| Функциональный преобразователь | 1990 |

|

SU1785009A1 |

Изобретение относится к импульсной технике и может быть использовано в радиоэлектронных системах в качестве интегрирующего преобразователя тока в частоту. Цель изобретения - экономия оборудования и снижение мощности потребления при одновременном достижении общего коэффициента передачи по всем каналам преобразования. Устройство содержит четыре преобразователя тока в частоту, в каждом из которых имеются источник 1 входного тока, интегратор 2, интегрирующий усилитель-сумматор, включающий .операционный усилитель 3, резистор 4 и конденсатор 5, первый 6 и второй 7 диоды, первый 8 и второй 9 источники порогового напряжения, формирователь импульсов биполярного эталонного тока на мостовом коммутаторе из четырех аналоговых ключей 11 - 14, первый 15 и второй 16 элементы И, выходы которых образуют выходные шины. Устройство содержит также общие блок сравнения и источник 17 эталонного тока. Общий блок сравнения может быть выполнен на восьми компараторах, параллельном регистре, тактовом генераторе и делителе частоты. Общий блок сравнения может быть также выполнен на мультиплексоре, компараторе, регистре сдвига, устройстве управления, параллельном регистре и тактовом генераторе. В каждом преобразователе применена схема ограничения напряжения на выводах интегратора 2, на элементах 6-9. Вторые диагонали мостовых коммутаторов первого, второго,третьего и четвертого преобразователей соединены последовательно и подключены к общему источнику 17 эталонного тока. Общая точка соединения вторых диагоналей мостовых коммутаторов второго и третьего преобразователей подключена к общей шине источников питания устройства. 2 з.п. ф., 2 ил. О чэ ел СЛ о 4

Авторы

Даты

1991-11-30—Публикация

1989-03-23—Подача