:Ш

-it3W

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор сопротивлений систем промышленного электроснабжения | 1985 |

|

SU1282021A1 |

| Устройство для измерения параметров трехфазной сети | 1985 |

|

SU1307396A1 |

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ МНОГОДВИГАТЕЛЬНОГО ЭЛЕКТРОПРИВОДА | 1992 |

|

RU2071635C1 |

| Цифровой измеритель неуравновешенности напряжений в промышленной сети | 1988 |

|

SU1645915A1 |

| Цифровое устройство для измерения несимметрии напряжений | 1980 |

|

SU993162A1 |

| Устройство для вычисления параметров трехфазной сети | 1986 |

|

SU1376104A1 |

| Устройство для измерения параметров качества электрической энергии трехфазной сети | 1980 |

|

SU1109680A1 |

| Устройство для определения распределения солености воды | 1990 |

|

SU1755157A1 |

| ЦИФРОВОЙ МАЛОГАБАРИТНЫЙ USB ОСЦИЛЛОГРАФ | 2009 |

|

RU2402024C1 |

| АНАЛИЗАТОР КАЧЕСТВА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1999 |

|

RU2145716C1 |

Изобретение касается контроля качества электроэнергии и предназначено для измерения неуравновешенности напряжений. Цель изобретения - повышение томности измерений - достигается благодари введению блока устройств выборки и хранения 5, позволяющего провести измерения по мгновенным напряжениям в сети В опин и тот же момент времени. Измеритель

ks

О KJ &ч --I

Ј

«л.

3 1

состоит из последовательно соединенных масштабного преобразователя 1 фильтра первой гармоники 2, выделителя действующего значения модуля- напряжения 3, блока устройств выборки и хранения k, аналогового коммутатора 5 и аналого-цифрового преобразователя (ЛЦП} 6, параллельно соединенных блока управления 7, блока буферного оперативного запоминаю

Изобретение относится к контролю качества электроэнергии и предназначено для измерения неуравновешенности напряжений трехфазной сети.

Цель изобретения - повышение точности измерений.

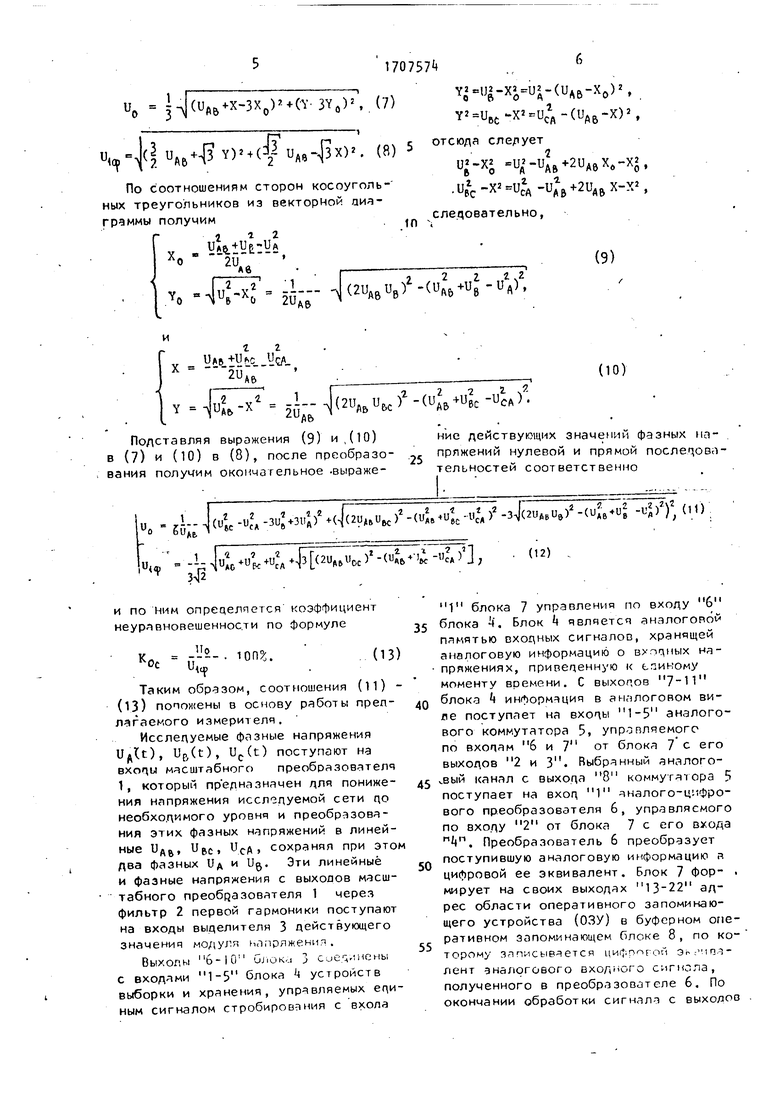

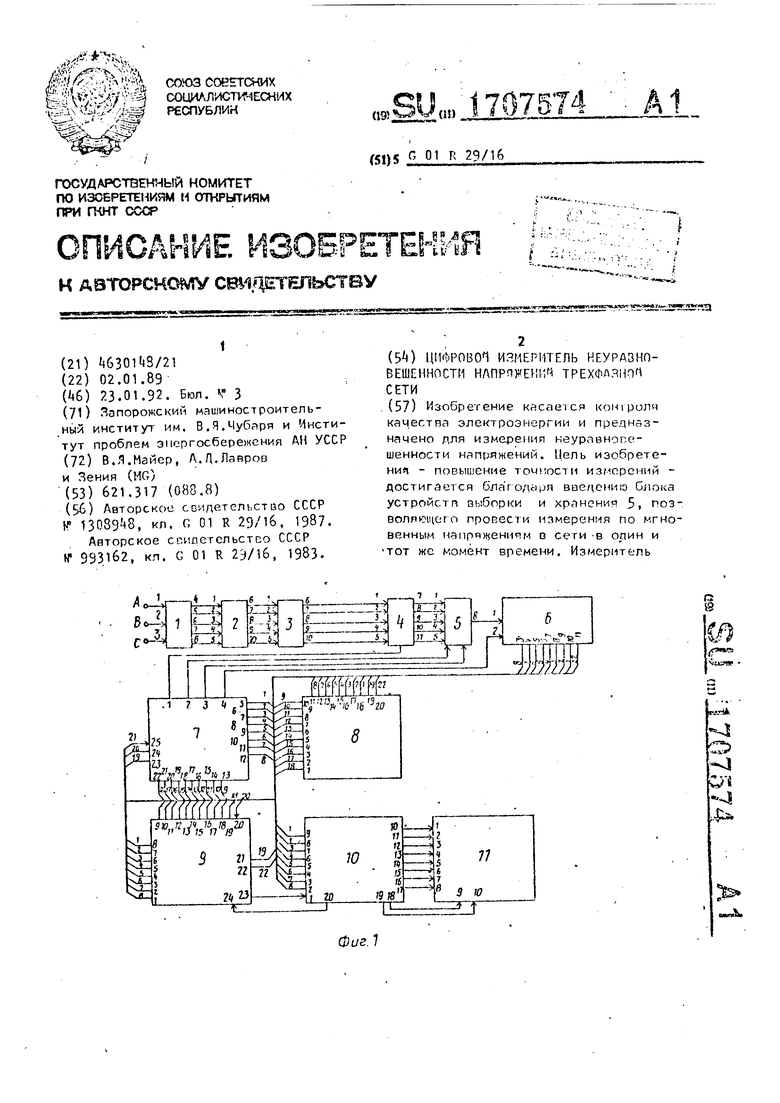

На фиг.1 представлена структурная схема предлагаемого измерителя} на фиг.2 - векторная диаграмма, поясняющая принцип измерения действующих значений симметричных составляющих напряжения.

Цифровой измеритель неуравновешенности напряжений содержит последовательно соединенные масштабный преобразователь 1, фильтр 2 первой гпрмони;;и, выделитель 3 действующего значения модуля напряжения, блок i устройсть выборки и хранения и ана- .логовый коммутатор 5, которые через аналого-цифровой преобразователь 6 связаны с параллельно соединенными блоком 7 управления, буферным оперативным запоминающим блоком 8,вычислительным блоком 9 и блоком 10 управления индикацией, подключенным к блоку 11 индикации.

Измеритель работает следующим образом.

При измерении симметричных составляющих используется тот факт, что напряжение примой последовательности основной частоты трехфазной сети зависит от абсолютных величин трех линейных напряжений основной частоты, а напряжение нулевой последователь- ности основной частоты - от трех фаз ных напряжений основной частоты. В этой связи, по методу Фортескью комплексы ректоров напряжений нулевой и прямой последоратепьностей можно с сот зет стаем о -л ь

5 (UA +

U

В

ис).

0757V .. д

щег о устройства (ОЗУ) 8,, вычислительного блока 9, блока управления индикацией 10 и блока индикации 11. Плок управления 7 связан с блоком устройств выборки и хранения b t аналоговым коммутатором 5, АЦП 6 и буферным- ОЗУ 8, блок управления индикацией 10 соединен с блоком индика- Ю -Чии П, а аналоговый коммутатор 5 связан с АЦП 6. 2 ил.

), (2)

а

;2

« г.Ъ

;4«

а - е5 а е

т.е. а

. . jJF...

2

-| + Jf;.. -комплексный множи

.. тель;

UA. UR.

Ос- -/ комплексы фазных напряжений,

ЛИ, ивс

- комплексы Линейных напряжений.

Из пектррной диаграммы (фиг. 2) находим аналитическое выражение векторов фазных и линейных напряжений соответственно

УЛ (ида-ХоН Y0,

Ve -xcrJ Y0,

Uс - (X-X0)+j(Y-Ye),

UAS uA6, Vec -x-j Y,

UCft - UAe-X)+j Y .

(3)

(4)

45

50

55

Подставляя выражения (З) в (1) и (4) в (2), после преобразований со- ответстиенно получим

о f (UA6-x-3X0)-f.i(Y-3Y0); (5)

V (22UAB Y +

+ J -J3(f - x)j. (6)

: Из выражений (5) и (6) можно соответственно получить модули напряжений нулевой и .прямой последовательностей

U0 (иА| +х-зх0)+Ог 3Y0), (7)

)U(f ) - (8) 5

По соотношениям сторон косоуголь- ных треугольников из векторной диаграммы получим п Ч г г

Y в У«.1Уг-УА

2илв . .

- Ги1-, Ч (2U (Uft2& +U

отсюда следу

U.-XJ -Ц{

U|fc-X2 A следовательн

Uw+Uf-c

2

UC/L

2U

А&

( „4 1иАЬ-Х

20;b- N

(2U

Подставляя выражения (9) и,(Ю) в (7) и (10) в (8), после преобразования получим окончательное -выраже55

L- ))2- -«с 2-зл1()2-( -Фг) ; оо;

АЬ

«« - v 3 (2uft6 t.0c - ( + ,Д -ис2А) ; Т

и по ним опрецелпется коэффициент неуравновешенности по формуле

К с П --1°П

Таким образом, соотношения (11) 03) попожены в основу работы предлагаемого измерителя.

Исследуемые фазные напряжения ), UB(t), Uc(t) поступают на вхоцы масштабного преобразователя 1, который предназначен для понижения напряжения исследуемой сети до необходимого уровня и преобразования этих фазных напряжений в линейные UAU, Uвс исд, сохраняя при это два фазных 11д и Ug. Эти линейные и фазные напряжения с выходов масштабного преобразователя 1 через фильтр 2 первой гармоники поступают на входы выделителя 3 действующего значения модуля напряжения .

Выхог.ы 6-10 Слок.и 3 cue.vmcHbi с входами 1-5 блока k устройств выборки и хранения, управляемых единым сигналом стробиров-зния с вхола

)

VI Е112-YS -(П.. -Y 1

Te 1V ло UA UAB ло; (г

СА

О 6 Y -UBC-X Uc -(UAB-X)f

отсюда следует

U.-XJ -Ц{-и +2иАвХв-Х,

U|fc-X2 A-UAV2lWX-X2. следовательно,

(9)

(Ю)

AbUE c

f-(uf

+U

25

ние действующих значений фазных напряжений нулевой и прямой последовательностей соответственно

(12)

40

50

8 коммутатора 5 1 аналого-цифро 1 блока 7 управления по входу 6 35 блока . Блок является аналоговой памятью входных сигналов, хранящей аналоговую информацию о входных на- пряжениях, приведенную к тайному моменту времени. С выходов 7-11 блока k информация в аналоговом ви- яе поступает на входы 1-5 аналогового коммутатора 5, управляемого по входам 6 и 7 от блока 7 с его выходов 2 и 3. Выбранный аналого- 45 «.вый канал с выхода поступает на вход вого преобразователя 6, управляемого по входу 2 от блока 7 с его входа nkn. Преобразователь 6 преобразует поступившую аналоговую информацию а цифровой ее эквивалент. Блок 7 фор- . мирует на своих выходах 13-22 адрес области оперативного запоминающего устройства (ОЗУ) в буферном оперативном запоминающем блоке 8, по которому записывается Эр.- чпа- лент аналогового входного сигнала, полученного в преобразователе 6. По окончании обработки сигнала с выходов

10, 9, 8, 7, 6, 5, b, 3 преобразователя 6 цифровой эквивалент аналогового сигна па поступает на входы 18, 17, 16, 15, 1, 13, 12, 11 блока 8, а с выхода 11 преобразователя 6 на вход 20 блока 8 заводят сигнал записи в блок 8 полученной информации. После этого следует выбор в компараторе 5 очередного аналогового канала с повторением алгоритма, аналогичного описанному. Режим намерения заканчивается после обработки всех аналоговых каналов. Об окончании режима измерения блок 7 оповещает вычислитель- ный блок 9 сигналом с выхолэ 2 по входу 20 блока 9, и система переходит в режим вычисления.

После получения от блока 7 сигнал а окончания измерений .блок 9 переводит систему в режим вычисления - выраба-. тывает на своем выходе 19 сигнал блокировки от дальнейшего несанкционированного запуска режима измерения,

подаваемый на вход 25 блока 7, и блок 8 переходит в режим ожидания. В режиме вычисления блок 9 получает доступ к всей области ОЗУ блока 8 путем установки адресов на своих выходах 18, 17, 16, 15, , 13, 12, 11, 10, 9, 9 обмен данными происходит по двунаправленной шине данных - входы-выходы 8, 7, 6, 5, , 3, 2, 1 блока 9. Сигнал записи Формируется п блоке 9 на выходе 22, а считывания - на выхопе 21, и подают их соответственно на входы 20 и 19 блока 8, Блок 9 производит вычисления по формулам (11) - (13) программным способом. В процессе счета полученные резул таты сохраняются в блоке 8. По окончании процесса счета блок 9 управляет перепачей результатов вычисления побайтно из блока 8 в блок 10 управления индикацией. Блок 9 на своем выходе 23 формирует сигнал записи байта результата в блок 10, Байт информации, в блок 10 проходит на входы 9, 8, 7, 5, А, 3, 2, а сигнал записи - на вход 1. Об ркончании процесса приема байта информации блок 10 с выхода 20 информирует блок 9 по входу 2V. Тадо преобразователя через последователь но соединенные фильтр первой гармоники, выделитель действующего значе ния модуля напряжения и блок устройств выборки и хранения соединены с соответствующими входами коммутатора, выход которого подключен к входу .аналого-цифропого преобразователя, информационные выходы которого соединены двунаправленной шиной данных с соответствующими информационными входами-выходами блок управления, буферного оперативного запоминающего блока и вычислительно го блока, адресные выходы которых

ким образом, происходит передача веси

вычисленной информации. Блок 10 про- 5 соответственно объединены межпу соидподит обработку всей принятой ин- оой шиной адреса.

5

0

5

формации и производит вывод ее в блок 11 индикации. Информация для вывода с выхолов 10, 11, 12, 13, 1, 15, 16, 17 блока 10 передается на входы 1, 2, 3, 4, 5, 6, 7, 8 бло- кч 11. Управление выводом информации в блоке 11 производится по его входам 9 и МО с выходов 18 и 19 блока 10.

Кроме Ue , , измеритель позволяет рассчитывать при необходимости значения углов, определяющих направления векторов U и 0.,, а также выводить на печать модули трех линейных и двух фазных напряжений сети и обрабатывать другие данные.

-.

Формула изобретения

Цифровой измеритель неуравновешенности напряжений трехфазной сети, содержащий масштабный преобразователь, последовательно соединенные фильтр первой гармоники и выделитель действующего значения модуля напряжения переменного тока, блок управления, управляющие пыходы которого соединены с командными входами коммутатора, аналого-цифрового преобразова0 теля, буферного оперативного запоминающего блока и вычислительного блока, и Ппок инпикации, соепиненный через его блок управления с шино данных,, отличающийся

5 тем, что, с целью повышения точности измерений, в него пополнительно введен блок устройств выборки и хранения, который связан с блоком управ- ления,. причем выходы млсштабного

о преобразователя через последовательно соединенные фильтр первой гармоники, выделитель действующего значения модуля напряжения и блок устройств выборки и хранения соединены с соответствующими входами коммутатора, выход которого подключен к входу .аналого-цифропого преобразователя, информационные выходы которого соединены двунаправленной шиной данных с соответствующими информационными входами-выходами блока управления, буферного оперативного запоминающего блока и вычислительного блока, адресные выходы которых

5

0

J

Ц

CA

;

| Способ очистки сульфоновых кислот | 1926 |

|

SU13089A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровое устройство для измерения несимметрии напряжений | 1980 |

|

SU993162A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-01-23—Публикация

1989-01-02—Подача