к:

N:

Изобретение относится к вычислительной технике, может быть использовано для моделирования объектов или процессов, описываемых сетями Петри, и является усовершенствованием изобретения по. авт.св. N2 1633430.

Цель изобретения - расширение функциональных возможностей устройства за счет моделирования сетей Петри с задержкой передачи фишек из вершин-переходов.

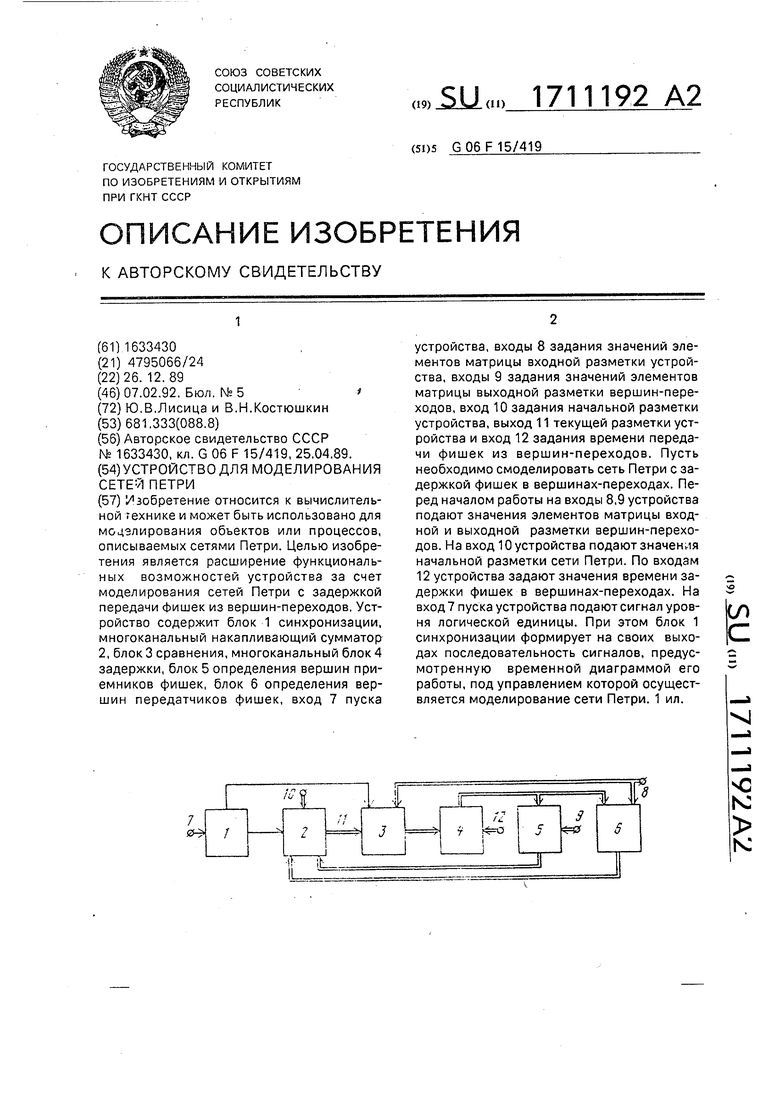

На чертеже представлена функциональная схема устройства.

Устройство содержит блок 1 синхронизации, многоканальный накапливающий сумматор 2, блок 3 сравнения, многоканальный блок 4 задержки, блок 5 определения вершин приемников фишек, блок 6 определения вершин передатчиков фишек, вход 7 пуска устройства, входы 8 задания значений элементов матрицы входной разметки устройства, входы 9 задания значений элементов матрицы выходной разметки вершин-переходов, вход 10 задания начальной разметки устройства, выход 11 текущей разметки устройства и вход 12 задания времени передачи фишек из вершин-переходов.

Устройство работает следующим образом.

Пусть необходимо смоделировать сеть Петри с задержкой фишек в вершинах-переходах.

Перед началом работы на входы 8,9 устройства подают значения элементов матрицы входной и выходной разметки вершин-переходов. На вход 10 устройства подают значения начальной разметки сети Петри. При этом каналы многоканального накапливающего сумматора 2 устанавливаются в исходное состояние (тем самым задается количество фишек в каждой соответствующей номеру канала вершине- месте). По входам 12 устройства задают значения времени задержки фишек в вершинах-переходах. При этом каналы блока 4 устанавливают заданное время задержки. На вход 7. пуска устройства подают сигнал уровня логической единицы. При этом блок-1 синхронизации формирует на своих выходах последовательность сигналов, предусмотренную временной диаграммой его работы.

Блок 1 синхронизации формирует импульс уровня логической единицы на своем первом выходе. При этом блок 3 сравнения формирует потенциалы уровня логической единицы на тех своих выходах признаков не меньше, которые соответствуют информационным входам группы, для которых значение каждого разряда информационного входа не меньше (т.е. больше или равно) значения соответствующего разряда информационного входа группы (тем самым определяются вершины-переходы, для которых выполняются условия переходов). При этом каналы блока 4 задерживают поступившую на их входы информацию на заданное время (тем самым моделируется процесс задержки передачи фишек из вершин-перехо0 дов). При этом блок 6 определения вершин передатчиков фишек формирует потенциалы уровня логической единицы на тех своих выходах, номера которых соответствуют вершинам-местам, передающим фишки, а

5 блок 5 определения вершин приемников фишек формирует потенциалы уровня логической единицы на тех своих выходах, номера которых соответствуют вершинам-местам, принимающим фишки.

0 Через время, достаточное для выполнения указанных операций, блок 1 синхронизации формирует импульс уровня логической единицы на своем втором выходе. При этом каналы сумматора 2 уменьша5 ют накопленные ранее значения на величины, поступившие по их входам вычитаемых и одновременно увеличивают указанные значения на величины, поступившие по их входам слагаемых (тем самым осуще0 ствляется моделирование процессов передачи (операции вычитания) и приема (операция сложения) фишек из вершин-мест (в вершины-места).

Через время, достаточйое для выполне5 ния указанных операций, блок 1 синхронизации повторяет выдачу импульса уровня логической единицы на своем первом выходе (при этом работа устройства повторяется). Формула изобретения

0 Устройство для моделирования сетей Петри по авт.св. № 1633430, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения моделирования сетей

5 Петри с задержкой передачи фишек из вершин-переходов, в него введен многоканальный блок задержки, причем М-й выход признака Не меньше блока сравнения (М-1,„ВП; ВП - количество вершин-перехо0 дов в сети Петри) подключен к информационному входу М-го канала многоканального блока задержки, информационный выход М- го канала которого подключен к входам опроса М-й вершины-перехода блока

5 определения вершин приемников фишек и блока определения вершин передатчиков фишек, вход задания времени передачи фишек из вершин-переходов устройства подключен к входу установки каналов многоканального блока задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетей Петри | 1989 |

|

SU1711191A2 |

| Устройство для моделирования сетей Петри | 1989 |

|

SU1727138A1 |

| Устройство для моделирования сетей Петри | 1989 |

|

SU1633430A1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ СЕТЕЙ ПЕТРИ | 1996 |

|

RU2126171C1 |

| Устройство для моделирования графов Петри | 1987 |

|

SU1483460A1 |

| Устройство для моделирования графов Петри | 1987 |

|

SU1483459A1 |

| Устройство для моделирования сетей Петри | 1990 |

|

SU1709348A1 |

| Устройство для моделирования графов Петри | 1986 |

|

SU1405070A1 |

| Устройство для исследования сетей Петри | 1987 |

|

SU1432547A2 |

| Устройство для моделирования графов Петри | 1986 |

|

SU1314350A1 |

Изобретение относится к вычислительной технике и может быть использовано для мо злирования объектов или процессов, описываемых сетями Петри. Целью изобретения является расширение функциональных возможностей устройства за счет моделирования сетей Петри с задержкой передачи фишек из вершин-переходов. Устройство содержит блок 1 синхронизации, многоканальный накапливающий сумматор 2, блок 3 сравнения, многоканальный блок 4 задержки, блок 5 определения вершин приемников фишек, блок 6 определения вершин передатчиков фишек, вход 7 пуска устройства, входы 8 задания значений элементов матрицы входной разметки устройства, входы 9 задания значений элементов матрицы выходной разметки вершин-переходов, вход 10 задания начальной разметки устройства, выход 11 текущей разметки устройства и вход 12 задания времени передачи фишек из вершин-переходов. Пусть необходимо смоделировать сеть Петри с задержкой фишек в вершинах-переходах. Перед началом работы на входы 8,9 устройства подают значения элементов матрицы входной и выходной разметки вершин-переходов. На вход 10 устройства подают значения начальной разметки сети Петри. По входам 12 устройства задают значения времени задержки фишек в вершинах-переходах. На вход 7 пуска устройства подают сигнал уровня логической единицы. При этом блок 1 синхронизации формирует на своих выходах последовательность сигналов, предусмотренную временной диаграммой его работы, под управлением которой осуществляется моделирование сети Петри. 1 ил. + Ё

| Устройство для моделирования сетей Петри | 1989 |

|

SU1633430A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-07—Публикация

1989-12-26—Подача