Изобретение относится к вычислительной технике и может быть использовано для моделирования систем, описываемых сетями Петри с запрещающими дугами.

Известно устройство для моделирования сетей Петри, содержащее блок задания матрицы входной разметки вершин-переходов, блок задания матрицы выходной разметки вершин-переходов, блок синхронизации, блок сравнения, многоканальный накапливающий сумматор, блок определения вершин-приемников меток и .блок определения вершин-передатчиков меток.

.Однако известное устройство не позволяет моделировать сети Петри с запрещаю- щими дугами.

Целью изобретения является расширение функциональных возможностей устройства за счет моделирования сетей Петри с Запрещающими дугами.

Поставленная цель достигается тем. что устройство для моделирования сетей Петри, содержащее блок синхронизации, блок вычисления текущей разметки и блок определения возбужденных переходов, содержит также блок определения запрещенных переходов и блок логического умножения.

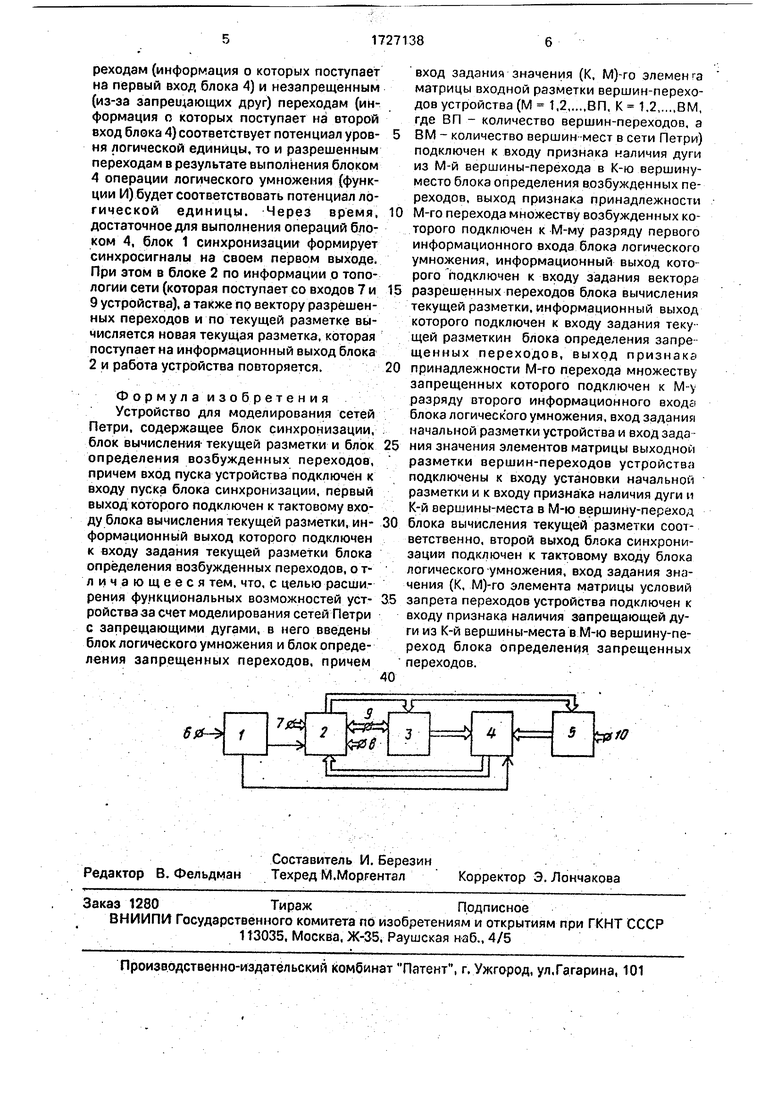

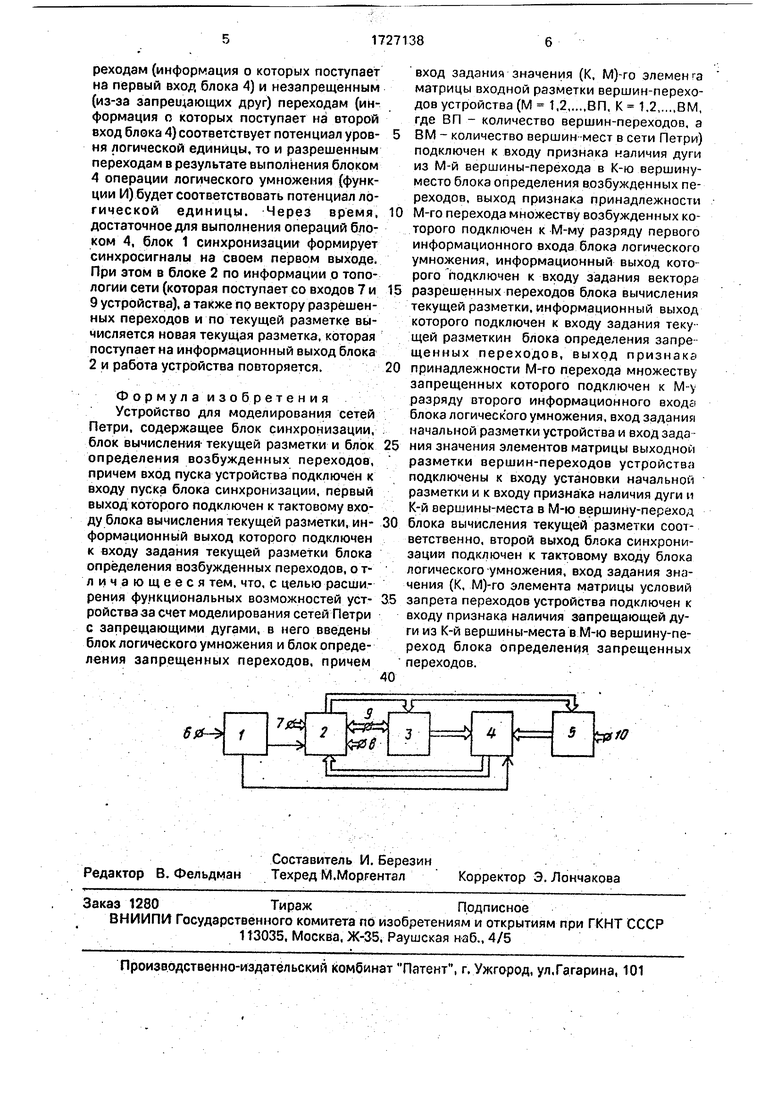

На чертеже представлена функциональная схема устройства для моделирования сетей Петри.

Устройство для моделирования сетей Петри содержит блок 1 синхронизации, блок 2 вычисления текущей разметки, блок 3 опVI

ГО XI

со

00

ределения возбужденных переходов, блок 4 логического умножения, блок 5 определения запрещенных переходов, вход 6 пуска, вход 7 задания значений элементов матрицы выходной разметки вершин-переходов, вход 8 задания начальной разметки, вход 9 задания элементов матрицы входной разметки вершин-переходов и вход 10 задания значений элементов матрицы условий запрета переходов устройства, причем вход б пуска устройства подключен к входу пуска блока 1 синхронизации, первый выход которого подключен к тактовому входу блока 2 вычисления текущей разметки, информационный выход которого подключен к входу задания текущей разметки блока 3 определения возбужденных переходов и к входу задания текущей разметки блока 5 определения запрещенных переходов, вход 9 задания значений (К, М)-го элемента матрицы входной разметки вершин-переходов устройства (М 1,2ВП, К 1,2,...,ВМ, где

ВП - количество вершин-переходов, а ВМ.- количество вершин-мест в сети Петри) подключен к входу признака наличия дуги из М-й вершины-перехода в К-ю вершину-место блока 2 вычисления текущей разметки и к входу признака наличия дуги из М-й вершины-перехода в К-ю вершину-место блока 3 определения возбужденных переходов, выход признака принадлежности М-то перехода множеству возбужденных которого подключен к М-у разряду первого информационного входа блока 4 логического умножения, информационный выход которого подключен к. входу задания вектора разрешенных переходов блока 2 вычисления текущей разметки, выход признака принадлежности М-ro перехода множеству запрещенных блока 5 определения запре- щенных переходов подключен к М-у разряду второго информационного входа блока 4 логического умножения, вход 8 задания начальной разметки устройства и вход 7 зада- ния значений элементов матрицы выходной разметки вершин-переходов устройства подключены к входу установки начальной разметки и к входу признака наличия дуги из К-й вершины-места в М-ю вершину-переход регистрирующего блока 2 вычисления текущей разметки соответственно, второй выход блока 1 синхронизации подключен к тактовому входу блока 4 логического умножения, вход 10 задания значения (К, М)-го элемента матрицы условий запретов пере- ходов устройства подключен к входу признака наличия запрещающей дуги из К-й рершины-места в М-ю вершину-переход блока 5 определения запрещенных переходов.

Устройство работает следующим образом.

На вход 6 пуска устройства подают импульс уровня логической единицы. Под действием синхросигналов с первого выхода блока 1 синхронизации информация о текущей разметке с информационного выхода блока 2 вычисления текущей разметки поступает на входы задания текущей разметки блока 3 определения возбужденных переходов и блока 5 определения запрещенных, переходов. В первом цикле работы устройства такой информацией является информация о начальной разметке, поступающая со входа 8 задания разметки на вход установки начальной разметки блока 2. В блоке 3 определения возбужденных переходов по значению текущей разметки (в первом цикле - начальной) и информации об элементах матрицы входной разметки вершин-переходов, поступающей со входа 9 устройства на вход признака наличия дуги из М-й вершины-перехода в К-ю вершину-место блока 3 выбираются те вершины-переходы, входная разметка которых и текущая разметка (в первом цикле - начальная) позволяют выполнить переход в обычном смысле, т.е. без учета наличия запрещающих дуг. При этом возбужденному в обычном смысле переходу на выходе признака принадлежности М-го перехода множеству возбужденных блока 3 (и, следовательно, на первом входе блока 4) соответствует потенциал уровня логической единицы.

В блоке 5 определения запрещенных переходов по значению текущей разметки (в первом цикле- начальной)и информации об элементах матрицы условий запрета переходов, поступающей со входа 10 устройства на вход признака наличия запрещающей дуги из К-й вершины-места в М-ю вершину-переход блока 5, выбираются те вершины-переходы, которые не могут сработать из-за наличия в текущей разметке (в первом цикле - начальной) меток в вершинах-местах, из которых ведут запрещающие дуги в эти переходы. При этом запрещенному переходу на выходе признака принадлежности М-го перехода множеству запрещенных блока 5 (и, следовательно, на втором входе блока 4) соответствует потенциал уровня логического нуля. Через время, достаточное для выполнения указанных операций, блок 1 снимает сигналы с первого выхода и формирует синхросигналы на своем втором выходе. При этом в блоке 4 реализуется операция логического умножения, и на его информационном выходе формируется вектор разрешенных переходов. Так как и возбужденным в обычном смысле переходам (информация о которых поступает на первый вход блока 4) и незапрещенным (из-за запрещающих друг) переходам (информация о которых поступает на второй вход блока 4) соответствует потенциал уров- ня логической единицы, то и разрешенным переходам в результате выполнения блоком А операции логического умножения (функции И) будет соответствовать потенциал логической единицы. Через время, достаточное для выполнения операций блоком 4, блок 1 синхронизации формирует синхросигналы на своем первом выходе. При этом в блоке 2 по информации о топологии сети (которая поступает со входов 7 и 9 устройства), а также по вектору разрешенных переходов и по текущей разметке вычисляется новая текущая разметка, которая поступает на информационный выход блока 2 и работа устройства повторяется.

Ф о р м у л а и з о б р е т е н и я Устройство для моделирования сетей Петри, содержащее блок синхронизации, блок вычисления-текущей разметки и блок определения возбужденных переходов, причем вход пуска устройства подключён к входу пуска блока синхронизации, первый выход которого подключен к тактовому входу блока вычисления текущей разметки, ин- формэционный выход которого подключен к входу задания текущей разметки блока определения возбужденных переходов, отличающееся тем. что. с целью расширения функциональных возможностей уст- ройства за счет моделирования сетей Петри с запрещающими дугами, в него введены блок логического умножения и блох определения запрещенных переходов, причем

:

вход задания значения (К, М)-го элемента матрицы входной разметки вершин-переходов устройства (М 1,2ВП, К 1,2ВМ,

где ВП - количество вершин-переходов, а ВМ - количество вершин -мест в сети Петри) подключен к входу признака наличия дуги из М-й вершины-перехода в К-ю вершину- место блока определения возбужденных переходов, выход признака принадлежности М-го перехода множеству возбужденных которого подключен к разряду первого информационного входа блока логического умножения, информационный выход которого Подключен к входу задания вектора разрешенных переходов блока вычисления текущей разметки, информационный выход которого подключен к входу задания текущей разметкин блока определения запрещенных переходов, выход признака принадлежности М-го перехода множеству запрещенных которого подключен к М-у разряду второго информационного входа блока логического умножения, вход задания начальной разметки устройства и вход задания значения элементов матрицы выходной разметки вершин-переходов устройства подключены к входу установки начальной разметки и к входу признака наличия дуги и К-й вершины-места в М-ю вершину-переход блока вычисления текущей разметки соответственно, второй выход блока синхронизации подключен к тактовому входу блока логического умножения, вход задания значения (К, М)-го элемента матрицы условий запрета переходов устройства подключен к входу признака наличия запрещающей дуги из К-й вершины-места в М-ю вершину-переход блока определения запрещенных переходов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования графов Петри | 1987 |

|

SU1483459A1 |

| Устройство для моделирования графов Петри | 1987 |

|

SU1483460A1 |

| Устройство для моделирования графов Петри | 1986 |

|

SU1314350A1 |

| Устройство для моделирования сетей Петри | 1989 |

|

SU1711192A2 |

| Устройство для моделирования сетей Петри | 1989 |

|

SU1711191A2 |

| Устройство для моделирования сетей Петри | 1990 |

|

SU1709348A1 |

| Устройство для моделирования графов Петри | 1985 |

|

SU1357972A1 |

| Устройство для моделирования графов Петри | 1990 |

|

SU1714621A1 |

| Устройство для моделирования графов Петри | 1990 |

|

SU1817103A1 |

| Устройство для моделирования графов Петри | 1986 |

|

SU1405070A1 |

Изобретение относится к вычислительной технике и может быть использовано для моделирования систем описываемых сетями Петри с запрещающими дугами. Целью изобретения является расширение функциональных возможностей устройства за счет моделирования сетей Петри с запрещающими дугами. Устройство содержит блок 1 синхронизации-, блок 2 вычисления текущей разметки, блок 3 определения возбужденных переходов, блок 4 логического умножения, блок 5 определения запрещенных переходов, вход 6 пуска, вход 7 задания значений элементов матрицы выходной разметки вершин-переходов, вход 8 задания начальной разметки, вход 9 задания элементов матрицы входной разметки вершин- переходов и вход 10 задания значений элементов матрицы условий запрета переходов устройства. Вектор управления, задающий возбуждение переходов сети в данной маркировке, формируется на выходе блока 4 в результате логического умножения вектора возбужденных переходов и вектора запрещенных переходов. По вектору управления в блоке 2 вычисляется текущая маркировка сети. 1 ил. (Л С

| Устройство для моделирования графов Петри | 1986 |

|

SU1405070A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования сетей Петри | 1989 |

|

SU1633430A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-15—Публикация

1989-06-26—Подача