Изобретение относится к автоматике и вычислительной технике и может быть использовано для вывода информации из ЭВМ,

Цель изобретения - повышение точности устройства.

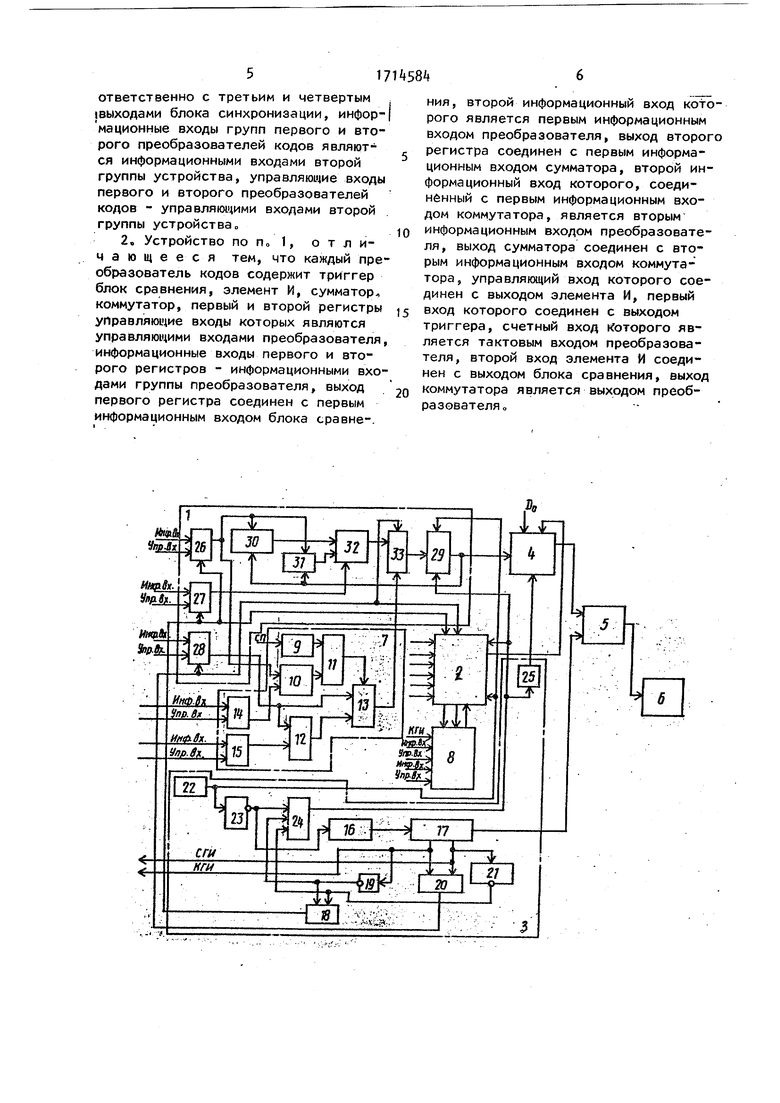

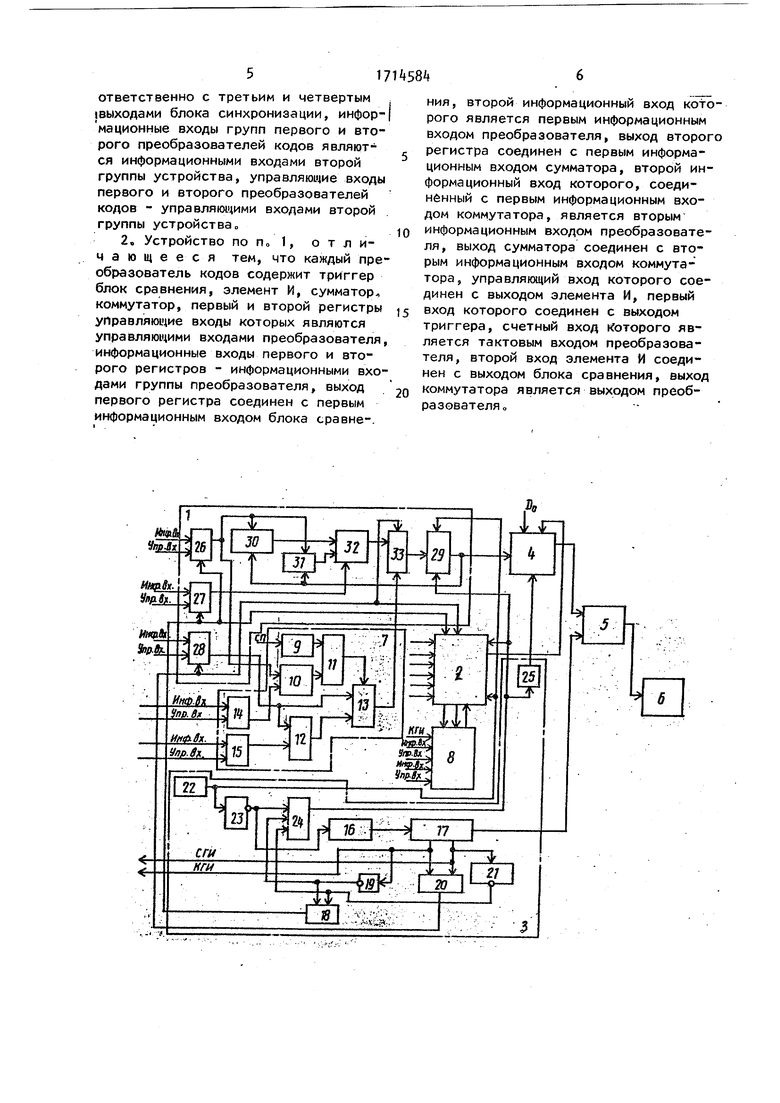

На чертеже приведена структурная схема устройства

Устройство содержит первый 1 и второй 2 формирователи адреса, 6jfoK 3 синхронизации, блок k памяти, формирователь 5 видеосигнала,, телевизионный приемник 6, первый 7 и второй 8 преобразователи кодов

Преобразователь кодов содержит Триггер 9, блок 10 сравнения, элемент И 11, сумматор 12, коммутатор 13 первый 14 и второй 15 регистры.

Блок синхронизации содержит делитель 16 частоты, синхрогенератор 17, элемент ИЛИ 18, инвертор 19, элемент ИЛИ 20, инвертор 21, генератор 22 им

пульсов, инвертор 23, элемент И 2, элемент. 25 задержки.

Формирователь адреса содержит регистры 26 - 29, сумматор 30, вычитатель 31, коммутаторы 32 и 33

Устройство работает следующим образом.

Отображаемая информация заносится в блок k памяти из ЭВМ (не показана) во время обратного хода развертки.

При отображении информации она считывается по адресам, вычисляемым формирователями 1 и 2 адреса. Считанная информация поступает в формирователь 5 видеосигнала, на синхровход которого поступает телевизионный синхросигнал из блока 3 синхронизации Полный телевизионный сигнал с выхода формирователя 5 поступает на видеовход телевизионного приемника 6.

Приведенный на чертеже формирователь адреса позволяет осуществлять

афинные преобразования изображения,, хранимого в блоке памятис В. этом случае адреса считывания, поступаю™ щие На первый и второй адресные входы блока А памяти, вычисляются следующим образом:

x,,j ь; ± a;(j О

(1) у;,. с; ± d;(j - 1),

где i 1, М - номер строки растра, j 1, N - номер элемента в строке;

a,b,c,d - параметры преобразования;

X и у - соответственно номера строки и столбца s блоке 4 памяти для злемеита (i, j), на экране телевизионного приемника

Для каждой строки значение параметра Ь(с) загружается в регистр 28 а параметра a(d) в регистры 26 и 2/ (в регистр 27 знак параметра)

Афинные преобразования позволяют осуществлять перемещение изображения поворот изображения, изменение масштаба изображения.

При уменьшении масштаба изображения мелкие детали, например узкие горизонтальные и вертикальные протяженные отрезки (линии) могут быть утpaMBHNj что приводит к снижению точности устройства с Например, если в соотношении (1) Ь; 0 а 2, то для каждой строки будут утрачены эламен ы 1. 3., 5 . . -.

Для того, чтобы исключить потерю информации, в устройство введены преобразователи 7 и 8 кодов.

В приведенном выше примере преобразователь 7 для каждой четной строки увеличивает коэффициент Ь; на единицу (единица записывается в регистр 15)«На входах . коммутатора 13 присутствуют коды bj и b + 1, выбор которых осуществляется сигналом с выхода элемента И 11. При этом возможны следующие ситуации:

если а-ь2 (двойка записана в регистр ), то для четных строк на коммутатора присутствует сигнал bj + 1, а для нечетных

если а; 2, то для любой строки на выходе коммутатора Ь, ,

В этом случае будут утрачены элементы 1, 3, 5о.с в нечетных строках, а элементы О, 2, k „.о в четных 5 Человеческий глаз аппроксимирует пропущенные элементы и потеря информации не произойдет, хотя яркость линий будет меньше исходной

Выбирая коды в регистрах И и 15 0 соответствующим образом, можно регулировать степень /детализации изображения при изменении масштаба

Таким образом, изобретение позволяет исключить потери информации 15 при выполнении афинного преобразова ния графической информации

Формула изобретения

20 « Устройство для отображения графической информации, содержащее первый и второй формирователи адреса, блок синхронизации, блок памяти, формирователь видеосигнала, выход кото25 роге подключен к видеовходу телевизионного приемника, информационный вход формирователя видеосигнала соединен с выходом блока памяти, управлящий вход которого соединен с первым выходом блока синхронизации,второй выход которого подключен к синхровходу формирователя видеосигнала, информационный вход блока памяти является информационным бходом устройдд ства, первый и второй адресные входы

блока памяти соединены с первьми выходами первого и второго формирователей адреса, информационные входы групп которых являются информацион 10 ными входами первой группы устройства, управляющие входы первых групп первого и второго формирователей адреса являются управляющими входами первой группы устройства, управляющие входы вторых групп первого и второго формирователей адреса соединены с выходами группы блока синхронизации, отличающееся тем, что, с целью повышения точности устройства, оно содержит первый и второй преобразователи кодов, выходы которых соединены с информационными входами соответственно первого и второго формирователей адреса, вторые и третьи выходы которых соединены с ,первыми и вторыми информационными входами соответственно первого и второго преобразователей кодов, такХовые входы которых соединены со- . ответственно с третьим и четвертым 1выходами блока синхронизации, информационные входы групп первого и второго преобразователей кодов являются информационными входами второй группы устройства, управляю1чие входы первого и второго преобразователей кодов - управлякячими входами второй группы устройства 2, Устройство по По 1, отличающееся тем, что каждый пре образователь кодов содержит триггер блок сравнения, элемент И, сумматор коммутатор, первый и второй регистры управляю1чие входы которых являются управляющими входами преобразователя информационные входы первого и второго регистров - информационными вхо дами группы преобразователя, выход первого регистра соединен с первым информационным входом блока еравне-. ния, второй информационный вход Kotoрого является первым информационным входом преобразователя, выход второго регистра соединен с первым информационным входом сумматора, второй информационный вход которого, соединённый с первым информационным входом коммутатора, является вторым информационным входом преобразователя, выход сумматора соединен с вторым информационным входом коммутатора, управляющий вход которого соединен с выходом элемента И, первый вход которого соединен с выходом триггера, счетный вход кйторого является тактовым входом преобразователя, второй вход элемента И соединен с выходом блока сравнения, выход коммутатора является выходом преобразователя

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство отображения информации на экране телевизионного индикатора | 1986 |

|

SU1425768A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1441452A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1357998A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1508272A1 |

| Устройство для отображения информации на телевизионном индикаторе | 1987 |

|

SU1495845A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1980 |

|

SU959143A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1981 |

|

SU1043731A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1439671A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для отображения информации на телевизионном индикаторе | 1983 |

|

SU1091216A1 |

Изобретение относится к автома-i тике и вычислительной технике и может' быть использовано для вывода информации из ЭВМ. Цель изобретения - повышение точности устройства, которая достигается введением первого и второго преобразователей кодов и соответствуняцих функциональных связей, а также выполнением преобразователя кодов. Изобретение позволяет исключить потери информации при выполнении афинного преобразования графической информации, 1 з,п. ф-лы, 1 ил.

| Устройство для отображения информации | 1982 |

|

SU1038965A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1992-02-23—Публикация

1989-11-09—Подача