IS 1819

U

4

СО

со

9д

M1

Изобретение относится к вычисли- тельной технике и автоматизации и может быть использовано для вывода графической информации на .ЭВМ.

Целью изобретения является повышение достоверности отображения информации.

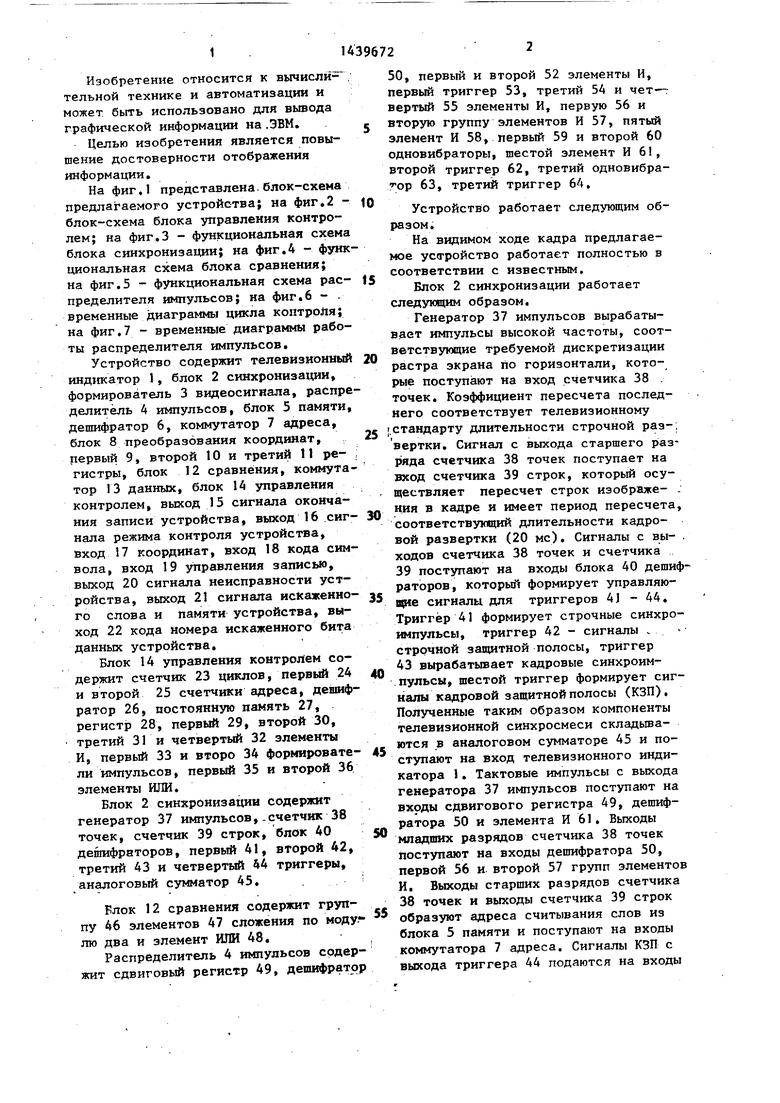

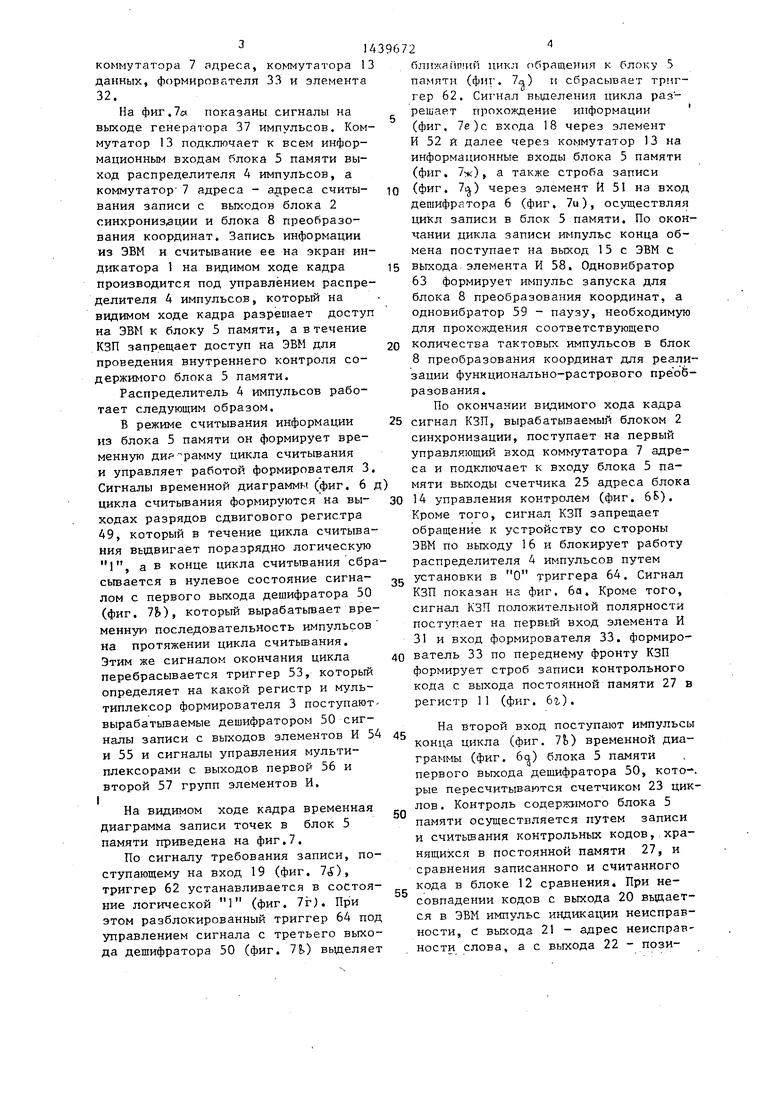

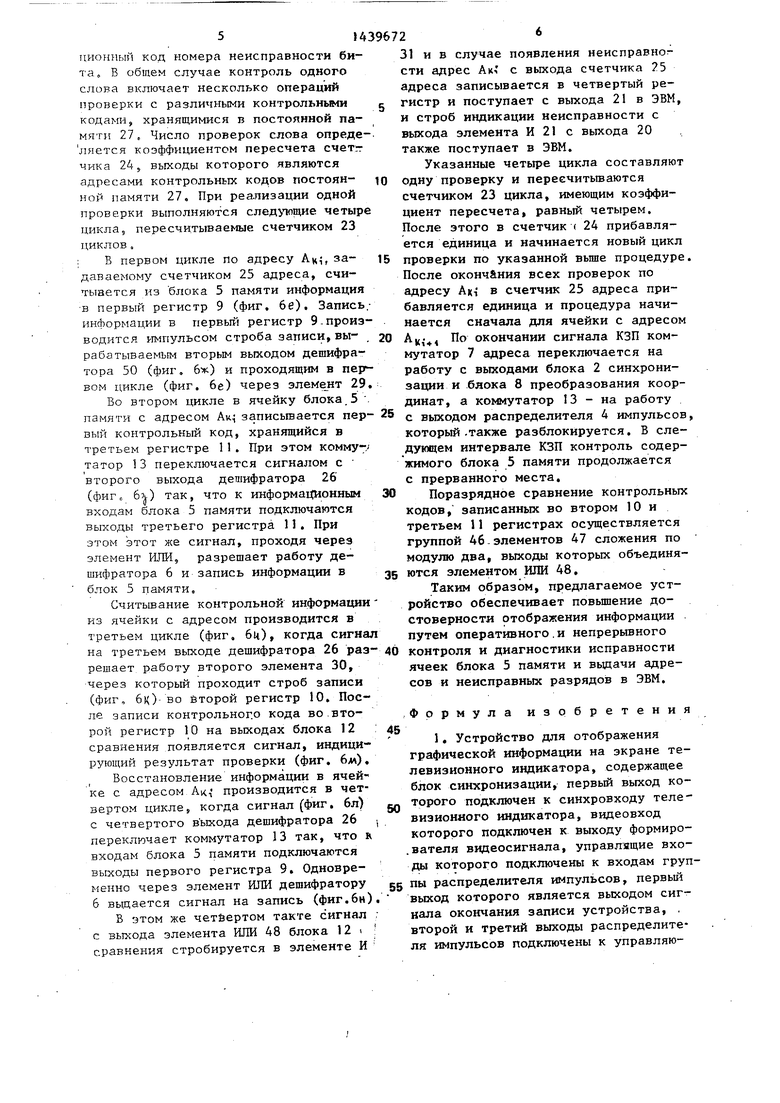

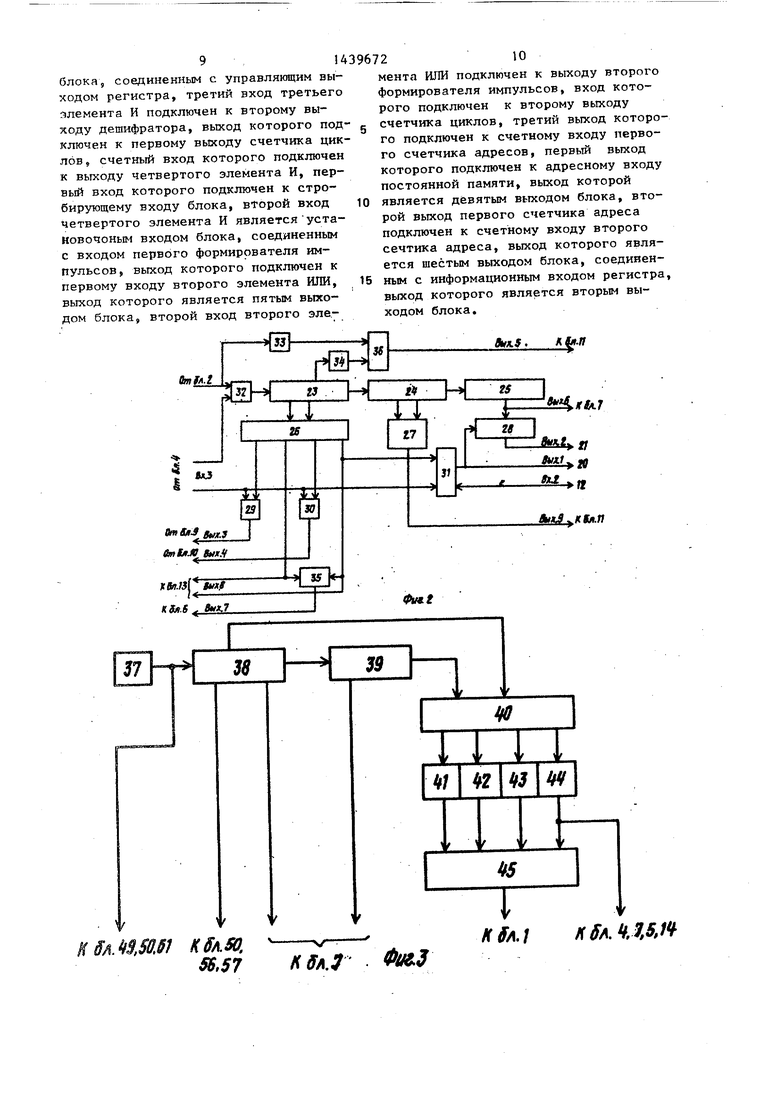

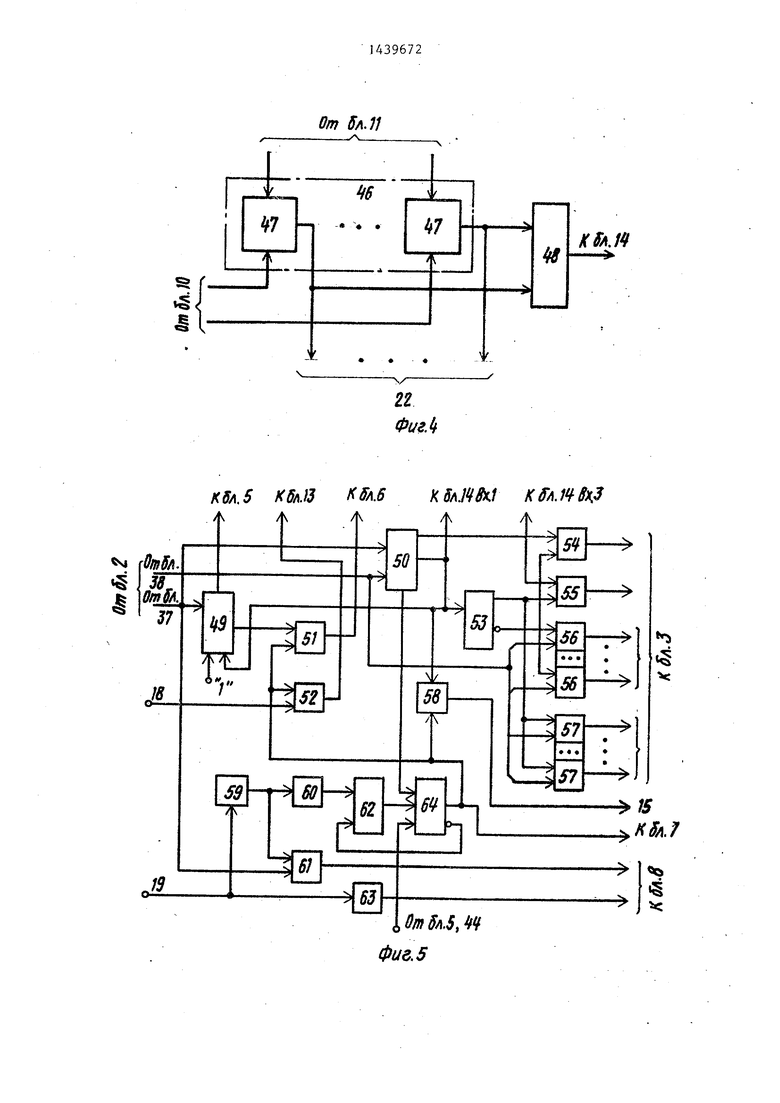

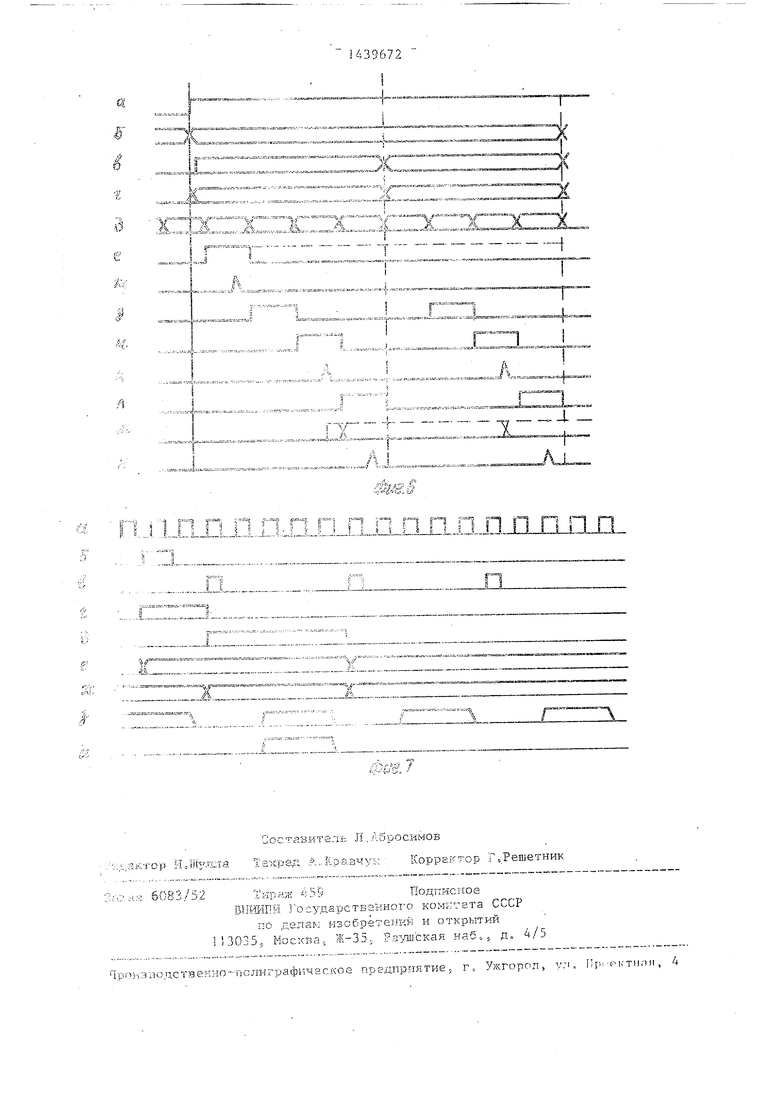

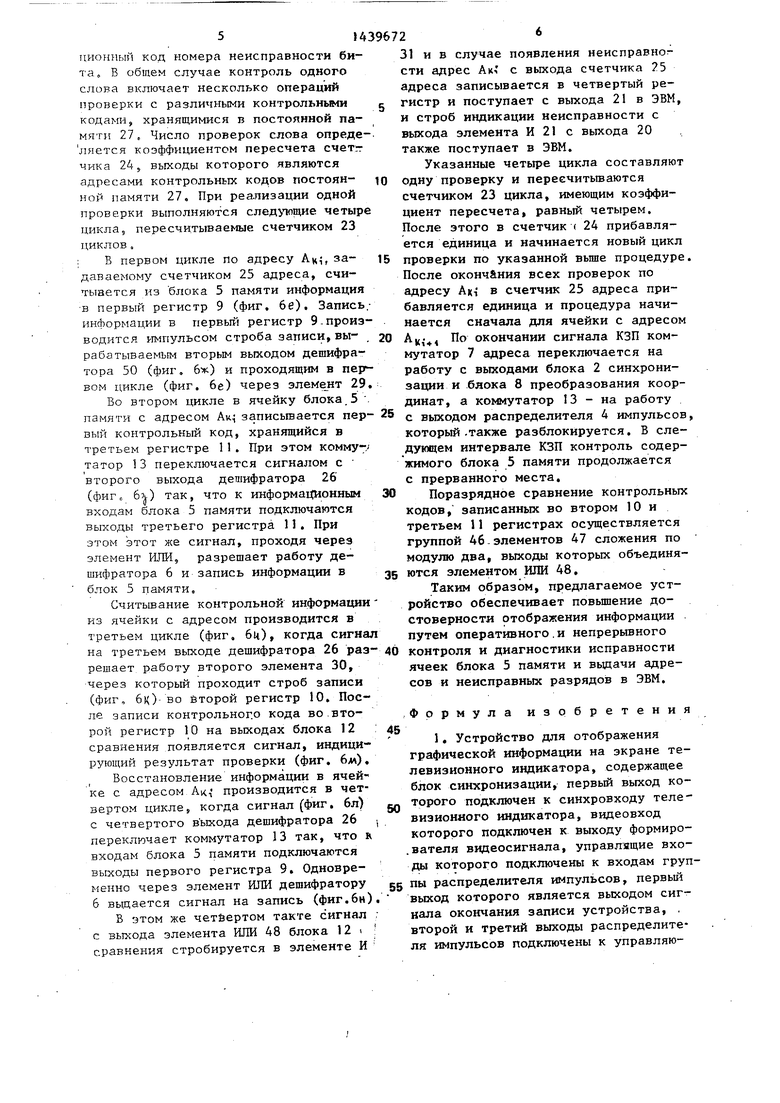

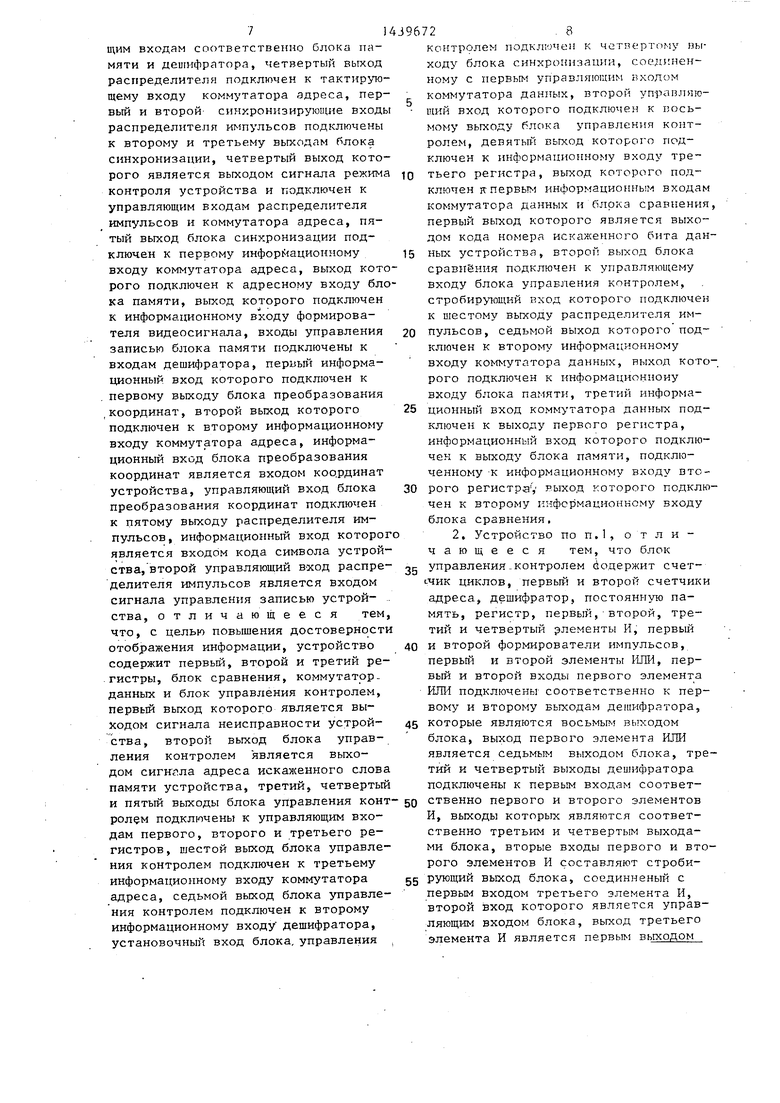

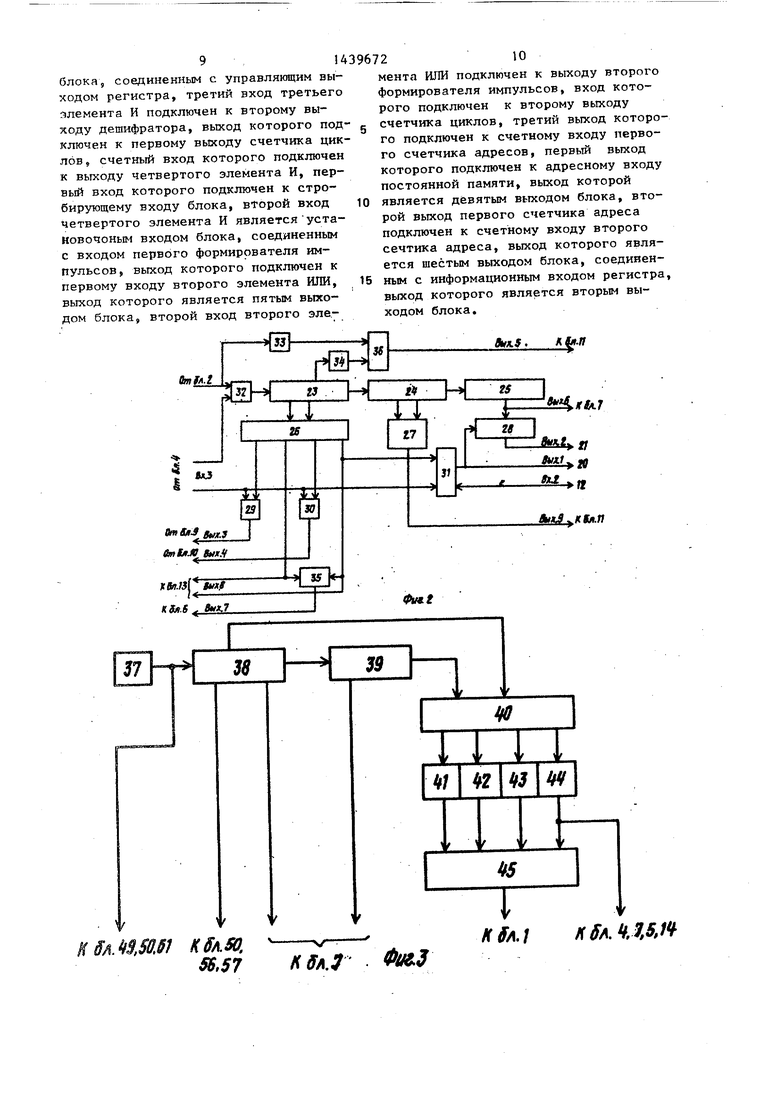

На фиг,1 представлена.блок-схема предлагаемого устройства; на фиг.2 - блок-схема блока управления контролем; на фиг.З - функциональная схема блока синхронизации; на фиг.4 - функциональная схема блока сравнения; на фиг.З - функциональная схема распределителя импульсов; на фиг.6 - . временные диаграммы цикла контроля; на фиг.7 - временные диаграммы работы распределителя импульсов.

Устройство содержит телевизионный индикатор 1, блок 2 синхронизации, формирователь 3 видеосигнала, распределитель 4 импульсов, блок 5 памяти, дешифратор 6, коммутатор 7 адреса, блок 8 преобразования координат, первый 9, второй 10 и третий 11 ре- гистры, блок 12 сравнения, коммутатор 13 данных, блок 14 управления контролем, выход 15 сигнала окончания записи устройства, выход 16 .сигнала режима контроля устройства. Вход 17 координат, вход 18 кода символа, вход 19 управления записью, выход 20 сигнала неисправности устройства, выход 21 сигнала искаженного слова и памяти устройства, выход 22 кода номера искаженного бита данных устройства.

Блок 14 управления контролем содержит счетчик 23 циклов, первый 24 и второй 25 счетчики адреса, дешифратор 26, постояннзто память 27, регистр 28, первый 29, второй 30, третий 31 и четвертый 32 элементы И, первый 33 и второ 34 формирователи импульсов, первый 35 и второй 36 элементы ИЛИ.

Блок 2 синхронизации содержит генератор 37 импульсов,.счетчик 38 точек, счетчик 39 строк, блок 40 дешифраторов, первый 41, второй 42, третий 43 и четвертый 44 триггеры, аналоговый сумматор 45.

Елок 12 сравнения содержит группу 46 элементов 47 сложения по модулю два и элемент ИЛИ 48.

Распределитель 4 импульсов содержит сдвиговый регистр 49, дешифратор

5

0

5

0

5

0

5

0

5

50, первый и второй 52 элементы И, первый триггер 53, третий 54 и четвертый 55 элементы И, первую 56 и вторую группу элементов И 57, пятый элемент И 58, первый 59 и второй 60 одновибраторы, шестой элемент И 61, второй триггер 62, третий одновибра- тор 63, третий триггер 64,

Устройство работает следующим образом.

На видимом ходе кадра предлагаемое устройство работает полностью в соответствии с известным.

Блок 2 синхронизации работает следующим образом.

Генератор 37 импульсов вырабатывает импульсы высокой частоты, соответствующие требуемой дискретизации растра экрана по горизонтали, которые поступают на вход счетчика 38 . точек. Коэффициент пересчета последнего соответствует телевизионному .стандарту длительности строчной раз-, вертки. Сигнал с выхода старшего разряда счетчика 38 точек поступает на вход счетчика 39 строк, который осуществляет пересчет строк изображе- : ния в кадре и имеет период пересчета, соответствующий длительности кадровой развертки (20 мс). Сигналы с вы- . ходов счетчика 38 точек и счетчика 39 поступают на входы блока 40 дешифраторов, который формирует управляющие сигналы для триггеров 41 - 44. Триггер 41 формирует строчные синхро- 1а4пульсы, триггер 42 - сигналы . строчной защитной полосы, триггер 43 вырабатывает кадровые синхроимпульсы, шестой триггер формирует сигналы кадровой защитной полосы (КЗП). Полученные таким образом компоненты телевизионной синхросмеси складываются в аналоговом сумматоре 45 и поступают на вход телевизионного индикатора J. Тактовые импульсы с выхода генератора 37 импульсов поступают на входы сдвигового регистра 49, дешифратора 50 и элемента И 61. Выходы младших разрядов счетчика 38 точек поступают на входы дешифратора 50, первой 56 и. второй 57 групп элементов И. Выходы старших разрядов счетчика 38 точек и выходы счетчика 39 строк образуют адреса считывания слов из блока 5 памяти и поступают на входы коммутатора 7 адреса. Сигналы КЗП с выхода триггера 44 подаются на входы

коммутатора 7 адреса, коммутатора 13 данных, формировйтелп 33 и элемента 32.

На фиг.7с показаны сигналы на выходе генератора 37 импульсов. Коммутатор 13 подключает к всем информационным входам блока 5 памяти выход распределителя 4 импульсов, а коммутатор 7 адреса - адреса считывания записи с выходов блока 2 синхрониз,ации и блока 8 преобразования координат. Запись информации из ЭВМ и считывание ее на экран индикатора 1 на видимом ходе кадра производится под управлением распределителя А импульсов, которьй на видимом ходе кадра разрешает доступ на ЭВМ к блоку 5 памяти, а в течение КЗП запрещает доступ на ЭВМ для проведения внутреннего контроля со- держи юго блока 5 памяти.

Распределитель 4 импульсов работает следующим образом.

В режиме считывания информации из блока 5 памяти он формирует временную ди рамму цикла считывания и управляет работой формирователя 3. Сигналы временной диаграммы (фиг. 6 д

ближайп ий цикл обращения к блоку 5 памяти (фиг. 7а) и сбрасывает триггер 62. Сигнал выделения цикла разрешает прохождение информации (фиг. 7е)с входа 18 через элемент И 52 и далее через коммутатор 13 на информационные входы блока 5 памяти (фиг, 7х), а также строба записи

(фиг. 7ij) через элемент И 51 на вход дешифратора 6 (фиг. 7и), осуществляя цикл записи в блок 5 памяти. По окончании дикла записи импульс конца обмена поступает на выход 15 с ЭВМ с

выхода элемента И 58. Одновибратор 63 формирует импульс запуска для блока 8 преобразования координат, а Одновибратор 59 - паузу, необходимую для прохояэдения соответствующего

количества тактовых импульсов в блок 8 преобразования координат для реализации функционально-растрового преобразования.

По окончании видимого хода кадра

сигнал КЗП, вырабатываемый блоком 2 синхронизации, поступает на первый управляющий вход коммутатора 7 адреса и подключает к входу блока 5 памяти выходы счетчика 25 адреса блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Устройство для отображения графической информации | 1987 |

|

SU1474724A1 |

| Устройство для орфографического контроля текстов | 1985 |

|

SU1278851A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

Изобретение относится-к области вычислительной техники и автоматики и может быть использовано для вьшода графической информации на ЭВМ, Целью изобретения является повышение достоверности отображения информации. Для этого в устройство, содержащее телевизионный индикатор 1, блок 2 синхронизации, формирователь 3 видеосигнала, распределитель 4 импульсов, -блок 5 памяти, дешифратор 6, коммутатор 7 адреса, блок 8 преобразования координат, введены три регистра 9 - П, блок 12 сравнения, комммутатор 13 данных и блок 14 управления контролем, Повышение достоверности отображения информации обеспечивается путем оперативного и непрерьшного контроля и диагностики исправности ячеек блока у 5 памяти и выдачи адресов неисправных разрядов в ЭВМ, 1 з,п, ф-лы, 7 ил. (Л

цикла считывания формируются на вы- 30 14 управления контролем (фиг. 6). ходах разрядов сдвигового регистра Кроме того, сигнал КЗП запрещает 49, который в течение цикла считывания выдвигает поразрядно логическую

обращение к устройству со стороны ЭВМ по выходу 16 и блокирует работ распределителя 4 импульсов путем установки в О триггера 64. Сигна КЗП показан на фиг. 6а, Кроме того сигнал КЗП положительной полярност поступает на первый вход элемента 31 и вход формирователя 33. формир 40 ватель 33 по переднему фронту КЗП формирует строб записи контрольног кода с выхода постоянной памяти 27 регистр 11 (фиг. 6г).

1, а в конце цикла считывания сбра

сьшается в нулевое состояние сигналом с первого выхода дешифратора 50 (фиг. 7), который вырабатьгоает временную последовательность импульсов на протяжении цикла считывания. Этим же сигналом окончания цикла перебрасывается триггер 53, которьш определяет на какой регистр и мультиплексор формирователя 3 поступают вырабатываемые дешифратором 50 сигналы записи с выходов элементов И 54 и 55 и сигналы управления мультиплексорами с выходов первой 56 и второй 57 групп элементов И.

I

На видимом ходе кадра временная диаграмма записи точек в блок 5 памяти приведена на фиг.7.

По сигналу требования записи, поступающему на вход 19 (фиг. 7), триггер 62 устанавливается в состояние логической 1 (фиг. 7г). При этом разблокированный триггер 64 под управлением сигнала с третьего выхода дешифратора 50 (фиг. 7) вьзделяет

14 управления контролем (фиг. 6). Кроме того, сигнал КЗП запрещает

обращение к устройству со стороны ЭВМ по выходу 16 и блокирует работу распределителя 4 импульсов путем установки в О триггера 64. Сигнал КЗП показан на фиг. 6а, Кроме того, сигнал КЗП положительной полярности поступает на первый вход элемента И 31 и вход формирователя 33. формиро- ватель 33 по переднему фронту КЗП формирует строб записи контрольного кода с выхода постоянной памяти 27 в регистр 11 (фиг. 6г).

На второй вход поступают импульсы конца цикла (фиг. 7Ь) временной диаграммы (фиг. 6а) блока 5 памяти первого выхода дешифратора 50, кото-, рые пересчитываются счетчиком 23 циклов . Контроль содерткимого блока 5 памяти осуществляется путем записи и считывания контрольных кодов, хранящихся в постоянной памяти 27, и сравнения записанного и считанного кода в блоке 12 сравнения. При несовпадении кодов с выхода 20 вьдает- ся в ЭВМ импульс индикации неисправности, с выхода 2 - адрес неиспран- ности слова, а с выхода 22 - позиционный код номера неисправности бита „ В общем случае контроль одного слова включает несколько операций проверки с различными контрольньми кодами, хранящимися в постоянной памяти 27, Число проверок слова определяется коэффициентом пересчета счетчика 24, выходы которого являются адресами контрольных кодов постоянной памяти 27. При реализации одной проверки выполняются след тощие четыре цикла, пересчитываемые счетчиком 23 циклов.

; В первом цикле по адресу Ац, задаваемому счетчиком 25 адреса, счи- тыается из блока 5 памяти информация в первый регистр 9 (фиг, бе). Запись/ информации в первый регистр 9.производится импульсом строба записи, вырабатываемым вторьп выходом дешифратора 50 (фиг, 6ж) и проходящим в перг- вом цикле (фиг. бе) через элеме нт 29. Во втором цикле в ячейку блока 5 .

20 АК,., По окончании сигнала КЗП коммутатор 7 адреса переключается на работу с выходами блока 2 синхронизации и блока 8 преобразования координат, а коммутатор 13 - на работу

памяти с адресом Ак записьшается пер- 25 выходом распределителя 4 импульсов.

вый контрольный код, хранящийся в третьем регистре 1 1 . При этом комму-, татор 13 переключается сигналом с второго выхода дешифратора 26 (фиг,, так, что к информаг(ионным входам блока 5 памяти подключаются выходы третьего регистра 11. При этом этот же сигнал, проходя через элемент ИЛИ, разрешает работу дешифратора 6 и запись информации в блок 5 памяти.

Считывание контрольной информации из ячейки с адресом производится в третьем цикле (фиг. 6и), когда сигнал на третьем выходе дешифратора 26 разрешает работу второго элемента 30, через который проходит строб записи (фиг, 6к)- во йторой регистр 10. После записи контрольного кода во.второй регистр 10 на выходах блока 12 сравнения появляется сигнал, индицирующий результат проверки (фиг. 6м),

Восстановление информации в ячейке с адресом АК-; производится в четвертом цикле, когда сигнал (фиг. 6л) с четвертого в ыхода дешифратора 26 переключает коммутатор 13 так, что к входам блока 5 памяти подключаются выходы первого регистра 9. Одновременно через элемент ИЛИ дешифратору 6 выдается сигнал на запись (фиг.бн).

В этом же четвертом такте сигнал : с выхода элемента ИЛИ 48 блока 12 сравнения стробируется в элементе И

который .также разблокируется. В следующем интервале КЗП контроль содержимого блока 5 памяти продолжается с прерванного места.

30 Поразрядное сравнение контрольных кодов, записанных во втором 10 и третьем 11 регистрах осуществляется группой 46-элементов 47 сложения по модулю два, выходы которых объединя35 ются элементом ИЛИ 48.

Таким образом, предлагаемое устройство обеспечивает повышение достоверности отображения информации путем оперативного.и непрерывного

40 контроля и диагностики исправности ячеек блока 5 памяти и выдачи адресов и неисправных разрядов в ЭВМ.

Формула изобретения

45

50

31 ив случае появления неисправности адрес с вькода счетчика 25 адреса записывается в четвертый регистр и поступает с выхода 21 в ЭВМ, и строб индикации неисправности с выхода элемента И 21 с выхода 20 также поступает в ЭВМ.

Указанные четьфе цикла составляют

одну проверку и пересчитьшаются

счетчиком 23 цикла, имеющим коэффициент пересчета, равный четырем. После этого в счетчик 24 прибавляется единица и начинается новый цикл

проверки по указанной вьше процедуре. После оконч&ния всех проверок по адресу АК-; в счетчик 25 адреса прибавляется единица и процедура начинается сначала для ячейки с адресом

АК,., По окончании сигнала КЗП коммутатор 7 адреса переключается на работу с выходами блока 2 синхронизации и блока 8 преобразования координат, а коммутатор 13 - на работу

выходом распределителя 4 импульсов.

который .также разблокируется. В следующем интервале КЗП контроль содержимого блока 5 памяти продолжается с прерванного места.

Поразрядное сравнение контрольных кодов, записанных во втором 10 и третьем 11 регистрах осуществляется группой 46-элементов 47 сложения по модулю два, выходы которых объединяются элементом ИЛИ 48.

Таким образом, предлагаемое устройство обеспечивает повышение достоверности отображения информации путем оперативного.и непрерывного

контроля и диагностики исправности ячеек блока 5 памяти и выдачи адресов и неисправных разрядов в ЭВМ.

Формула изобретения

щим входам соответственно блока памяти и дешифратора, четвертый выход распределителя подключен к тактирующему входу коммутатора адреса, первый и второй- синхронизирующие входы распределителя импульсов подключены к второму и третьему выходам блока синхронизации, четвертый выход которого является выходом сигнала режима контроля устройства и подключен к управляющим входам распределителя импульсов и коммутатора адреса, пятый выход блока синхронизации подключен к первому инфорйационному входу коммутатора адреса, выход которого подключен к адресному входу блока памяти, выход которого подключен к информационному входу формирователя видеосигнала, входы управления записью блока памяти подключены к входам дешифратора, первый информационный вход которого подключен к первому выходу блока преобразования координат, второй выход которого подключен к второму информационному входу коммутатора адреса, информационный вход блока преобразования координат является входом коо.рдинат устройства, управляющий вход блока преобразования координат подключен к пятому выходу распределителя импульсов , информационный вход которого является входом кода символа устрой- ства, второй управляющий в-ход распределителя импульсов является входом сигнала управления записью устрой- . ства, отличающееся тем, что, с целью повышения достоверности тображения информации, устройство одержит первый, второй и третий ре- истры, блок сравнения, коммутатор- анных и блок управления контролем, ервый выход которого является выодом сигнала неисправности устройства, второй выход блока управления контролем является выхоом сигнала адреса искаженного слова амяти устройства, третий, четвертый

и пятый Выходы блока управления конт- 50 ственно первого и второго элементов

ролем подключены к управляющим входам первого, второго и третьего регистров , шестой выход блока управления контролем подключен к третьему информационному входу коммутатора адреса, седьмой выход блока управления контролем подключен к второму информационному входу дешифратора, установочный вход блока, управления ,

J9672. 8

контролем подкл очен к четвертому ньг- ходу блока синхронизации, соединенному с первым управляющим входом коммутатора данных, второй управляю- иий вход которого подключен к восьмому выходу блока управления контролем, девятый выход которого подключен к информационному входу тре10 тьего регистра, выход которого подключен к первым информационным входам коммутатора данных и блока сравнения, первый выход которого является выходом кода номера искаженного бита дан15 ных устройства, второй выход блока сравнения подключен к управляющему входу блока управления контролем, стробирующий вход которого подключен к шестому выходу распределителя им20 пульсов, седьмой выход которого подключен к второ гу информационному входу коммутатора данных, выход которого подключен к информационноиу входу блока памяти, третий информа25 ционный вход коммутатора данных подключен к выходу первого регистра, информационный вход которого подключен к выходу блока памяти, подключенному -к информационному входу вто30 рого регистра , выход которого подключен к второму информационному входу блока сравнения,

35 управления ..контролем йодержит счет- «ик циклов, первый и второй счетчики адреса, дешифратор, постоянную память, регистр, первый,второй, третий и четвертый рлементы И, первый

40 и второй формирователи импульсов, первый и второй элементы 1ШИ, первый и второй входы первого элемента ИЛИ подключены соответственно к первому и второму выходам дешифратора,

45 которые являются восьмым вь ходом блока, выход первого элемента ИЛИ является седьмым выходом блока, третий и четвертый выходы дешифратора подключены к первым входам соответИ, выходы которых являются соответственно третьим и четвертым выходами блока, вторые входы первого и второго элементов И составляют строби- 55 рующий выход блока, соединненый с первым входом третьего элемента И, второй вход которого является управляющим входом блока, выход третьего элемента И является первым выходом

блока, соединенным с управляющим выходом регистра, третий вход третьего элемента И подключен к второму выходу дешифратора, выход которого подключен к первому выходу счетчика циклов, счетный вход которого подключен к выходу четвертого элемента И, первый вход которого подключен к стро- бирующему входу блока, второй вход четвертого элемента И является уста- Новочоным входом блока, соединенным с входом первого формирователя импульсов, выход которого подключен к первому входу второго элемента ИЛИ, выход которого является пятым выходом блока, второй вход второго элеMSO.§1 KfA.SO. S6.57

KSK,T WtJ

мента ИЛИ подключен к выходу второго формирователя импульсов, вход которого подключен к второму выходу счетчика циклов, третий выход которого подключен к счетному входу первого счетчика адресов, первый выход которого подключен к адресному входу постоянной памяти, выход которой является девятым выходом блока, второй выход первого счетчика адреса подключен к счетному входу второго сечтика адреса, выход которого является шестым выходом блока, соединенным с информационным входом регистра, выход которого является вторым выходом блока.

KSM K6A.4.1S.1

От 5л.11

К5л,5 KSAJ3 .6 К5Л.ШМ KfA.S

КШ

гг

ФигЛ

Фие,5

&.

(

О

| Техника средств связи | |||

| Сер | |||

| ВТСС, вып | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Устройство для вывода графической информации | 1979 |

|

SU930355A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1988-11-23—Публикация

1987-02-06—Подача