Изобретение относится к электротехнике и может быть использовано в асинхронном .электроприводе для регулирования скорости вращения двигателя.

Известны устройства для регулирования частоты вращения асинхронного двигателя (АД), содержащие шесть регулирующих тиристоров, соединенных попарно встречно-параллельно между собой и включенных в разрывы линейных приводов всех фаз статора АД.Квазичастотное регулирование, реализуемое такими устройствами, основано на однополупериодичном формировании выходного напряжения или тока в соответствии с сигналами модуляции.

Известно также устройство квазичастотного регулирования напряжения, содержащее два встречно-параллельно соединенных основных тиристора, включенные между питающей сетью и нагрузкой, и два встречно-параллельно соединенных тиристора, шунтирующие нагрузку.

Известно устройство для регулирования частоты вращения асинхронного двигателя, содержащее тиристорный коммутатор в цепи обмотки статора АД, блок синхронизации, подключенный к источнику питания, делитель частоты, один вход которого соединен с выходом блока синхронизации, а другой вход соединен с выходом блока управления, и выход - с распределителем импульсов, подключенным к управляющим электродам тиристорного коммутатора.

Недостатком известного устройства являются невысокие энергетические показатели, обусловленные наличием бестоковых пауз, возникающих при изменении по/1яр- ности питающего напряжения, а также дискретный характер регулирования частоты

VI Ч|

VI

вращения АД с возможностью плавного регулирования только в небольших пределах.

Цель изобретения - улучшение энергетических показателей устройства для регулирования частоты вращения асинхронного двигателя и расширение диапазона плавного регулирования частоты вращения.

Для этого в устройство для регулирования частоты вращения асинхронного электродвигателя, содержащее тиристорный коммутатор, выполненный в виде трех пар встречно-параллельно соединенных тиристоров, одни зажимы которого предназначены для соединения с клеммами питающей сети, а другие зажимы соединены с вывода- ми. для подключения статорной обмотки электродвигателя, и блок управления, введены три пары встречно-параллельно соединенных шунтирующих тиристоров, соединенных по схеме треугольник, выводы которой предназначены для подключе- ния к выводам статорной обмотки двигателя, преобразователь напряжение - частота, блок сигналов модуляции, блок формирования сигналов полярности, логический блок и блок усилителей-формирователей, первые три входа и вторые три входа блока формирования сигналов полярности соединены соответственно с клеммами для.подключения питающей сети и с выводами для подключения статорной обмотки электродвигателя, выход блока управления через преобразователь напряжение. - частота - с входом блока сигналов модуляции, семь выходов которого соединены с соответствующими управляющими входами логического блока, двенадцать информационных зхо- дов которого соединены с соответствующими выходами блока формирования сигналов полярности, выходы YI - Уе и У - У12 логического блока через блок усилителей-формирователей соединены с управляющими цепями соответствующих тиристоров коммутатора и шунтирующих тиристоров, где YI Mi -Si; Y2 Mi -Si; Ys M2 S2; Y4 M2 S2i Ys Мз Зз; Ye - Мз -Зз; Y Mi -M2--P -Mx-S54; Ye Mi -M2 -P их Yg M2 -Мз -P -Mxx xSes; Yiq M2 -Мз -P -Mx -See; Yji Мз х xMi -P-Mx -346; Yt2 Мз -Mi -P -Мх-3б4; P (Yi + Y2) -(Y3 + Y4) + (Yi + Y2) -(Y5 + Y6) + +(Y3 + Y4) -(Y5 + Ye),

где Si, Si, 32, 32, Зз, Зз. Ss4. 345, Збб, 356, 346, Зб4 - сигналы на выходах блока формирования сигналов полярности, где Si Ui; 32 sign 1)2; Зз - sign Уз - сигналы полярности фазных напряжений источника

питания Ui, Ua; a Ski - sign Uw - (1 + Uw// Uki/)/2 - Ski; k - 4,5,6; I - 4,5,6; I k - сигналы полярности напряжений на .шунтирующих тиристорах Uw;.Mi, Mi, Ma, Mz, Мз, Мз, MX сигналы на выходах блока сигналов модуляции;

. МР | + 2(p-1)JTQ}-1{t- + 2(p-lH3 TQ}};

Mx- 2 {1(t-kTo)(kTQ + k o

где 1(t)

4J

1,2,b;

при t 0 при t 0,

k 0,1,2..., «,

To - период сигнала на выходе преобразователя напряжение - частота;

Тс - период напряжения источника питания.

Блок сигналов модуляции содержит кольцевой сдвиговый регистр, выполненный на шести D-триггерах, формирователь

сигналов запрета, RC-цепь установки и дифференцирующую RC-цепь, D-вход каждого последующего .D-триггера соединен Q-вы- ходом предыдущего D-триггера, С-входы всех D-триггеров объединены и соединены

с входом формирователя сигналов запрета и выходом дифференцирующей RC-цепи, вход которой образует вход блока сигналов модуляции, 3-входы первого, пятого и шестого D-триггеров и R-входы второго,

третьего и четвертого D-триггеров объединены и подключены к RC-цепи установки, Q-выходы D-триггеров и выход формирователя сигналов запрета образуют выходы блока сигналов модуляции.

Блок формирования сигналов полярности содержит шесть формирователей с двумя входами и двумя выходами каждый, первые входы первого - третьего формирователей объединены, а вторые их входы

образуют первые три входа блока формирования сигналов полярности, первые входы четвертого - шестого формирователей соединены с вторыми входами соответственно шестого, четвертого и пятого формирователей и образуют вторые три входа блока формирования сигналов полярности, выходы которого образованы выходами шести формирователей.

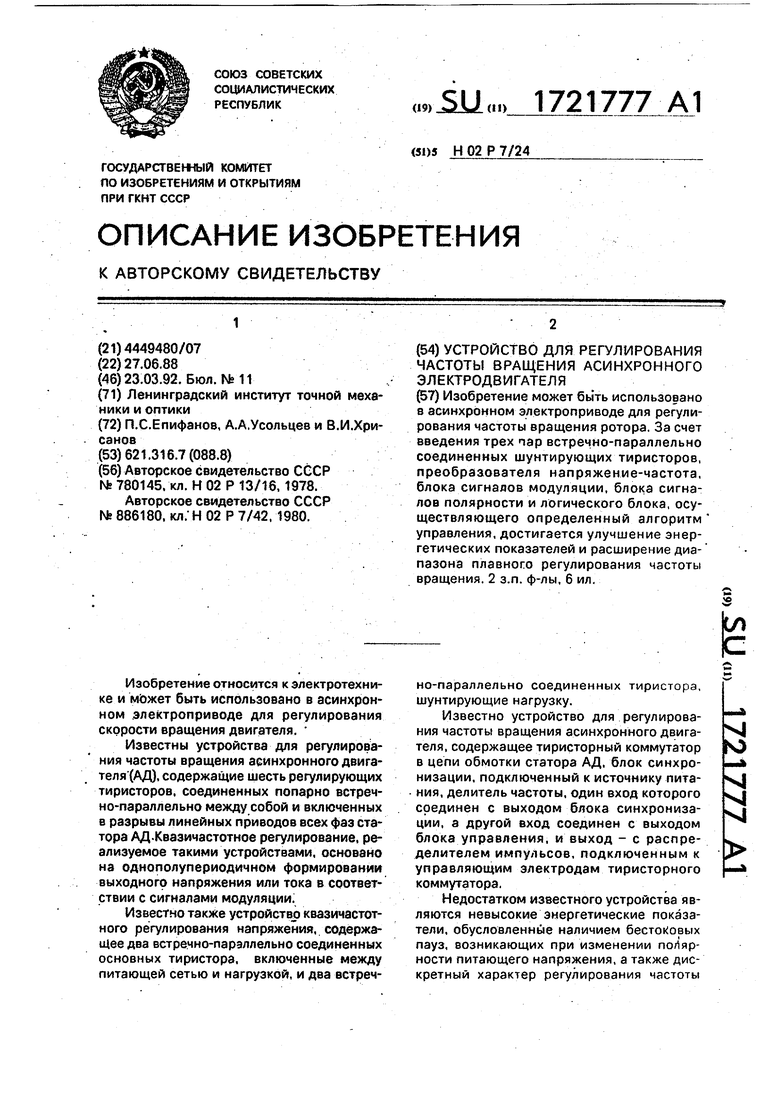

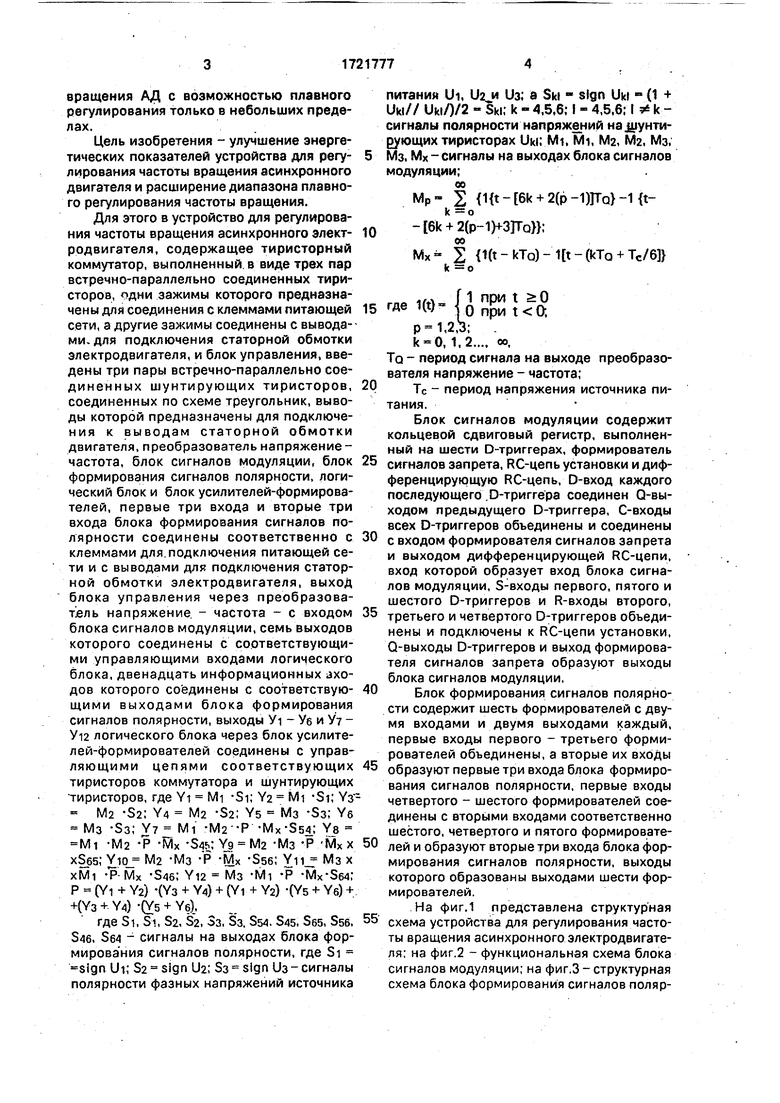

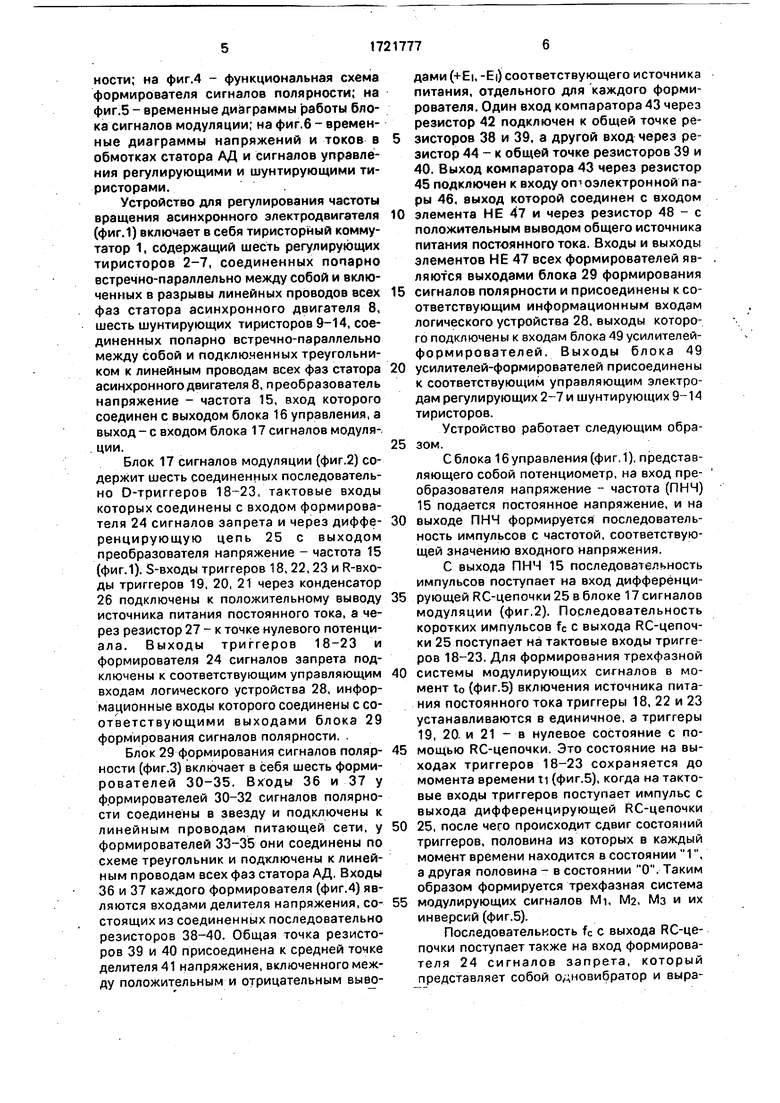

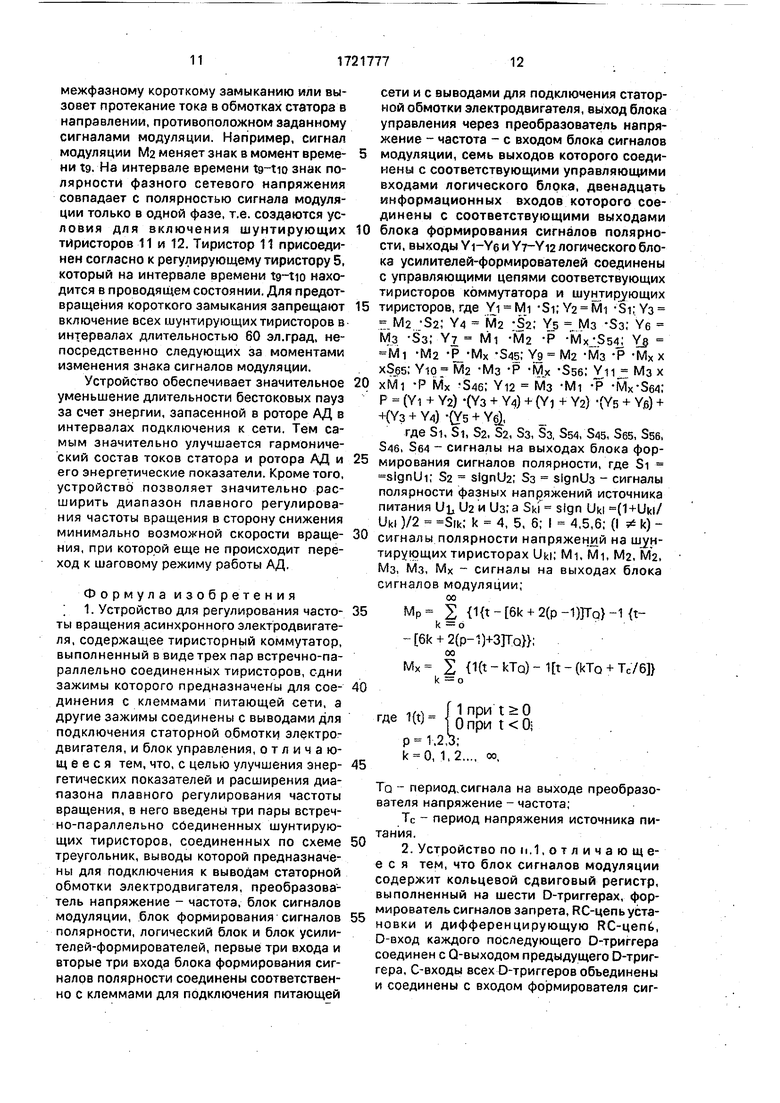

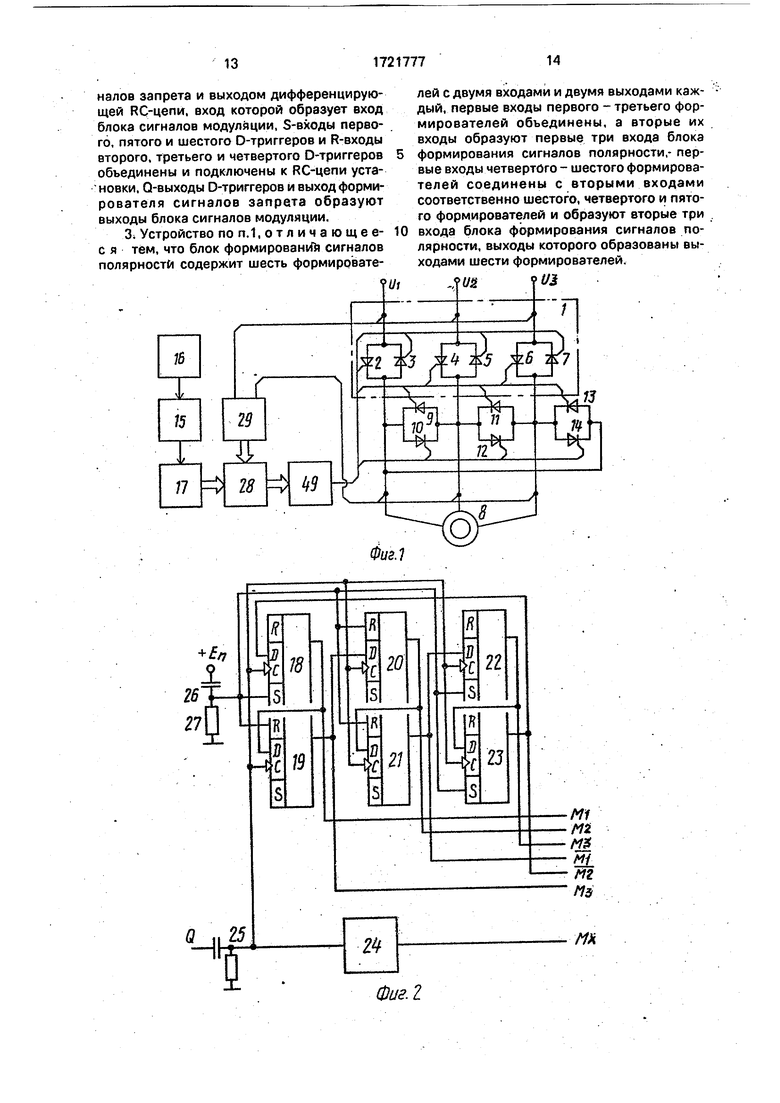

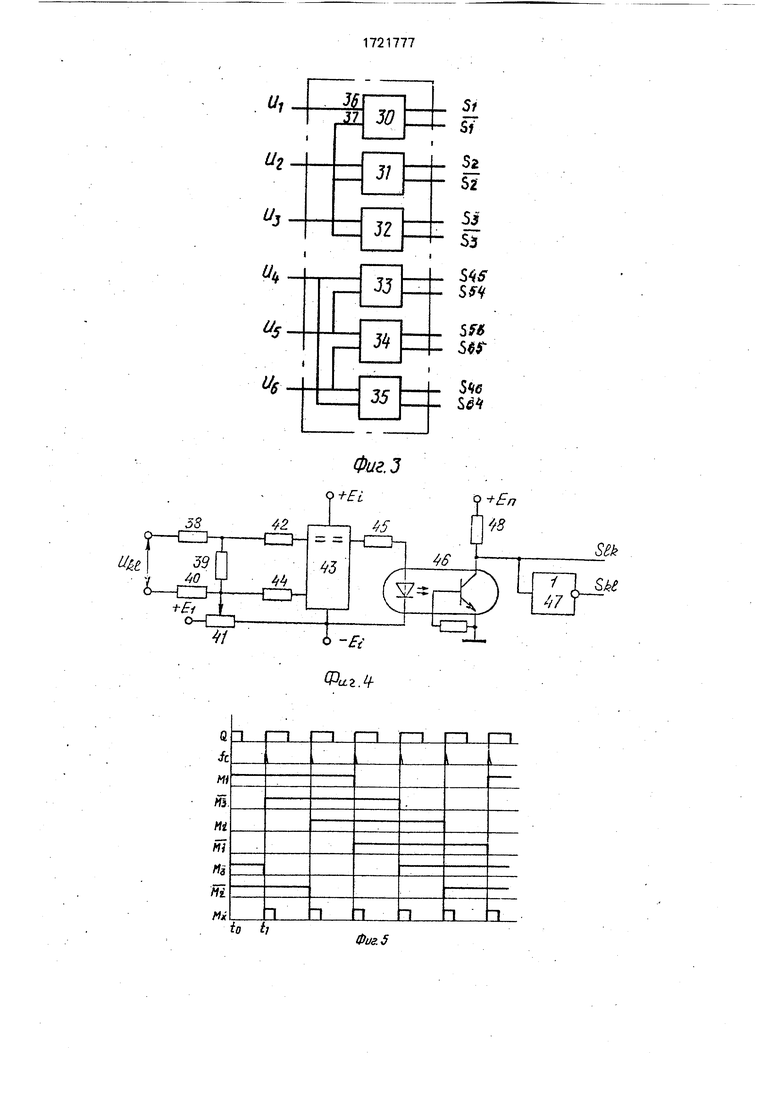

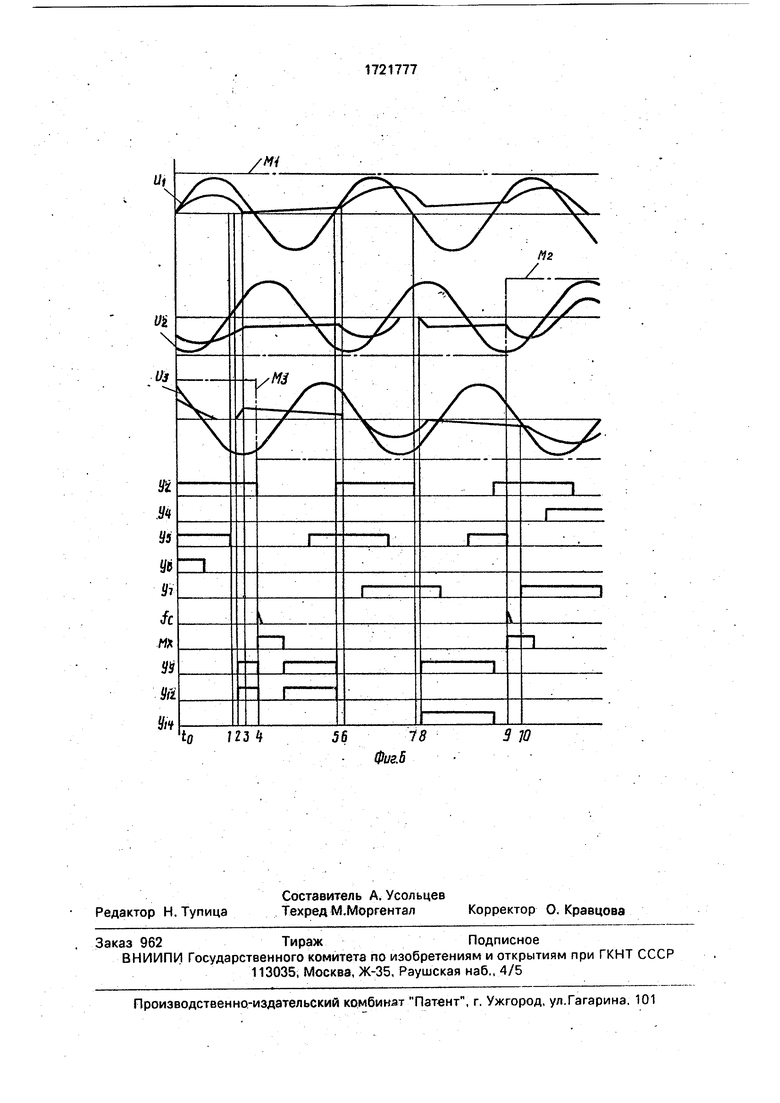

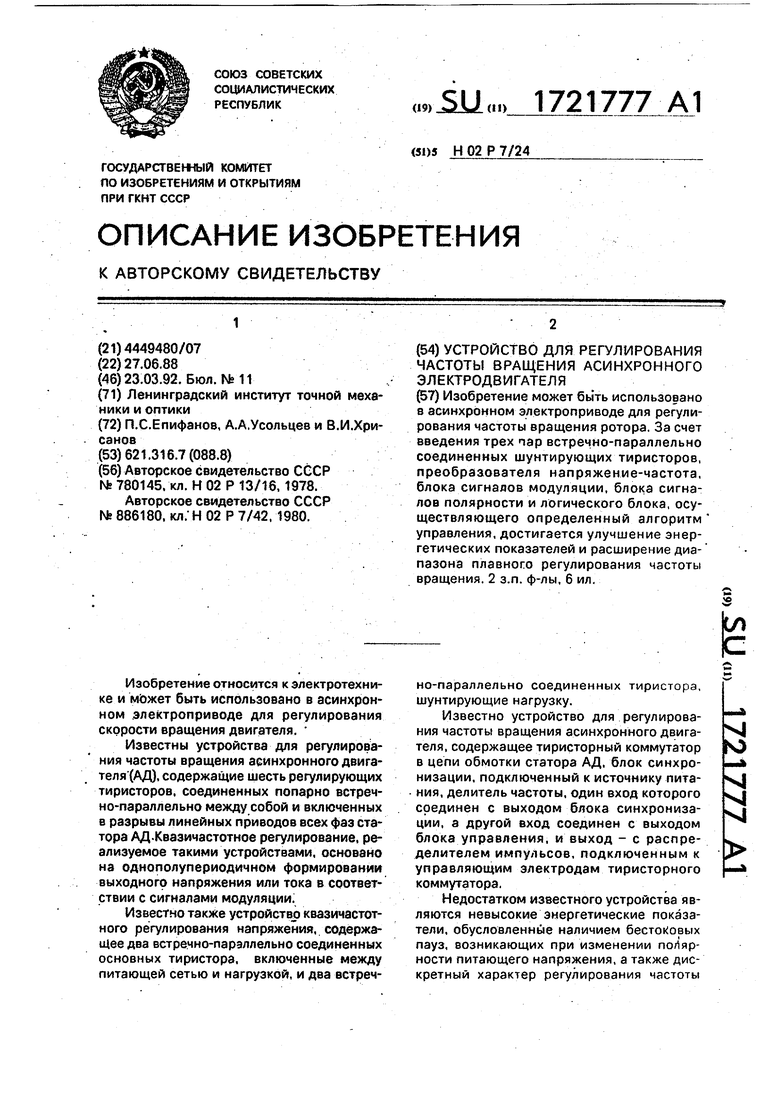

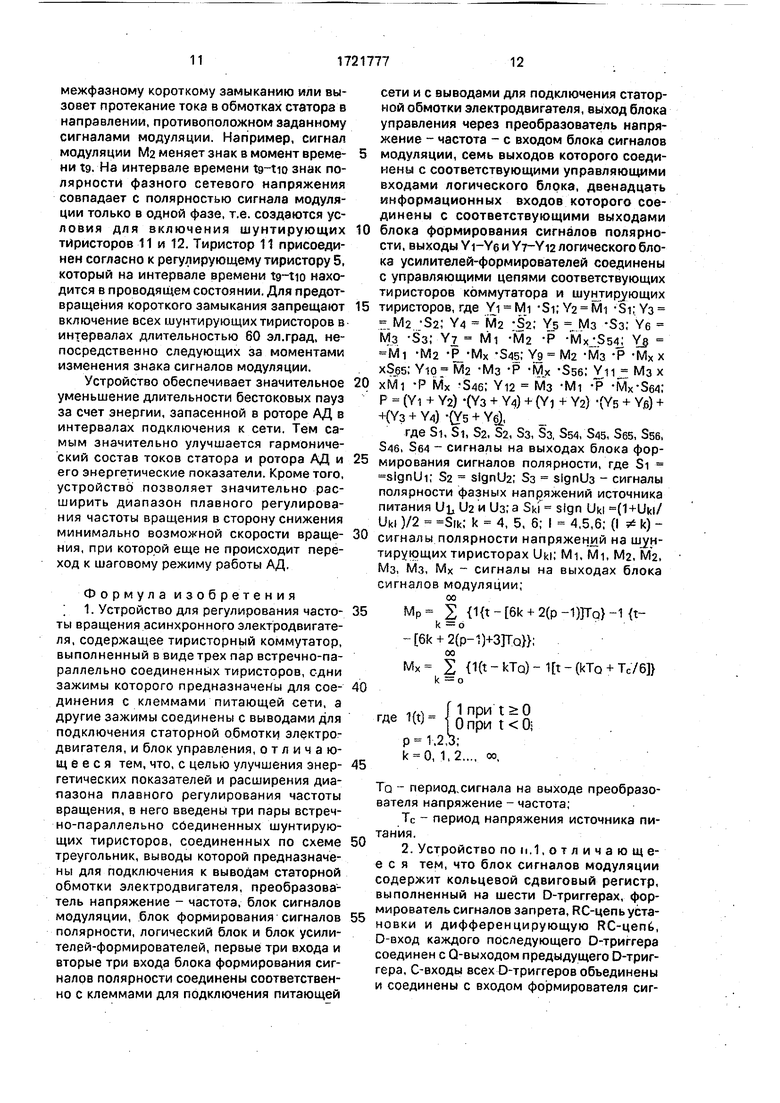

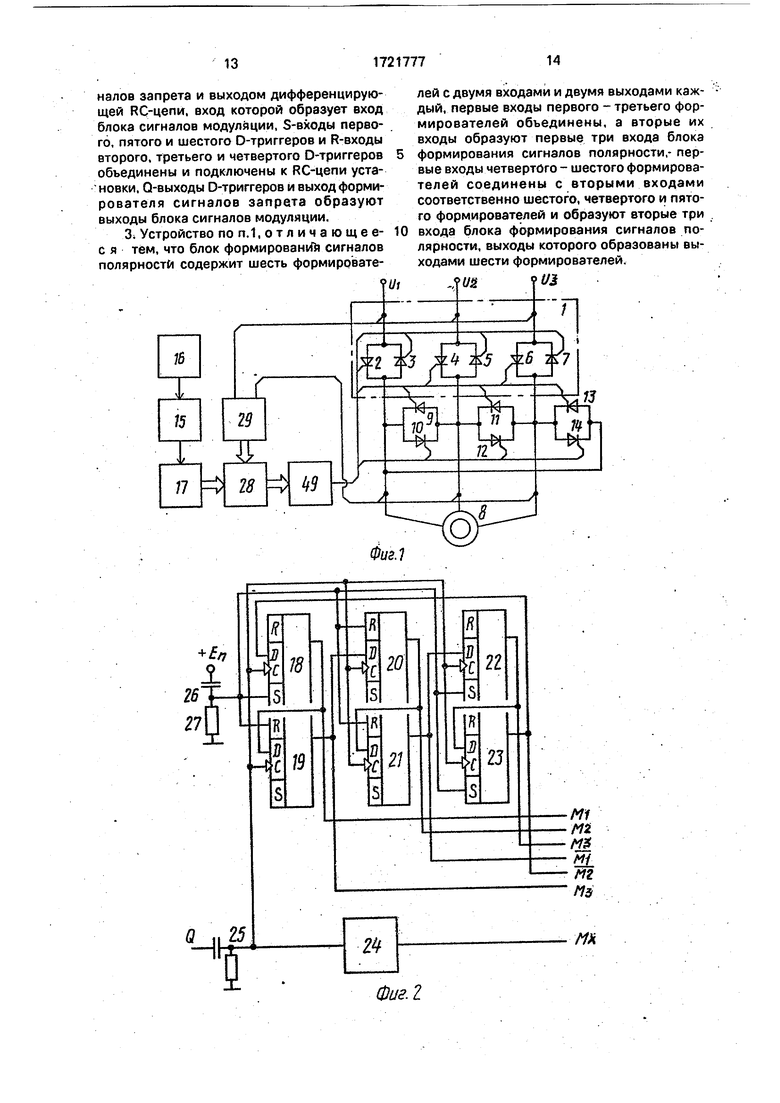

На фиг.1 представлена структурная

схема устройства для регулирования частоты вращения асинхронного электродвигателя; на фиг.2 - функциональная схема блока сигналов модуляции; на фиг.З - структурная схема блока формирования сигналов полярности; на фиг.4 - функциональная схема формирователя сигналов полярности; на фиг.5 - временные диаграммы работы блока сигналов модуляции; на фиг.б - временные диаграммы напряжений и токов в обмотках статора АД и сигналов управления регулирующими и шунтирующими тиристорами..

Устройство для регулирования частоты вращения асинхронного электродвигателя (фиг.1) включает в себя тиристорный коммутатор 1, содержащий шесть регулирующих тиристоров 2-7, соединенных попарно встречно-параллельно между собой и включенных в разрывы линейных проводов всех фаз статора асинхронного двигателя 8, шесть шунтирующих тиристоров 9-14, соединенных попарно встречно-параллельно между собой и подключенных треугольником к линейным проводам всех фаз статора асинхронного двигателя 8, преобразователь напряжение - частота 15, вход которого соединен с выходом блока 16 управления, а выход- с входом блока 17 сигналов модуля-.- . ции.

Блок 17 сигналов модуляции (фиг.2) содержит шесть соединенных последовательно D-тритгеров 18-23, тактовые входы которых соединены с входом формирователя 24 сигналов запрета и через дифференцирующую цепь 25 с выходом преобразователя напряжение - частота 15 (фиг.1). S-входы триггеров 18, 22,23 и R-BXO- ды триггеров 19, 20, 21 через конденсатор 26 подключены к положительному выводу источника питания постоянного тока, а через резистор 27 - к точке нулевого потенци- ала. Выходы триггеров 18-23 и формирователя 24 сигналов запрета подключены к соответствующим управляющим входам логического устройства 28, информационные входы которого соединены с со- ответствующими выходами блока 29 формирования сигналов полярности, .

Блок 29 формирования сигналов полярности (фиг.З) включает в себя шесть формирователей 30-35. Входы 36 и 37 у формирователей 30-32 сигналов полярности соединены в звезду и подключены к линейным проводам питающей сети, у формирователей 33-35 они соединены по схеме треугольник и подключены к линейным проводам всех фаз статора АД. Входы 36 и 37 каждого формирователя (фиг.4) являются входами делителя напряжения, состоящих из соединенных последовательно резисторов 38-40. Общая точка резисторов 39 и 40 присоединена к средней точке делителя 41 напряжения, включенного между положительным и отрицательным выводами (+Ei, -Ei) соответствующего источника питания, отдельного для каждого формирователя. Один вход компаратора 43 через резистор 42 подключен к общей точке ре- 5 зисторов 38 и 39, а другой вход через резистор 44 - к общей точке резисторов 39 и 40. Выход компаратора 43 через резистор 45 подключен к входу от оэлектрон ной пары 46, выход которой соединен с входом

0 элемента НЕ 47 и через резистор 48 - с положительным выводом общего источника питания постоянного тока. Входы и выходы элементов НЕ 47 всех формирователей являются выходами блока 29 формирования

5 сигналов полярности и присоединены к соответствующим информационным входам логического устройства 28, выходы которого подключены к входам блока 49 усилителей- формирователей. Выходы блока 49

0 усилителей-формирователей присоединены к соответствующим управляющим электродам регулирующих 2-7 и шунтирующих 9-14 тиристоров.

Устройство работает следующим обра5 зом.

С блока 16 управления (фиг.1), представляющего собой потенциометр, на вход преобразователя напряжение - частота (ПНЧ) 15 подается постоянное напряжение, и на

0 выходе ПНЧ формируется последовательность импульсов с частотой, соответствующей значению входного напряжения.

С выхода ПНЧ 15 последовательность импульсов поступает на вход дифферёнци5 рующей RC-цепочки 25 в блоке 17 сигналов модуляции (фиг,2). Последовательность коротких импульсов fc с выхода RC-цепочки 25 поступает на тактовые входы триггеров 18-23. Для формирования трехфазной

0 системы модулирующих сигналов в момент to (фиг.5) включения источника питания постоянного тока триггеры 18, 22 и 23 устанавливаются в единичное, а триггеры 19, 20. и 21 - в нулевое состояние с по5 мощью RC-цепочки. Это состояние на выходах триггеров 18-23 сохраняется до момента времени ti (фиг.5), когда на тактовые входы триггеров поступает импульс с выхода дифференцирующей RC-цепочки

0 25, после чего происходит сдвиг состояний триггеров, половина из которых в каждый момент времени находится в состоянии 1, а другая половина - в состоянии О. Таким образом формируется трехфазная система

5 модулирующих сигналов Mi, M2, Мз и их инверсий (фиг.5).

Последовательность fc с выхода RC-цепочки поступает также на вход формирователя 24 сигналов запрета, который представляет собой одновибратор и вырабатывает импульсы длительностью 60 эл.град Мх, передние фронты которых совпадают по времени с моментами изменения полярностей модулирующих сигналов (фиг.5).

Сигналы модуляции Mi - Мз, а также сигнал MX могут быть представлены аналитически в виде

Мр- 2 {1{t- 6k + 2(p-1)TTQ-Ht- -E6k + 2(p-1)+3rra}};

00

MX- 2 {1(t-kTo)(kTQ +

k o

1(t)

4°

1,2,3;

при t&O при t О,

к-0,1,2..., оо,

TQ - период сигнала на выходе преобразователя напряжение - частота;

Тс - период напряжения источника питания.

Формирователи 30-32, на входы которых подаются фазные напряжения Ui, Ua, Ua питающей сети, вырабатывают логические сигналы, единичное состояние которых соответствует -положительной полуволне этих напряжений, т.е. в соответствии с выражениями

St sign Ui; 82 sign U2; 83m sign Уз, (1)

а также их инверсии Si, 82, 83.

Формирователи 33-35, на входы которых подаются напряжения U45. Use, Ue4 с выводов обмоток статора АД, вырабатывают логические сигналы 845. Sse, 8в4, единичное состояние которых соответствует положительной полярности напряжений соответственно на шунтирующих тиристорах 10,12 и 14 и инверсные им логические сигналы Ss4,8б5, S4S. единичное состояние которых соответствует положительной полярности напряжений соответственно на шунтирующих тиристорах 9, 11 и 13. Таким образом, знаки сигналов полярности, вырабатываемых формирователями 33-35. определяются в соответствии с выражением

Ski-(1+Uki/lUkil)/2-Sik.(2)

где k - 4,5,6; I - 4,5,6; k. ;

Входное напряжение формирователя сигнала полярности Uw (фиг.4) через делитель, выполненный на резисторах 38-40 и предназначенный для снижения входного напряжения до значений, допускаемых входными цепями компаратора, подается

на вход компаратора 43. Один из входов компаратора подключен также к средней точке делителя 41 напряжения, включенного между положительным и отрицательным

выводами источника питания постоянного тока и предназначенного для установки уровня переключения компаратора. Для питания компаратора в каждом из формирователей 30-35 используется отдельный

источник постоянного тока EI. С выхода компаратора 43 сигнал через токоограничиваю- щий резистор 45 поступает на вход оптоэлектронной пары 46, применение которой в сочетании с использованием отдельного источника питания в каждом формирователе обеспечивает гальваническую развязку их входных цепей. С выхода оптоэлектронной пары 46 сигнал поступает на вход формирователя и на вход элемента

НЕ 47, выход которого также является выходом формирователя. Таким образом, на выходах формируются логические сигналы Ski, единичное состояние которых соответствует положительной полярности напряжений

Uki, и инверсные им сигналы SIR.

Сигналы с выходов блока 29 поступают на информационные входы логического устройства 28, на управляющие входы которого подаются сигналы модуляции Mr, Mz, Мз и

их инверсии, а также сигнал запрета Мх с выходов блока сигнала модуляции.

Логическое устройство 28 вырабатывает сигналы управления Y2-Yy регулирующими тиристорами 2-7 в соответствии с

логическими выражениями

Y2 Mi;Y3 Mi -Si;Y4 -82; Ye Мз -8з:

M2 vS.2 (3) Y7 M3-$3,

а также сигналы Ug-Yi4 управления шунтирующими тиристорами 9-14:

Yg - Mi -М2 -Р Мх -854; Yio Mr -M2 x

xP % 845; Yn M2. -Мз- Р MxjSe 5; Yj2 M2 -Ms Sse; Mr Px xMx 846,Y14 M3 Mi -P -Mx -864. (4)

где сигнал Р соответствует интервалам времени, в которых полярности фазных

напряжений питающей сети совпадают с полярностями соответствующих сигналов модуляции не менее чем в двух фазах и определяются в соответствии с логическим выражением

Р - (Y2 + Ys) (Y4 + Ys) + (Y2 + Ys) -(Ye -ь + Y7) + (Y4 + Y5)-{Y6 + Y7).(5)

Единичное состояние сигналов Y2-Y и Yg-Yw, вырабатываемых логическим устройством, соответствует -наличию сигнала

управления тиристором, номер которого соответствует цифровому индексу сигнала Y.

Сигналы Y2-Y и Yg-Y через блок 49 выходных формирователей, обеспечивающих их усиление и гальваническую развязку, поступают на управляющие электроды регулирующих 2-7 и шунтирующих 9-14 тиристоров. Блок 49 выходных формирователей представляет собой совокупность двенадцати одноканальных усилителей- формирователей..

Алгоритм работы, реализуемый логическим устройством 28, заключается в следующем. При совпадении полярностей фазных напряжений питающей сети Ui, U2, Уз с полярностями соответствующих сигналов модуляции Mi, M2, Мз производится включение регулирующих тиристоров, создающих в обмотках статора АД импульсные токи, направление которых соответствует полярности сигналов модуляции.

К каждой паре регулирующих тиристоров подключены две пары шунтирующих тиристоров, в каждой из которых имеется по одному тиристору, включенному согласно с одним из регулирующих. Под согласным включением понимается такое включение, когда к катоду одного тиристора подключен анод другого. Таким образом, например, к тиристору 2 подключены согласно тиристоры 10 и 13, а к тиристору 3 - 9 и 14.

Кроме того, алгоритм работы устройства в общем случае может нарушаться в моменты изменения знаков сигналов модуляции. В интервалах времени длительностью 60 эл.град. непосредственно следующих за моментами изменения знаков сигналов модуляции, возможны такие включения шунтирующих тиристоров, которые создают режим короткого замыкания или формируют в обмотках статора АД импульсы тока произвольной полярности. Поэтому в пределах этих интервалов запрещают включение всех- шунтирующих тиристоров сигналом MX.

. При работе схемы (фиг.1), например, на интервале времени t0-t4 (фиг,6) знаки сигналов модуляции неизменны итаковы, что разрешается включение регулирующих тиристоров 2, 5 и 6. Согласно к этим тиристорам подключены шунтирующие тиристоры 10, 11, 13 и 14, включение которых на напряжении интервала времени to-t/j запрещается. Токи в обмотках статора АД в этом интервале времени формируются под действием сетевых напряжений. Напряжение на шунтирующих тиристорах формируется как сумма приложенных к ним линейных

сетевых напряжений и ЭДС самоиндукции, трансформации и вращения. В момент времени ti (фиг.6) заканчивается интервал, в котором полярности фазных сетевых напря- 5 жений совпадают с полярностями соответствующих сигналов модуляции не менее чем в двух фазах, однако через регулирующие тиристоры 2 и 5 продолжает протекать ток, уменьшающийся под действием сетевого

0 напряжения. В момент времени т.2 под действием ЭДС обмоток статора АД шунтирующие тиристоры 9 и 12, к которым до этого момента было приложено обратное напряжение, смещаются в прямом направлении

5 и включаются импульсами управления. На интервале времени т. ток через шунтирующие тиристоры 9 и 12 нарастает одновременно с убыванием тока через регулирующие тиристоры 2 и 5. Ток через

0 тиристор 6 прекратился ранее в течение интервала под действием сетевого напряжения.

В момент времени тз выключается регулирующий тиристор 2, к которому под

5 действием ЭДС обмоток статора прикладывается обратное напряжение. Одновременно выключается регулирующий тиристор 5, поскольку цепь тока замыкается через шунтирующие тиристоры 9 и 12, чем обеспечи0 вается непрерывность тока в обмотках статора АД в интервале ta-ts, когда статор отключен от питающей сети.

В момент времени ts начинается интервал, в котором полярности фазных сетевых

5 напряжений совпадают с полярностями сигналов модуляции в двух фазах, однако шунтирующие тиристоры 9 и 12 выключаются в момент времени te, когда под действием сетевых напряжений они смещаются в об0 ратном направлении.

На интервале времени te-t токи в обмотках статора протекают под действием сетевых напряжений через регулирующие тиристоры 2, 5 и 7, встречно которым под5 ключены шунтирующие тиристоры 9 и 14, и в момент ta. когда под действием ЭДС обмоток статора тиристоры 9 и 14 смещаются в прямом направлении, они включаются импульсами управления. Дальнейшее форми0 рование токов в статоре АД происходит аналогично.

В общем случае при плавном асинхронном изменении частоты сигналов модуляции изменение их полярности происходит

5 в произвольные моменты времени относительно фазных сетевых напряжений. При этом могут быть созданы условия для включения шунтирующих тиристоров, подключенных согласно с включенными регулирующими тиристорами, что приведет к

межфазному короткому замыканию или вызовет протекание тока в обмотках статора в направлении, противоположном заданному сигналами модуляции. Например, сигнал модуляции М2 меняет знак в момент времени tg. На интервале времени tg-tio знак полярности фазного сетевого напряжения совпадает с полярностью сигнала модуляции только в одной фазе, т.е. создаются условия для включения шунтирующих тиристоров 11 и 12. Тиристор 11 присоединен согласно к регулирующему тиристору 5, который на интервале времени tg-tio находится в проводящем состоянии. Для предотвращения короткого замыкания запрещают включение всех шунтирующих тиристоров в интервалах длительностью 60 эл.град, непосредственно следующих за моментами изменения знака сигналов модуляции.

Устройство обеспечивает значительное уменьшение длительности бестоковых пауз за счет энергии, запасенной в роторе АД в интервалах подключения к сети. Тем самым значительно улучшается гармонический состав токов статора и ротора АД и его энергетические показатели. Кроме того, устройство позволяет значительно расширить диапазон плавного регулирования частоты вращения в сторону снижения минимально возможной скорости вращения, при которой еще не происходит переход к шаговому режиму работы АД.

Формула изобретения ; 1. Устройство для регулирования частоты вращения асинхронного электродвигателя, содержащее тиристорный коммутатор, выполненный в виде трех пар встречно-параллельно соединенных тиристоров, одни зажимы которого предназначены для соединения с клеммами питающей сети, а другие зажимы соединены с выводами для подключения статорной обмотки электродвигателя, и блок управления, отличающееся тем, что, с целью улучшения энергетических показателей и расширения диапазона плавного регулирования частоты вращения, в него введены три пары встречно-параллельно соединенных шунтирующих тиристоров, соединенных по схеме треугольник, выводы которой предназначены для подключения к выводам статорной обмотки электродвигателя, преобразователь напряжение - частота, блок сигналов модуляции, блок формирования сигналов полярности, логический блок и блок усилителей-формирователей, первые три входа и вторые три входа блока формирования сигналов полярности соединены соответственно с клеммами для подключения питающей

сети и с выводами для подключения статорной обмотки электродвигателя, выход блока управления через преобразователь напряжение - частота - с входом блока сигналов

модуляции, семь выходов которого соединены с соответствующими управляющими входами логического блока, двенадцать информационных входов которого соединены с соответствующими выходами

блока формирования сигналов полярности, выходы Yi-Ye и Yr-Yi2 логического блока усилителей-формирователей соединены с управляющими цепями соответствующих тиристоров коммутатора и шунтирующих

тиристоров, где Yi Mi -Si;Y2 Mi -Si;Y3 М2 -Sa; Y4 Mz -Sa; Ys Мз -5з; Ye Мз -S3; Y - Mi -M2 -P Yj Mi -M2 -S45; Yj M2 -Мз -P -Mxx х5б5; Yio M2 -Мз P -Mx Sse; YHJ Мз х

xMi -P MX -S4e; Yi2 Мз -Mi -P -MX-S64; P (Yi + Y2) (Y3 + Y4) + (Yj + Y2) -Г/5 + Yfi) + +(Y3 + Y4)-(Ys + Ye),

где Si, Si, Sa, 82, 83, Зз, S54, S45, Ses, Sse, S46, Se4 сигналы на выходах блока формирования сигналов полярности, где Si signUi; Sz signlte; 5з slgnUs - сигналы полярности фазных напряжений источника питания UL Ua и Уз; a Skf sfgn Uki (1+Uicl/ UM )/2 - Sik; k 4, 5, 6; I 4,5,6; (I k) сигналы полярности напряжений на шунтирующих тиристорах Uki; MI, Mi, М2, М2, Мз, Мз, MX - сигналы на выходах блока сигналов модуляции;

Мр f {1{t- 6k + 2(p-1)TQ}-1{tk 6

6k + 2(P-1)+3 TQ}};

00

MX 2 {1(t - kTQ) - - (kTQ +

k o

где 1{t)

p-T.2, k 0, 1,2...,

1 при t 0 О при t 0;

00

0

5

TQ - период,сигнала на выходе преобразователя напряжение - частота;

Тс - период напряжения источника питания.

2. Устройство по II,1, отличающееся тем, что блок сигналов модуляции содержит кольцевой сдвиговый регистр, выполненный на шести D-триггерах, формирователь сигналов запрета, RC-цепь установки и дифференцирующую RC-цепь, D-вход каждого последующего D-триггера соединен с Q-выходом предыдущего D-триггера, С-входы всех D-триггеров объединены и соединены с входом формирователя сигналов запрета и выходом дифференцирующей RC-цепи, вход которой образует вход блока сигналов модуляции, S-входы первого, пятого и шестого D-триггеров и R-входы второго, третьего и четвертого D-триггеров объединены и подключены к RC-цепи уста- новки. Q-выходы D-триггеров и выход формирователя сигналов запрета образуют выходы блока сигналов модуляции.

3; Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок формирования сигналов полярности содержит шесть формировате0

лей с двумя входами и двумя выходами каждый, первые входы первого - третьего формирователей объединены, а вторые их входы образуют первые три входа блока формирования сигналов полярности,- первые входы четвертого - шестого формирователей соединены с вторыми входами соответственно шестого, четвертого и пятого формирователей и образуют вторые три входа блока формирования сигналов полярности, выходы которого образованы выходами шести формирователей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехфазный преобразователь частоты с непосредственной связью | 1988 |

|

SU1617573A1 |

| Способ квазичастотного регулирования напряжения переменного тока | 1982 |

|

SU1078578A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| Способ регулирования частоты вращения трехфазного асинхронного электродвигателя | 1985 |

|

SU1376209A1 |

| Устройство для программного управления инвертором напряжения в электроприводе переменного тока | 1990 |

|

SU1737678A1 |

| Способ управления асинхронным электроприводом | 1986 |

|

SU1429271A1 |

| Устройство для возбуждения синхронной электрической машины | 1985 |

|

SU1387152A1 |

| Устройство для управления асинхронным электродвигателем с фазным ротором | 1983 |

|

SU1131010A1 |

| Устройство для реверса асинхронного частотно-регулируемого электродвигателя | 1983 |

|

SU1418881A1 |

| Способ управления асинхронным электроприводом | 1988 |

|

SU1628175A1 |

Изобретение может быть использовано в асинхронном электроприводе для регулирования частоты вращения ротора. За счет введения трех пар встречно-параллельно соединенных шунтирующих тиристоров, преобразователя напряжение-частота, блока сигналов модуляции, блока сигналов полярности и логического блока, осуществляющего определенный алгоритм управления, достигается улучшение энергетических показателей и расширение диапазона плавного регулирования частоты вращения. 2 з.п. ф-лы, 6 ил.

Ml № MS

Ш. fit

Us

Фиг.Чio ii

Фиг.З

Фиг. 5

Щ

N

/Mi

У$

t0 234

5675

(Oyafi

y

#2

5 10

| Способ квазичастотного регулирования напряжения | 1978 |

|

SU780145A1 |

| кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для регулирования частоты вращения асинхронного электродвигателя | 1980 |

|

SU886180A1 |

Авторы

Даты

1992-03-23—Публикация

1988-06-27—Подача