1

(21)4379258/24-07 (22) 17.02.88 (46)30.12.90. Б юл. N-48

(71)Ленинградский институт точной механики и оптики

(72)П.С.Епифанов, А.А.Усольцев и В.И.Хри- санов

(53)621.314.27(088.8)

(56) Авторское свидетельство СССР

№ 780145, кл. Н 02 Р 13/16. 1978.

Авторское свидетельство СССР № 886180,кл. Н 02 Р 7/42,1980.

(54) ТРЕХФАЗНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ С НЕПОСРЕДСТВЕННОЙ СВЯЗЬЮ

(57) Изобретение относится к области силовой преобразовательной техники и может быть использовано в электроприводах переменного тока. Целью его является улучшение качества тока в нагрузке за счет устранения бестоковых пауз. Преобразователь содержит регулирующие 2-7 и шунтирующие 33-38 тиристоры. Предлагаемый алгоритм управления реализуется системой управления 12-14, 39, 48, 49. 7 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования частоты вращения асинхронного электродвигателя | 1988 |

|

SU1721777A1 |

| Устройство для управления преобразователем постоянного напряжения в трехфазное квазисинусоидальное | 1985 |

|

SU1359872A1 |

| Формирователь линейно-частотно-модулированных сигналов | 1989 |

|

SU1706004A1 |

| СПОСОБ УПРАВЛЕНИЯ ЧАСТОТНЫМ АСИНХРОННЫМ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2081503C1 |

| Автоматический регулятор компенсирующего устройства | 1990 |

|

SU1704145A1 |

| Способ торможения электродвигателя переменного тока и устройство для его осуществления | 1985 |

|

SU1336183A1 |

| Регулятор компенсирующего устройства | 1990 |

|

SU1721705A2 |

| УСТРОЙСТВО для ПЛАВНОГО АВТОМАТИЧЕСКОГО | 1969 |

|

SU253110A1 |

| СПОСОБ УПРАВЛЕНИЯ ТИРИСТОРНЫМ ВЫПРЯМИТЕЛЕМ И УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТИРИСТОРНЫМ ВЫПРЯМИТЕЛЕМ | 1991 |

|

RU2107381C1 |

| Преобразователь постоянного напряжения в многофазное переменное | 1977 |

|

SU780125A1 |

Изобретение относится к области силовой преобразовательной техники и может быть использовано в электроприводах переменного тока. Целью его является улучшение качества тока в нагрузке за счет устранения бестоковых пауз. Преобразователь содержит регулирующие 2 - 7 и шунтирующие 33 - 38 тиристоры. Предлагаемый алгоритм управления реализуется системой управления 12 - 14, 39, 48, 49. 7 ил.

л::

&

«

Фиг.1

Ш

М2

мз

ел

с

,

j

V,

JJ

и

А

36

35

щ

38

37

Оч

VJ

СЛ VI

я

JO

I

Изобретение относится к силовой преобразовательной технике и служит для регу- лирования частоты основной гармонической составляющей в трехфазной активно-индуктивной нагрузке, в частности может быть использовано в электроприводе переменного тока для регулирования скорости вращения двигателя.

Цель изобретения - улучшение энергетических показателей за счет устранения бестоковых пауз и увеличения пульсности выходных токов и напряжений в трехфазной актмвно-индуктивной нагрузке, соединенной звездой без нулевого провода

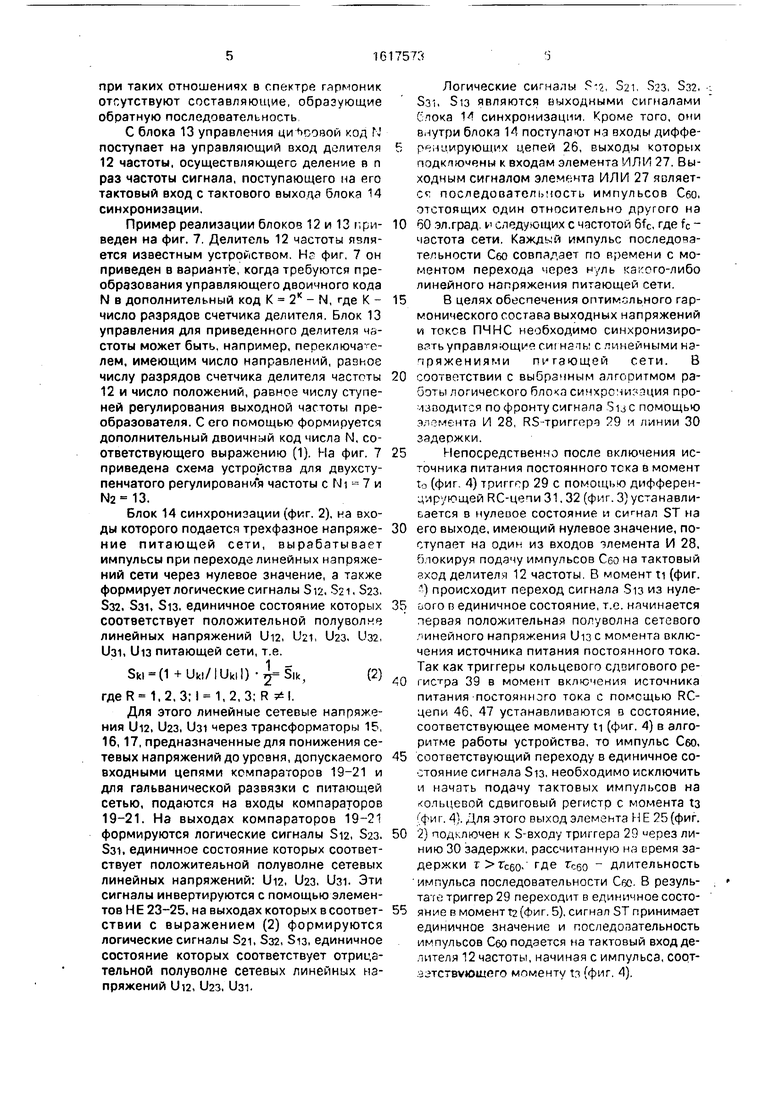

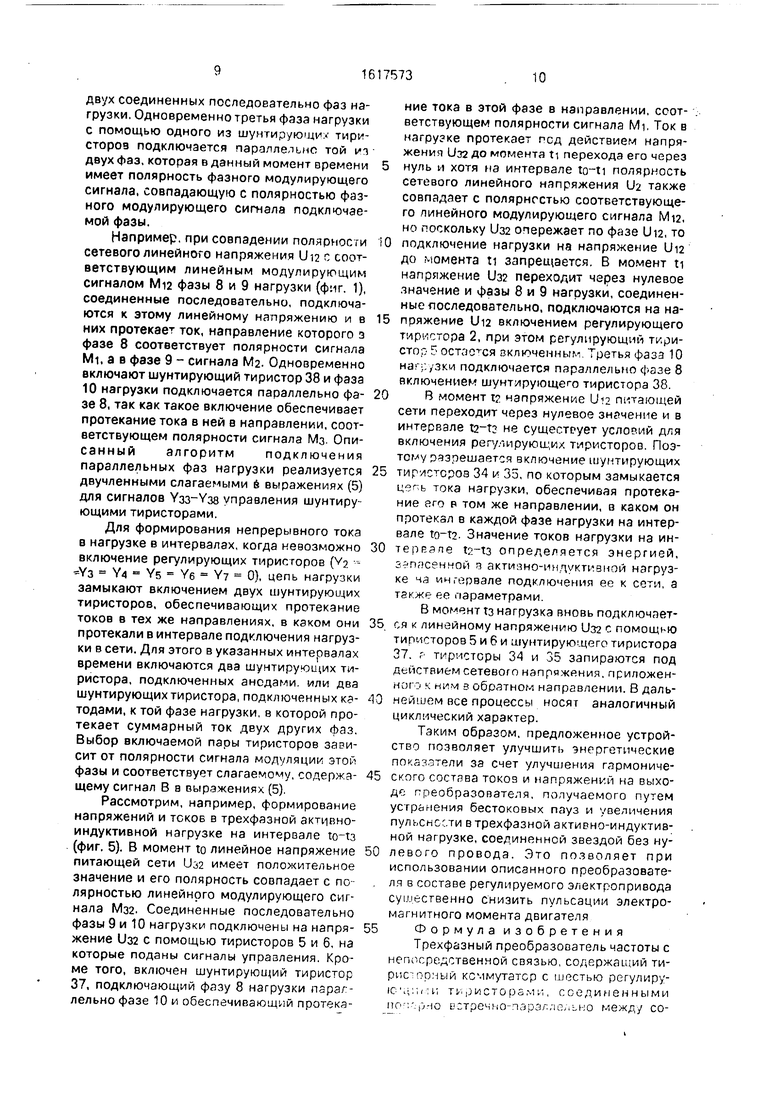

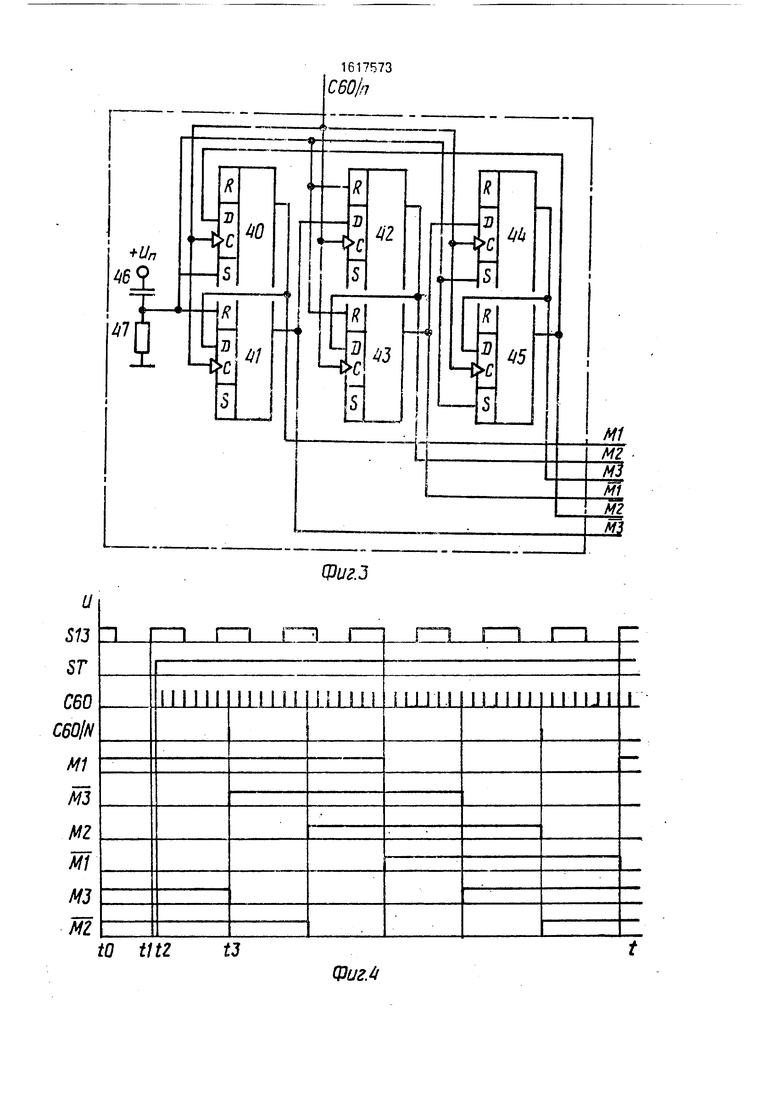

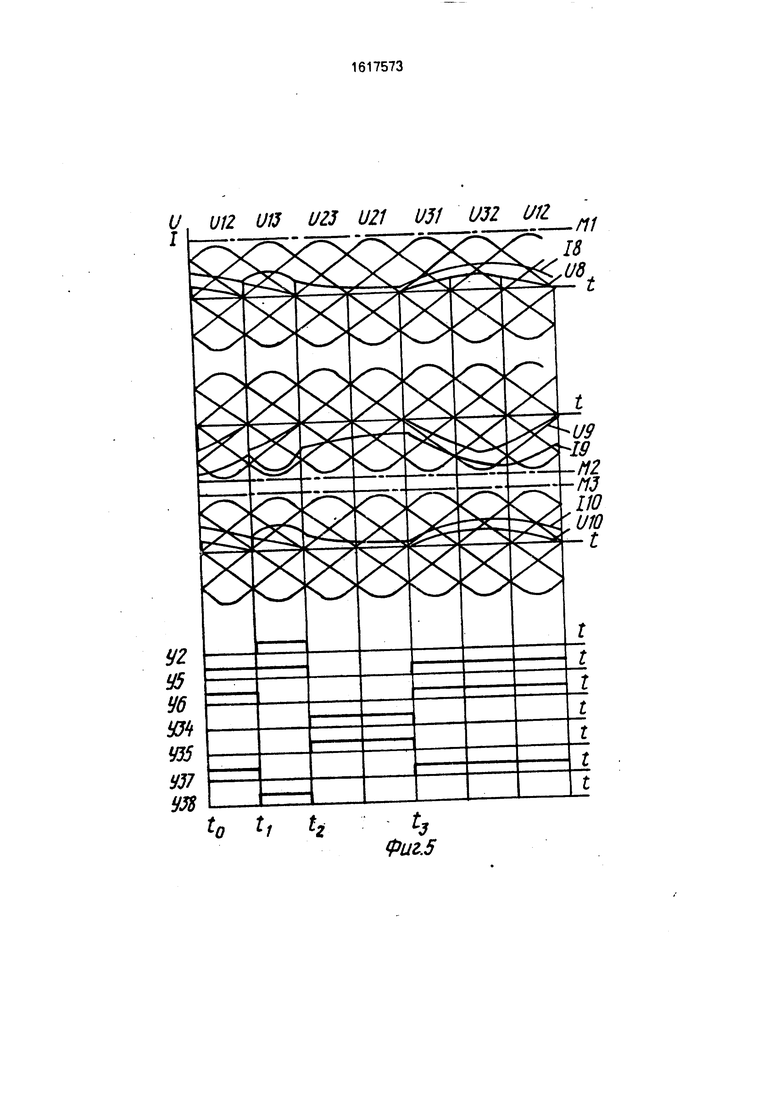

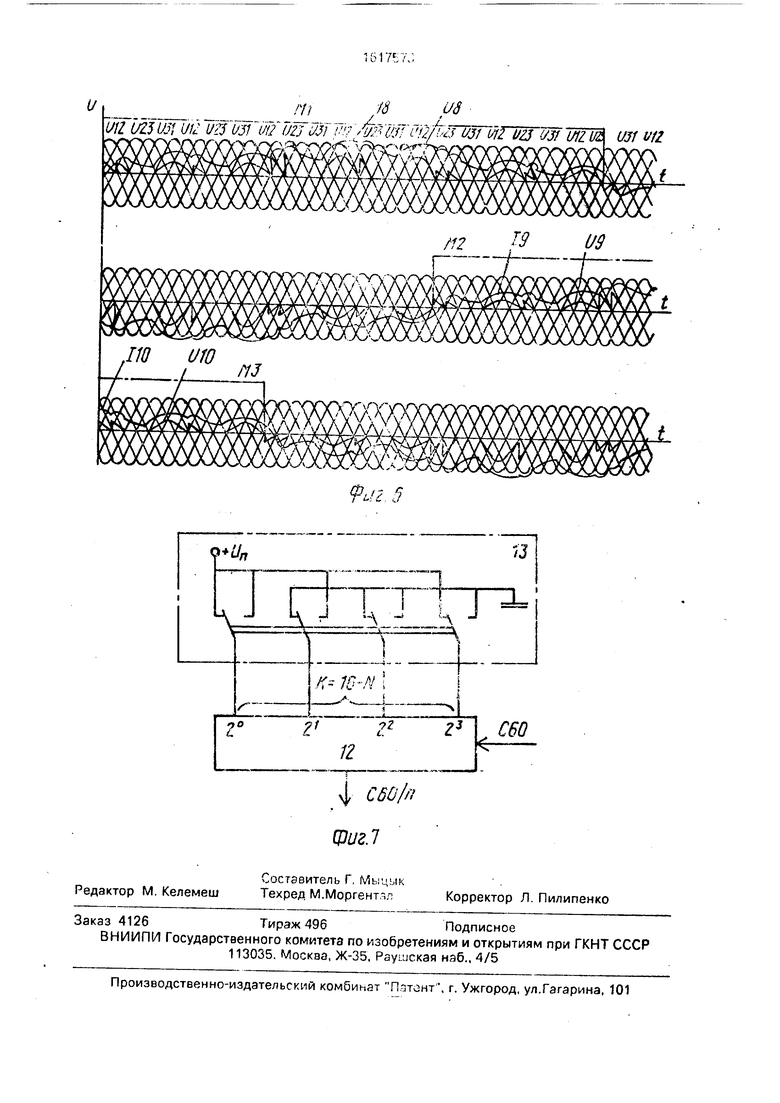

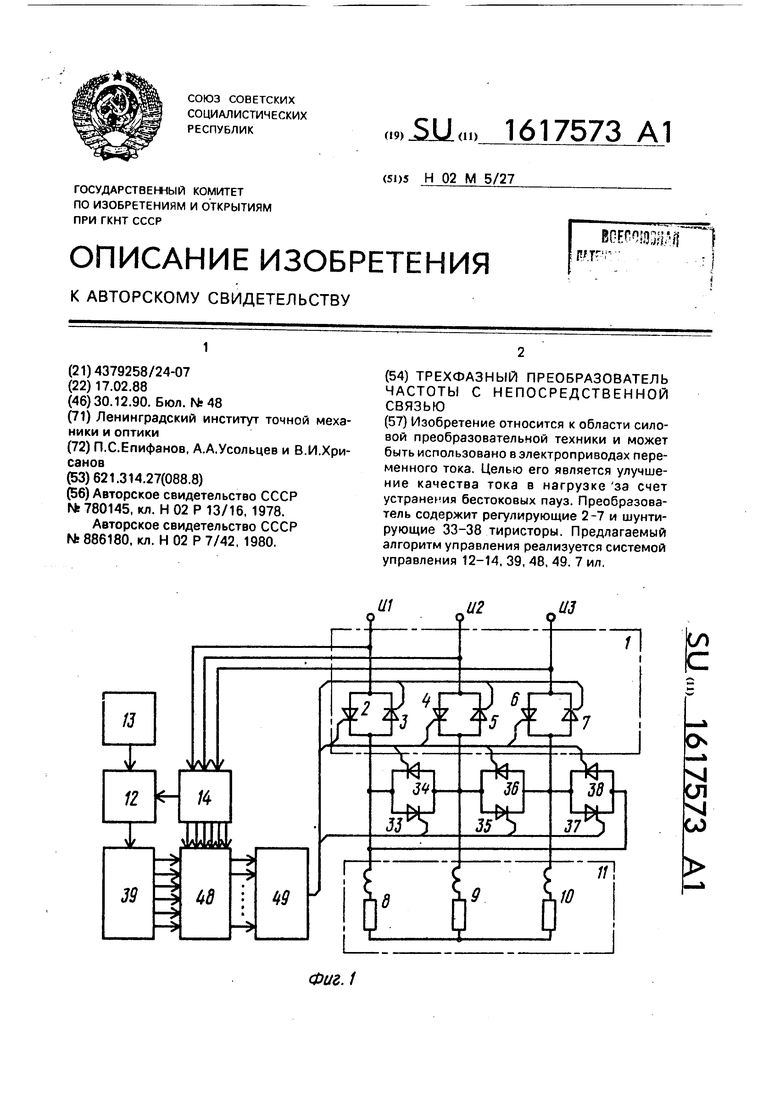

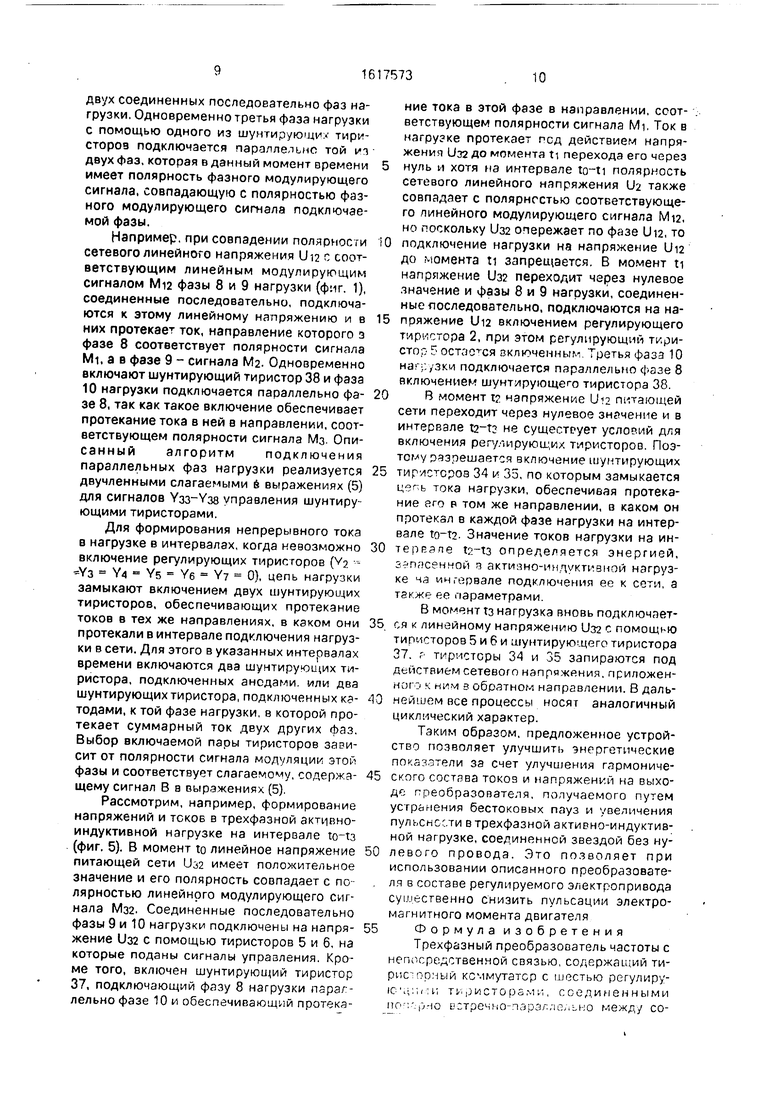

На фиг. 1 изображена структурная схе- ма трехфазного преобразователя частоты с непосредственной связью; на фиг. 2 - то же, блока синхронизации; на фиг. 3 - то же, кольцевого сдвигового регистра; на фиг. 4 - временные диаграммы работы блока синх- ронизации и кольцевого сдвигового регистра; на фиг. 5 - временные диаграммы напряжений и токов на выходе преобразователя и сигналов управления тиристорами; на фиг. 6 - временные диаграммы напряже- НИИ и токов для случая соотношения частот питающей сети и частоты сигнала модуляции, равного 13; на фиг. 7 - пример реализации блока управления и делителя частоты.

Трехфазный преобразователь частоты с непосредственной связью (ПЧНС) включает в себя (фиг. 1} тиристорный коммутатор 1, содержащий шесть регулирующих тиристоров 2-7, соединенных попарно встречно-па- раллельно между собой и включенных о разрывы линейных проводов фзз 8-10 активно-индуктивной нагрузки 11, соединенной звездой без нулевого провода, делителя 12 частоты с переменным коэффи- циенюм деления, управляющий вход которого соединен с выходом блока 13 управления, и 14 синхронизации, сетевыми входами соединенный с источником питания.

Блок 14 синхронизации (фиг. 2) содер- жит трансформаторы 15-17, первичные обмотки которых подключены треугольником к линейным проводам питающей сети, а вторичные обмотки через резисторы 18 подключены соответственно к одному из входов компараторов 19-21. Вторые входы компараторов через резисторы 22 подключены к точке нулевого потенциала, а выходы - к входам элементов НЕ 23-25 и к входам дифференцирующих цепей 26. Выходы эле- ментов НЕ 23-25 также присоединены к входам соответствующих д фференцирую- щих цепей 26. Выходы всех дифференцирующих цепей 26 объединены на элемент

ИЛИ 27, а его выход подключен к входу элемента 2-Й 28, другой вход которого подключен к выходу RS-триггера 29. Вход S триггера 29 через линию 30 задержки подключен к выходу элемента НЕ 25. Вход R триггера 29 через резистор 31 подключен к точке нулевого потенциала, а через конденсатор 32 - к источнику питания постоянного тока. Выход элемента 2-Й 28 является тактовым выходом блока синхронизации и подключен к тактовому входу делителя 12 частоты (фиг. 1). Выходы компараторов 19- 21 и элементов НЕ 23-25 являются синхронизирующими выходами блока 14 синхронизации.

Преобразователь содержит также шесть шунтирующих тиристоров 33-38, соединенных попарно встречно-параллельно между собой и подключенных треугольником к линейным проводам всех фаз нагрузки 11,

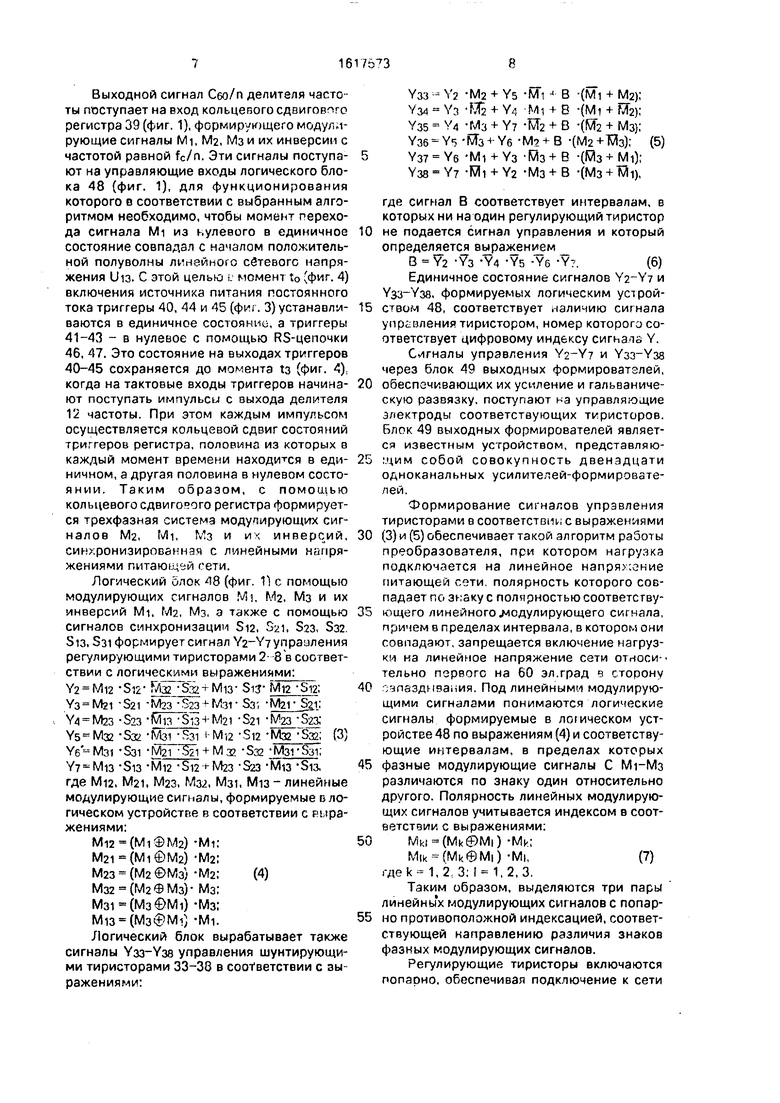

Выход делителя 12 частоты (фиг. 1) подключен к входу кольцевого сдвигового регистра 39. В состав кольцевого сдвигового регистра входят (фиг. 3) шесть соединенных последовательно D-триггеров 40-45, тактовые входы которых подключены к выходу делителя 12 частоты (фиг. 1). Входы S триггеров 40,44, 45 и входы R триггеров 41 - 43 через конденсатор 46 подключены к истон- нику питания постоянного тока, а через резистор 47 - к точке нулевого потенциала. Выходы триггеров 40-45 подключены к соответствующим управляющим входам логического блока 48, шесть синхронизирующих входов которого соединены с шестью соответствующими в ходами блока 14 синхронизации (фиг. 1).

Выходы логического блока 48 соединены с двенадцатью соответствующими входами блока 49 выходных формирователей, двенадцать выходов которого подключены к управляющим электродам, соответствующих регулирующих и шунтирующих тиристоров.

Трехфазный преобразователь частоты с непосредственной связью работает следующим образом.

Блок 13 управления (фиг. 1) вырабатывает цифровой код N, соответствующий отношению п частоты питающей сети к частоте основной гармонической составляющей напряжения на выходе ПЧНС, определяемому выражением

п fc/fi 6k + 1 при k 1,2,3..., (1) где fc - частота сетевого напряжения;

f 1 - частота основной гармонической составляющей выходного напряжения преобразователя.

Выбор кратности частот п, определяемый выражением (1) объясняется тем, что

при таких отношениях в спектре гармоник отсутствуют составляющие, образующие обратную последовательность

С блока 13 управления ци оовой код N поступает на управляющий вход делителя 12 частоты, осуществляющего деление в п раз частоты сигнала, поступающего на его тактовый вход с тактового выхода блока 14 синхронизации.

Пример реализации блоков 12 и 13 1фи- веден на фиг. 7. Делитель 12 частоты является известным устройством. НЕ фиг. 7 он приведен в варианте, когда требуются преобразования управляющего двоичного кода N в дополнительный код К 2 - N, где К - число разрядов счетчика делителя. Блок 13 управления для приведенного делителя частоты может быть, например, переключа- е- лем, имеющим число направлений, равное числу разрядов счетчика делителя частоты 12 и число положений, равное числу ступеней регулирования выходной частоты преобразователя. С его помощью формируется дополнительный двоичный код числа N, соответствующего выражению (1). На фиг. 7 приведена схема устройства для двухступенчатого регулировани я частоты с Ni 7 и .

Блок 14 синхронизации (фиг. 2). на входы которого подается трехфазное напряже- ние питающей сети, вырабатывает импульсы при переходе линейных напряжений сети через нулевое значение, а также формирует логические сигналы Si2, 821, S23, 5з2, 5з1. Si3, единичное состояние которых соответствует положительной полуволне линейных напряжений Ui2, Uzi, U23. из2, U31, Ui3 питающей сети, т.е.

1 о(2)

Ski (1+Uki/IUkil)

где R 1.2.3:1 1,2, 3; R i I.

Для этого линейные сетевые напряжения Ui2. U23. U31 через трансформаторы 15, 16,17, предназначенные для понижения сетевых напряжений до уровня, допускаемого входными цепями компараторов 19-21 и для гальванической развязки с питающей сетью, подаются на входы компараторов 19-21. На выходах компараторов 19-21 формируются логические сигналы Si2, 823. 5з1, единичное состояние которых соответствует положительной полуволне сетевых линейных напряжений: Ui2, U23, U3i. Эти сигналы инвертируются с помощью элементов НЕ 23-25. на выходах которых в соответ- ствии с выражением (2) формируются логические сигналы S2i. 832, , единичное состояние которых соответствует отрицательной полуволне сетевых линейных напряжений и 12, U23. U31.

:

0 5 0 5

0 5

0

5 0 5

Логические сигналы S-г, S2i, S23. Зз2, Зз1, Si3 являются выходными сигналами блока И синхронизации. Кроме того, они внутри блока 14 поступают на входы дифференцирующих цепей 26, выходы которых подключены к входам элемента ИЛИ 27. Выходным сигналом элемента ИЛИ 27 яоляет- ся последовательность импульсов СбО, отстоящих один относительно другого на 60 эл.град. 1-1 следую1цих с частотой 6fc, где fc - частота сети. Каждый импульс последовательности Сбо совпадает по времени с моментом перехода через нуль какого-либо линейного напряжения питающей сети.

В целях обеспечения оптимального гармонического состава выходных напряжений и токсв ПЧНС необходимо синхронизировать управляющие сиг напы с линейными напряжениями питающей сети. В соответствии с выбранным алгоритмом работы логического блока синхрсниззция про- 1зподится по фронту сигнала Si3C помощью элемента И 28, RS-триггера 29 и линии 30 задержки.

Непосредственно после включения источника питания постоянного тока в момент То (фиг, 4) триггер 29 с помощью дифференцирующей ВС-цепи31.32 (фиг. 3) устанавливается в нулеоое состояние и сигнал ST на его выходе, имеющий нулевое значение, поступает на один из входов элемента И 28. блокируя подачу импульсов Сео на тактовый вход делителя 12 частоты. В момент ti (фиг. л) происходит переход сигнала Si3 из нулевого D единичное состояние, т.е. начинается первая положительная полуволна сетевого линейного напряжения Ui3 с момента включения источника питания постоянного тока. Так как триггеры кольцевого сдоигового регистра 39 в момент включения источника питания постоянного тока с помощью RC- цепи 46. 47 устанавливаются в состояние, соответствующее моменту ti (фиг. 4) в алгоритме работы устройства, то импульс Сбо. соответствующий переходу в единичное состояние сигнала Si3, необходимо исключить и начать подачу тактовых импульсов на кольцевой сдвиговый регистр с момента тз | фи г. 4). Для этого выход элемента И Е 25 (фиг. 2) подключен к S-входу триггера 29 «ерез линию 30 задержки, рассчитанную на время задержки г Тсбо- где Гсбо длительность импульса последовательности Сбс. В резуль- , татй триггер 29 переходит в единичное состояние в момент Т2 (фиг. 5). сигнал ST принимает единичное значение и последовательность импульсов СбО подается на тактовый вход делителя 12 частоты, начиная с импульса, соот- зэтствуюшего моменту t3 (фиг. 4).

Выходной сигнал Сео/п делителя частоты п эступает на вход кольцевого сдвигового регистра 39 (фиг. 1), формирующего модул;1- рующие сигналы Mi, М2, Мз и их инверсии с частотой равной fc/n. Эти сигналы поступают на управляющие входы логического блока 48 (фиг. 1), для функционирования которого в соответствии с выбранным алгоритмом необходимо, чтобы момент перехода сигнала Mi из нулевого в единичное состояние совпадал с началом положительной полуволны линейного сетевого напряжения Ui3. С этой целью е момент to (фиг. 4) включения источника питания постоянного тока триггеры 40, 44 и 45 (фиг. 3) устанавливаются в единичное состояние, а триггеры 41-43 - в нулевое с помощью RS-цепочки 46, 47. Это состояние на выходах триггеров 40-45 сохраняется до момента ta (фиг. 4), когда на тактовые входы триггеров начинают поступать импульсы с выхода делителя 12 частоты. При этом каждым импульсом осуществляется кольцевой сдвиг состояний триггеров регистра, половина из которых в каждый момент времени находится в единичном, а другая половина в нулевом состо- янии. Таким образом, с помощью кольцевого сдвигового регистра формируется трехфазная система модулирующих сигналов М2, MI, Мз и их инверсий, синхронизированная с линейными напряжениями питающей сети.

Логический олок 48 (фиг. 11 с помощью модулирующих сигналов Mi, М2, Мз и их инверсий MI, М2, Мз, а также с помощью сигналов синхронизации Si2, . 823, 5з2, Si3,5з1 формирует сигнал Y2-Y7 управления регулирующими тиристорами 2- 8 в соответствии с логическими выражениями:

Sl2- 821 М23 523

Y2 Ml2

M13ГЛзг

Mi2 312; S3 ,

М2Г S2.1J

S23;

S31 i-M-12 -512 -Maz -532;

(3)

Y4 M23 -523 + M21 -521 532

Ye - Мз1 -531 , + M 32 -532 :M3iJmY7 Ml3 513 Ml2 Sl2 + M23 823 Mw 513,

где Mi2, M21, M23, Мз2, Мз1, Mi3- линейные модулирующие сигналы, формируемые в логическом устройстве в соответствии с выражениями:

Mi2 (Mi®M2) -Mi:

M21(Ml€)M2) М2;

М23 () М2;(4)

Мз2 (М2ФМз)- Мз:

Мз1 (Мз©М1) -Мз:

М13 (МзФМ1)-Ml.

Логический блок вырабатывает также сигналы Y33-Y38 управления шунтирующими тиристорами 33-38 в cootвeтcтвии с выражениями:

0

5

0

0

5

0

5

0

5

Y33 - Y2 М2 + Y5 -Ml - в -(Ml + М2);

V34 Y3 + Y4 Ml + в -(Ml + М2):

Y35 - Y4 -Мз + Y + в -(2 + Мз); Y36 Y5 М з + Y6 -Мз + в (М2 ); (5) Y37 Y6 -Ml + Y3 -Мз + в -(Мз + Mi); Y38 Y -RIi + Y2 -Мз + В -(Мз + Ml),

где сигнал В соответствует интервалам, в которых ни на один регулирующий тиристор не подается сигнал управления и который определяется вь ражением

B Y2 -73 Y4 -Ys -Ye -Y.(6)

Единичное состояние сигналов Y2-Y7 и Y33-Y38, формируемых логическим устройством 48, соответствует наличию сигнала управления тиристором, номер которого соответствует цифровому индексу сигнала Y.

Сигналы управления Y2-Y7 и Y33-Y38 через блок 49 выходных формирователей, обеспечивающих их усиление и гальваническую развязку, поступают на управляющие электроды соответствующих тиристоров. Блок 49 выходных формирователей является известным устройством, представляющим собой совокупность двенадцати одноканальных усилителей-формирователей.

Формирование сигналов управления тиристорами в соответствии с выражениями (3) и (5) обеспечивает такой алгоритм работы преобразователя, при котором нагрузка подключается на линейное напря :;ение питающей сети, полярность которого совпадает по зк;аку с полярностью соответствующего линейного/модулирующего сигнала, примем в пределах интервала, в котором они совпадают, запрещается включение нагрузки на линейное напряжение сети относи- тельно первого на 60 эл.град в сторону очпаздивапия. Под линейными модулирующими сигналами понимаются логические сигналы формируемые в логическом устройстве 48 по выражениям (4) и соответствующие интервалам, в пределах которых фазные модулирующие сигналы С Mi-Мз различаются по знаку один относительно другого. Полярность линейных модулирующих сигналов учитывается индексом в соответствии с выражениями:

Mki (Mk©Mi) -Mk;

Mik (Mk©Mi)-Ml,(7)

гдek 1,2, 3: 1,2, 3.

Таким образом, выделяются три пары линейны х модулирующих сигналов с попарно противоположной индексацией, соответствующей направлению различия знаков фазных модулирующих сигналов.

Регулирующие тиристоры включаются попарно, обеспечивая подключение к сети

двух соединенных последовательно фаз нагрузки, Одновременно третья фаза нагрузки с помощью одного из шунтирующих тиристоров подключается параллельно той из двух фаз. которая в данный момент времени имеет полярность фазного модулирующего сигнала, совпадающую с полярностью фазного модулирующего сигнала подключаемой фазы.

Например, при совпадении полярности сетевого линейного напряжения Ui2 с соответствующим линейным модулирующим сигналом Mi2 фазы 8 и 9 нагрузки (фиг. 1), соединенные последовательно, подключаются к этому линейному напряжению и в них протекает ток, направление которого з фазе 8 соответствует полярности сигнала MI, а в фазе 9 - сигнала Ма. Одновременно включают шунтирующий тиристор 38 и фаза 10 нагрузки подключается параллельно фазе 8, так как такое включение обеспечивает протекание тока в ней в направлении, соответствующем полярности сигнала Мз. Описанный алгоритм подключения параллельных фаз нагрузки реализуется двучленными слагаемыми 6 выражениях (5) для сигналов Узз-Узз управления шунтирующими тиристорами.

Для формирования непрерывного тока в нагрузке в интервалах, когда невозможно включение регулирующих тиристоров (Vj -- Y3 Y4 YE Ye Yy 0). цепь нагрузки замыкают включением двух шунтирующих тиристоров, обеспечивающих протекание токов в тех же направлениях, в каком они протекали в интервале подключения нагрузки в сети. Для этого в указанных интеовалах времени включаются два шунтирующих тиристора, подключенных анодами, или два шунтирующих тиристора, подключенных катодами, к той фазе нагрузки, в которой протекает суммарный ток двух других фаз. Выбор включаемой пары тиристоров зависит от полярности сигнала модуляции этой фазы и соответствует слагаемому, содержащему сигнал В в выражениях (5),

Рассмотрим, например, формирование напряжений и тсков в трехфазной активно- индуктивной нагрузке на интервале to-тз (фиг. 5). В момент to линейное напряжение питающей сети из2 имеет положительное значение и его полярность совпадает с полярностью линейного модулирующего сигнала Мз2, Соединенные последовательно фазы 9 и 10 нагрузки подключены на напряжение U32 с помощью тиристоров 5 и 6. на которые поданы сигналы управления. Кроме того, включен шунтирующий тиристор 37, подключающий фазу 8 нагрузки пзраг- лельно фазе 10 и обеспечивающ зй протекание тока в этой фазе в направлении, соответствующем полярности сигнала MI, Ток в нагрузке протекает под действием напряжения 1/32 до момента ti перехода его через 5 нуль и хотя на интервале to-ti полярность сетевого линейного напряжения U2 также совпадает с полярностью соответствующего линейного модулирующего сигнала Mi2. но поскольку U32 опережает по фазе Ui2, то iO подключение нагрузки на напряжение Ui2 до момента ti запрещается, В момент ti напряжение из2 переходит через нулевое значение и фазы 8 и 9 нагрузки, соединенные последовательно, подключаются на на- 15 пряжение Ui2 включением регулирующего тиристора 2, при этом регулирующий тиристор 5 остас ся включенным. Третья фаза 10 наг -.узки подключается параллельно фазе 8 включением шунтирующего тиристора 38, 20 В момент тг напряжение Ui2 питающей сети переходит через нулевое значение и в интервале t2-T3 не существует условий для включения регулирующих тиристоров. Поэтому разрешается включение 1иунтирующих 25 тиристоров 34 и 35. по которым замыкается цепь тока нагрузки, обеспечивая протекание его р том же направлении, в каком он протекал в каждой фазе нагрузки на интервале to-T2, Значение токов нагрузки на ин- 30 терЕэпе t2-t3 определяется энергией. запасенhfoй з актизно-инлуктивиой нагрузке ча ичгйрвале подключения ее к сети, а также ее параметрами.

В момент тз нагрузка вновь подключает- 35 ся к линейному напряжению U32 с помощью тиристоров 5 и 6 и шунтирующего тиристора 37. , тиристоры 34 и 35 запираются под действием сетевого напряжения, приложенного к ним 3 обратном направлении. В даль- 40 нейшем все процессы носят аналогичный циклический характер.

Таким образом, предложенное устройство позволяет улучшить энергетические показатели за счет улучшения гармониче- 5 СКОРО состсзва токоз и напряжений на выходе гтреобразователя, получаемого путем устранения бестоковых пауз и увеличения пульснссти в трехфазной активно-индуктивной нагрузке, соединенной звездой без ну- 0 левого провода. Это позволяет при использовании описанного преобразовате- . ля в составе регулируемого электропривода суш.ественно снизить пульсации электромагнитного момента двигателя 5Формула изобретения

Трехфазный преобразователь частоты с непосредственной связью, содержащий ти- ристорный коммутатор с шестью регулиру- 1СЧ ;;гП1 ту оистора,ми, соединенными no-: :|jHo встреч110-парэлле;;ьно между собой и включаемыми в разрывы линейных проводов всех фаз активно-индуктивной нагрузки, блок управления, выполненный фор- мирующим цифровой код N, соответствующий отношению п частоты пи- тающей сети к частоте основной гармонической составляющей на выходе преобразователя, выход которого соединен с управляющим входом делителя частоты с переменным коэффициентом деления, так- товый вход которого подключен к тактовому выходу блока синхронизации, тремя входами подключенного к питающей сети, отличающийся тем, что, с целью улучшения энергетических показателей за счет устра- нения бестоковых пауз и увеличения пульс- ности напряжения и токов в трехфазной активно-индуктивной нагрузке, соединенной звездой без нулевого провода, в преобразователь введены шесть шунтирующих тиристоров, соединенных попарно встречно-параллельно между собой и подключаемых треугольником к линейным проводам трехфазной активно-индуктивной нагрузки, в блок синхронизации введены формирова- тели логических сигналов Si2, Sai, 823. 5з2, 5з1, Si3, единичное состояние которых соответствует положительной полуволне линейных напряжений Ui2. Uai, U23, U32, U31, Uis питающей сети, формируемых по логине- ским выражениям

- ТОП -5

1-1,2,3;

k-1,2,3;

I .

кольцевой сдвиговый регис гр с пар1афазны- ми выходами: Mi, Mi, М2, М2, Мз, Мз, вход которого соединен с выходом делителя частоты, логический блок, шесть управляющих входов которого соединены с соответствующими выходами кольцевого сдвигового регистра, шесть синхронизирующих входов - с шестью соответствующими выходами блока синхронизации, а двенадцать выходов Y2-Y7, УЗЗ-УЗЗ через блок усилителей-формирователей подключены к соответствующим управляющим злектродам регулирующих и шунтирующих тиристоров, причем аппаратурная реализация указанного логического блока и связи между его вхо- дами и выходами определяются следующими выражениями:

Sl2 S32 + M13 -513 -М12 -512; S21 -N23 -823+ М31

Ml3 -513+М21

Мз1 831 + Mi2

М21 821 + Мз2 Mi2 812 + М23

Y2 М12 УЗ М21 Y/l M23 -823 -832 -831 Y7 Mi3 -813 где

Mi2 ()-Mi;

M21 (М1фМ2) -Ma;

М2з (М2@Мз) -Мг:

Мз2 {М2фМз) -Мз;

Мз1 {Мз6-)М1) -Мз;

М1з {Мз€)М1) -MI,

Y33 Y2 M2-bY5

8i3

8з1

821 8l2 832 823

M21 82i:

M23 823:

Мз2 8з2: Мз1 8з1: Mi3 8i3.

Ml-I-B-(Mi+ М2);

M2-I-Y4 Ml -I- В (Ml + M2); Мз +Y M2 + B(M2 + Мз); M3 + Y6 M2 + В(М2 + Мз);

Y34 Y3

Y35 Y4 Y36 YS

Y37 Ye MI -b Y3 Мз + В ( Мз + MI ); Y38 Yy Ml -ь Y2 Мз + В ( Мз + Ml).

гдеВ Y2 Y3 Vs -Ye Y.

to tm

t3

(Риг.

и

U12 U1} U15 (

Фиг.5

Hi

18

US

Ьгш (Ju u 5 u2fWfu2 j W b Moj2/i irujn/}2

9аг 5

18

US

Moj2/i iru

(/j/ ши/г

U31 т

Авторы

Даты

1990-12-30—Публикация

1988-02-17—Подача