фиг. 1

Изобретение относится к технике радиосвязи и может использоваться в различ- ных системах радиотелефонной и радиотелеграфной связи для контроля трактов супергетеродинного приемника в режиме дежурного приема.

Цель изобретения - повышение быстродействия.

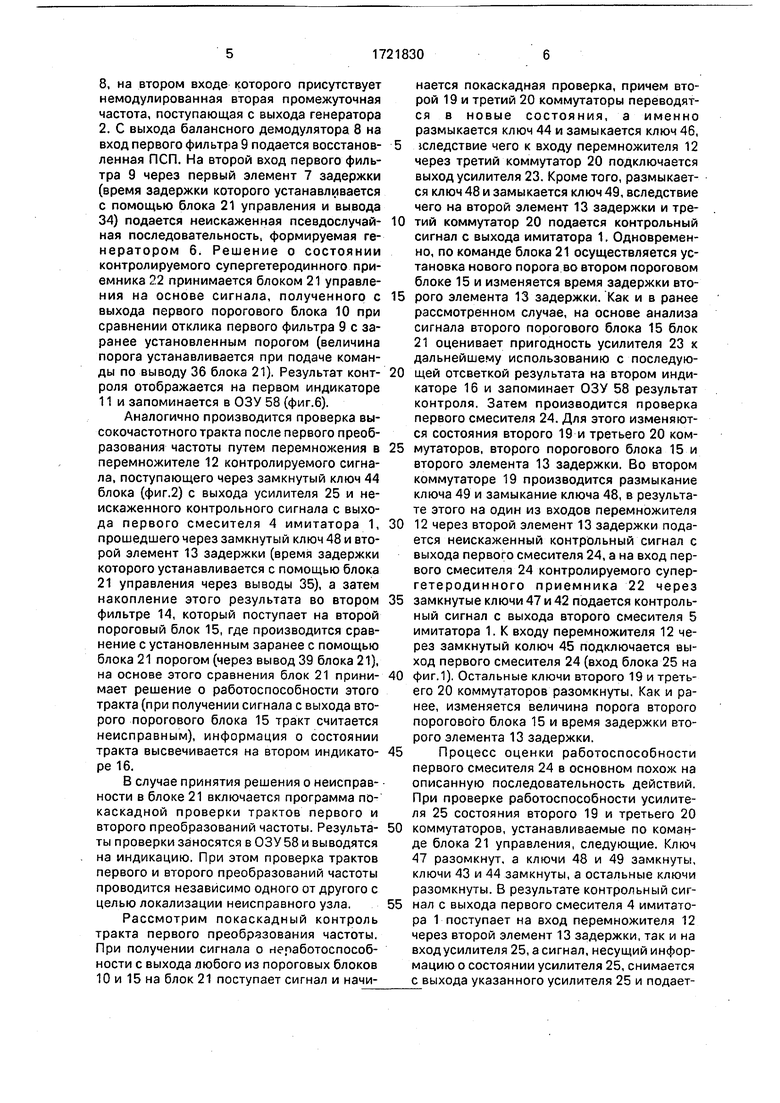

На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг.2 - вариант выполнения третьего коммутатора; на фиг.3 -.вариант выполнения второго коммутатора; на фиг.4 - вариант выполнения первого коммутатора; на фиг.5 - блок управления; на фиг.б - микроконтроллер.

Устройство для контроля работоспособ- ности супергетеродинного приемника (фиг. 1) содержит имитатор 1 входного сигнала, состоящий из генератора 2 промежуточной частоты, балансного модулятора 3, первого 4 и второго 5 смесителей, генератор 6 контрольного сигнала, первый элемент 7 задержки, балансный модулятор 8, первый фильтр 9, первый пороговый блок 10, первый индикатор 11, перемножитель 12, второй элемент 13 задержки, второй фильтр 14, второй пороговый блок 15, второй индикатор 16, первый коммутатор 17, элемент ИЛ И 18, второй 19 и третий 20 коммутаторы, блок 21 управления. Кроме того, показан контролируемый супергетеродинный приемник 22, состоящий из усилителя 23 высокой частоты, первого смесителя 24, усилителя 25 первой промежуточной частоты, второго смесителя 26,, усилителя 27 второй промежуточной частоты, детектора 28, первого 29 и второго 30 гетеродинов. Причем блок 21 управления имеет выводы 31-40.Третий коммутатор (фиг.2) 20 содержит два трехка- нальных коммутатора, каждый из которых имеет ключи 41-46. Второй коммутатор 19 (фиг.З) содержит ключи 47-49. Первый коммутатор 17 (фиг.4) содержит ключи 50-52.

Блок 21 управления (фиг.5) содержит микроконтроллер 53 и аналого-цифровой преобразователь (АЦП) 54,

Микроконтроллер 53 (фиг.б) содержит тактовый генератор 55, формирователь 56 сигнала Сброс, микропроцессор 57, оперативно запоминающий блок (ОЗУ) 58, постоянно запоминающий блок (ПЗУ) 59, параллельный интерфейс 60.

Устройство работает следующим образом.

После включения питания все элементы блока 21 (фиг.1) устанавливаются в исходное состояние (фиг.б). Тактовый генератор 55 с формирователем 56 формируют сигнал Сброс по импульсу от генератора 6. Микропроцессор 57 начинает генерировать адреса, считывать управляющую программу, записанную в ПЗУ 59 и выполнять ее. В соответствии с алгоритмом работы блок 21

выдает команды на проверку всего тракта супергетеродинного приемника 22 и тракта первого преобразования частоты (первый смеситель 24 и первый гетеродин 29). При этом в первом коммутаторе 17 (фиг.4) на

0 управляющих входах сигналы отсутствуют (низкий уровень) и ключи 50-52 разомкнуты. Второй коммутатор 19 (фиг.З) через замкнутые ключи 47 и 48 обеспечивает прохождение сигнала с выхода имитатора 1 (с выхода

5 второго смесителя 5) на вход третьего коммутатора 20 и контрольного сигнала с выхода первого смесителя 4 на вход второго; элемента 13 задержки. Третий коммутатор 20 (фиг.2) обеспечивает связь входа, под0 ключенного к второму коммутатору 19, с входом супергетеродинного приемника 22 через замкнутый ключ 41, а выход усилителя 25 - с одним из входов перемножителя 12 через замкнутый ключ 44. Остальные ключи

5 47-49, 42,43,46 и 45 второго и третьего коммутаторов разомкнуты.

Проверка работоспособности всего супергетеродинного приемника не отличается от контроля работоспособности с помощью

0 известного устройства.

Контрольный сигнал в виде промодули- рованной на выходе балансного модулятора 3 псевдослучайной последовательностью (ПСП) генератора 6 ПСП синусоидальной не5 сущей, формируемой генератором 2, поступает с выхода балансного модулятора 3 на вход первого 4 и второго 5 смесителей, в которых с помощью сигналов первого и второго гетеродинов происходит перенос спек0 тра сигнала генератора 2 на частоту настройки контролируемого приемника 22. Сформированный сигнал через второй 19 и третий 20 коммутаторы (замкнутые ключи 47 и 41) подается на вход усилителя 23 контро5 лируемого супергетеродинного приемника 22 и последовательно проходит через первый смеситель 24, на второй вход которого подается сигнал с выхода первого гетеродина 29, усиливается усилителем 25. Усилен0 ный сигнал через элемент ИЛИ 18 подается на вход второго смесителя 26, на второй вход которого поступает сигнал с выхода второго гетеродина 30, и усиливается в усилителе 27. С выхода усилителя 27 сигнал

5 поступает на вход детектора 28.

Контрольный сигнал, несущий информацию о состоянии высокочастотного тракта, с выхода усилителя 27 контролируемого супергетеродинного приемника 22 поступает на первый вход балансного демодулятора

8, на втором входе которого присутствует немодулированная вторая промежуточная частота, поступающая с выхода генератора 2. С выхода балансного демодулятора 8 на вход первого фильтра 9 подается восстановленная ПСП. На второй вход первого фильтра 9 через первый элемент 7 задержки (время задержки которого устанавливается с помощью блока 21 управления и вывода 34) подается неискаженная псевдослучайная последовательность, формируемая генератором 6. Решение о состоянии контролируемого супергетеродинного приемника 22 принимается блоком 21 управления на основе сигнала, полученного с выхода первого порогового блока 10 при сравнении отклика первого фильтра 9 с заранее установленным порогом (величина порога устанавливается при подаче команды по выводу 36 блока 21). Результат контроля отображается на первом индикаторе 11 и запоминается в ОЗУ 58 (фиг.6).

Аналогично производится проверка высокочастотного тракта после первого преобразования частоты путем перемножения в перемножителе 12 контролируемого сигнала, поступающего через замкнутый ключ 44 блока (фиг.2) с выхода усилителя 25 и неискаженного контрольного сигнала с выхода первого смесителя 4 имитатора 1, прошедшего через замкнутый ключ 48 и второй элемент 13 задержки (время задержки которого устанавливается с помощью блока 21 управления через выводы 35), а затем накопление этого результата во втором фильтре 14, который поступает на второй пороговый блок 15, где производится сравнение с установленным заранее с помощью блока 21 порогом (через вывод 3.9 блока 21), на основе этого сравнения блок 21 принимает решение о работоспособности этого тракта (при получении сигнала с выхода второго порогового блока 15 тракт считается неисправным), информация о состоянии тракта высвечивается на втором индикаторе 16.

В случае принятия решения о неисправности в блоке 21 включается программа покаскадной проверки трактов первого и второго преобразований частоты. Результаты проверки заносятся в ОЗУ 58 и выводятся на индикацию. При этом проверка трактов первого и второго преобразований частоты проводится независимо одного от другого с целью локализации неисправного узла.

Рассмотрим покаскадный контроль тракта первого преобразования частоты. При получении сигнала о неработоспособности с выхода любого из пороговых блоков 10 и 15 на блок 21 поступает сигнал и начинается покаскадная проверка, причем второй 19 и третий 20 коммутаторы переводятся в новые состояния, а именно размыкается ключ 44 и замыкается ключ 46,

следствие чего к входу перемножителя 12 через третий коммутатор 20 подключается выход усилителя 23. Кроме того, размыкается ключ 48 и замыкается ключ 49, вследствие чего на второй элемент 13 задержки и тре0 тий коммутатор 20 подается контрольный сигнал с выхода имитатора 1. Одновременно, по команде блока 21 осуществляется установка нового порога во втором пороговом блоке 15 и изменяется время задержки вто5 рого элемента 13 задержки. Как и в ранее рассмотренном случае, на основе анализа сигнала второго порогового блока 15 блок 21 оценивает пригодность усилителя 23 к дальнейшему использованию с поеледую0 щей отсветкой результата на втором индикаторе 16 и запоминает ОЗУ 58 результат контроля. Затем производится проверка первого смесителя 24. Для этого изменяются состояния второго 19 и третьего 20 ком5 мутаторов, второго порогового блока 15 и второго элемента 13 задержки. Во втором коммутаторе 19 производится размыкание ключа 49 и замыкание ключа 48, в результате этого на один из входов перемножителя

0 12 через второй элемент 13 задержки подается неискаженный контрольный сигнал с выхода первого смесителя 24, а на вход первого смесителя 24 контролируемого супергетеродинного приемника 22 через

5 замкнутые ключи 47 и 42 подается контрольный сигнал с выхода второго смесителя 5 имитатора 1. К входу перемножителя 12 через замкнутый колюч 45 подключается выход первого смесителя 24 (вход блока 25 на

0 фиг.1). Остальные ключи второго 19 и третьего 20 коммутаторов разомкнуты. Как и ранее, изменяется величина порога второго порогового блока 15 и время задержки второго элемента 13 задержки.

5 Процесс оценки работоспособности первого смесителя 24 в основном похож на описанную последовательность действий. При проверке работоспособности усилителя 25 состояния второго 19 и третьего 20

0 коммутаторов, устанавливаемые по команде блока 21 управления, следующие. Ключ 47 разомкнут, а ключи 48 и 49 замкнуты, ключи 43 и 44 замкнуты, а остальные ключи разомкнуты. В результате контрольный сиг5 нал с выхода первого смесителя 4 имитатора 1 поступает на вход перемножителя 12 через второй элемент 13 задержки, так и на вход усилителя 25, а сигнал, несущий информацию о состоянии усилителя 25, снимается с выхода указанного усилителя 25 и подается на второй вход перемножителя 12. С помощью блока 21 изменяется порог второго порогового блока 15 и время задержки второго элемента 13 задержки.

Как указано, параллельно с процессом контроля состояния тракта первого преобразования частоты производится проверка работоспособности тракта второго преобразования частоты. Для этого замыкается ключ 51 в первом коммутаторе 17 при разомкнутых ключах 50 и 52, и контрольный сигнал поступает с выхода балансного модулятора 3 на вход усилителя 27. Одновременно изменяются значения порога первого порогового блока 10 и время задержки первого элемента 7 задержки. Все указанные действия выполняются на основе команд, поступивших с выводов 33, 34 и 36 блока 21 управления. Контроль работоспособности усилителя 27 не отличается от описанного.

Если усилитель 27 исправен, то проводится контроль второго смесителя 26 вместе с усилителем 27. Для выполнения указанной проверки замыкается ключ 50, ключи 51 и 52 разомкнуты, устанавливаются новые значения порога первого порогового блока 10 и времени задержки первого элемента 7 задержки на основе команд блока 21 (через выводы 34 и 36). Контрольный сигнал снимается с выхода первого смесителя 4 имитатора 1 и подается через ключ 50 первого коммутатора 17, элемент ИЛИ 18 на вход второго смесителя 26. Сигнал, несущий информацию о состоянии второго смесителя 26 и усилителя 27, поступает с выхода усилителя 27 на вход балансного модулятора 8. Дальнейшие действия по определению пригодности указанных каскадов к использованию не отличаются от описанных.

Если же при проверке усилителя 27 установлен факт его неисправности, то для проверки работоспособности второго смесителя 26 замыкаются ключи 50 и 52 в первом коммутаторе 17, а ключ 51 находится в разомкнутом состоянии. Контрольный сигнал с выхода первого смесителя 4 имитатора 1 поступает через элемент ИЛИ 1.8 на вход второго смесителя 26, а контрольный сигнал, несущий информацию о состоянии второго смесителя 26, через ключ 52 поступает на вход балансного модулятора 8. В дальнейшем контроль работоспособности подобен описанному. Следует отметить, что при проверке второго смесителя 26 устанавливаются определенные значения порога в первом пороговом блоке 10 и времени задержки первого элемента 7 задержки.

Ф о р м у л а и з о б р е т е н и я

Устройство для контроля работоспособности супергетеродинного приемника, содержащее имитатор входного сигнала, состоящий из последовательно соединенных генератора промежуточной частоты, балансного модулятора, первого и второго смесителей, вторые входы которых соединены с выходами соответственно первого и второго гетеродинов контролируемого су0 пергетеродинного приемника, последовательно соединенные генератор контролируемого сигнала, второй выход которого соединен с вторым входом балансного модулятора имитатора входного сигнала,

5 и первый элемент задержки, последовательно соединенные балансный демодулятор, первый вход которого соединен с выходом усилителя второй промежуточной частоты контролируемого супергетеродин0 ного приемника, а второй вход соединен с выходом генератора промежуточной частоты имитатора входного сигнала, первый фильтр, второй вход которого соединен с выходом первого элемента задержки, пер5 вый пороговый блок и первый индикатор, первый коммутатор, первый выход которого соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходами усилителя пер0 вой промежуточной частоты контролируемого супергетеродинного приемника и первым входом второго смесителя контролируемого супергетеродинного приемника, последовательно соединенные второй эле5 мент задержки, перемножитель, второй фильтр, второй пороговый блок и второй индикатор, отличающееся тем, что, с целью повышения быстродействия, введены второй коммутатор, первый и второй ин0 формационные входы которого соединены соответственно с выходами первого и второго смесителей имитатора входного сигнала, блок управления, первый и второй входы которого соединены соответственно с вто5 рым выходом генератора контрольного сигнала и вторым выходом второго порогового блока, третий коммутатор, первый и второй информационные входы которого соединены соответственно с первым выходом вто0 рого коммутатора и выходом усилителя первой промежуточной частоты контролируемого супергетеродинного приемника, а первый, второй, третий и четвертый выходы третьего коммутатора соединены, соответ5 ственно с входом усилителя высокой частоты, входом первого смесителя, входом усилителя первой промежуточной частоты контролируемого супергетеродинного приемника и вторым вюдом перемножителя, второй выход второго коммутатора соединен с входом второго элемента задержки, второй выход первого порогового блока соединен с третьим входом блока управления, первый, второй, третий, четвертый, пятый, шестой и седьмой выходы блока управления соединены соответственно с управляющими входами второго порогового блока, третьего коммутатора, первого коммутатора, первого элемента задержки, первого порогового блока, второго элемента задержки и. второго

0

коммутатора, первый, второй и третий информационные входы первого коммутатора, соединены соответственно с выходами первого смесителя и балансного модулятора имитатора входного сигнала и с выходом усилителя второй промежуточной частоты контролируемого супергетеродинного приемника, вход усилителя второй промежуточной частоты которого соединен с вторым выходом первого коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля работоспособности супергетеродинного приемника | 1989 |

|

SU1626419A1 |

| Устройство для контроля работоспособности супергетеродинного приемника | 1989 |

|

SU1684932A1 |

| Устройство для контроля работоспособности супергетеродинного приемника | 1986 |

|

SU1394442A2 |

| Устройство для контроля работоспособности супергетеродинного приемника | 1990 |

|

SU1753608A2 |

| Устройство для контроля работоспособности супергетеродинного приемника | 1991 |

|

SU1818696A1 |

| Устройство для контроля работоспособности супергетеродинного приемника | 1991 |

|

SU1818697A1 |

| Устройство для контроля работоспособности супергетеродинного приемника | 1980 |

|

SU932632A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАБОТОСПОСОБНОСТИ СУПЕРГЕТЕРОДИННОГО ПРИЕМНИКА | 1988 |

|

RU2013008C1 |

| Устройство для контроля работоспособности супергетеродинного радиоприемника | 1985 |

|

SU1283988A1 |

| Устройство для контроля работоспособности супергетеродинного приемника | 1984 |

|

SU1192146A1 |

Изобретение относится к технике радиосвязи. Цель изобретения - повышение быстродействия. Для достижения поставленной цели в устройство введены два коммутатора 19 и 20 и блок 21 управления. Эти блоки позволяют проводить автоматически контроль работоспособности супергетеродинного приемника 22 как на верхнем, так и на нижнем уровне путем задания изменяющихся величин пороговых уровней и времен задержки, а также за счет подачи на отдельные каскады контрольного сигнала и съема их реакций с их выхода. 6 ил.

Квх.ЗА.23 к0х.й.2т квхбл.2б

K8mJZ бл.21

КВш.Вл.9 к 1. бл.П Фиг:1

К8ых.31 Ъл.21

Фиг.З

К8ы..бл.25

KW32 бл.21

iS

V

i-,

«а

sc

Фиг4

34 56 35 39 33 «

гутН-И-Н-Н-.-.

I J

53

I

&Й

f

IТГ |

-Н-Н-.-.

53

I

Kfr.6 40

WA

ШУ

f

Г

7738

Фиг. 5

Фиг. 6

| Устройство для контроля работоспособности супергетеродинного приемника | 1986 |

|

SU1394442A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-03-23—Публикация

1990-04-09—Подача