Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники..

Маломощные тиристоры нашли применение в качестве активных компонентов логических элементов промышленной автоматики.

По сравнению с транзисторами тиристоры имеют ряд существенных преимуществ: более широкий диапазон рабочих напряжений и токов, большой коэффициент усиления по току, свойство памяти (тиристор после включения помнит поданный на него сигнал), являясь ключевыми приборами, а не линейными усилителями, менее зависят от возможного ухудшения параметров..

Известны тиристорные логические элементы в дискретном исполнении, которые не содержат реактивных компонентов и питаются от трехфазной сети переменного тока. Эти элементы характеризуются следующими положительными особенностями:

не требуют стабилизированных источников питания, элемен ты работают при колебаниях напряжения питания сети в диапазоне от 0,5 до 1,2 UH и коэффициенте разветвления по выходу -5;

х| Ю XJ

ю о

имеют идеальную устойчивость по логическому нулю, так как тиристор после включения не чувствителен к помехам, и высокую устойчивость по логической единице - 8 В;

уровень внутренних коммутационных помех имеет минимально возможную величину, так как тиристор включается и выключается в рассматриваемых элементах при IT «0(Jn«0.

RS-триггер на этих элементах реализуется на двух тиристорных элементах ИЛИ- НЕ. В этом RS-триггере положительная обратная связь реализована благодаря тому, что выход первого логического элемента подключен к одному из входов второго логического элемента, выход которого подключен к одному из входов первого логического элемента и элементы ИЛИ-НЕ питаются от выпрямленных двухимпульс- ных напряжений, каждое длительностью 300 эл.град., сдвинутых друг относительно друга на 120 эл.град. При этом нулевые значения напряжения питания одного элемента перекрываются положительным напряжением на другом элементе и наоборот.

Эти элементы не содержат реактивных компонентов и поэтому пригодны для реализации в монолитном исполнении по стан- дартной технологии биполярных ТТЛ НС.

Однако эти элементы и соответственно RS-триггер. построенный на этих элементах, при их реализации в монолитном исполнении имеют недостаток, заключающийся в малой устойчивости к дестабилизирующим воздействиям по логической единице. Это объясняется уменьшением величины напряжения питания, что необходимо для уменьшения выделяемой в элементах мощности,

Тиристорные логические элементы с питанием от 3-фазной сети переменного тока послужили основой, на которой были разработаны и освоены в серийном производстве тиристорные динамические высокопомехо- устойчивые логические интегральные схемы серии К523, имеющие высокую помехоустойчивость в обоих логических состояниях. Питание ИС серии К523 осуществляется от источника импульсных взаимно перекры- вающихся двух или трехтактных трапецеидальных напряжений с амплитудой Ud % 68 ±10%.

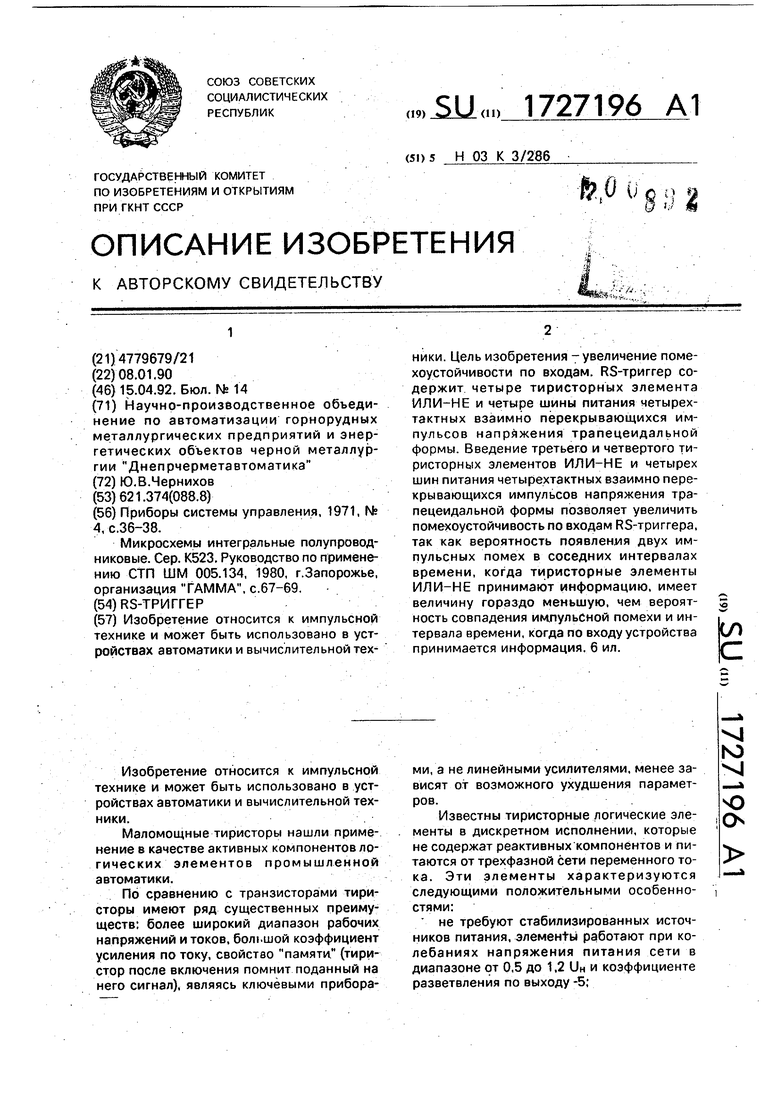

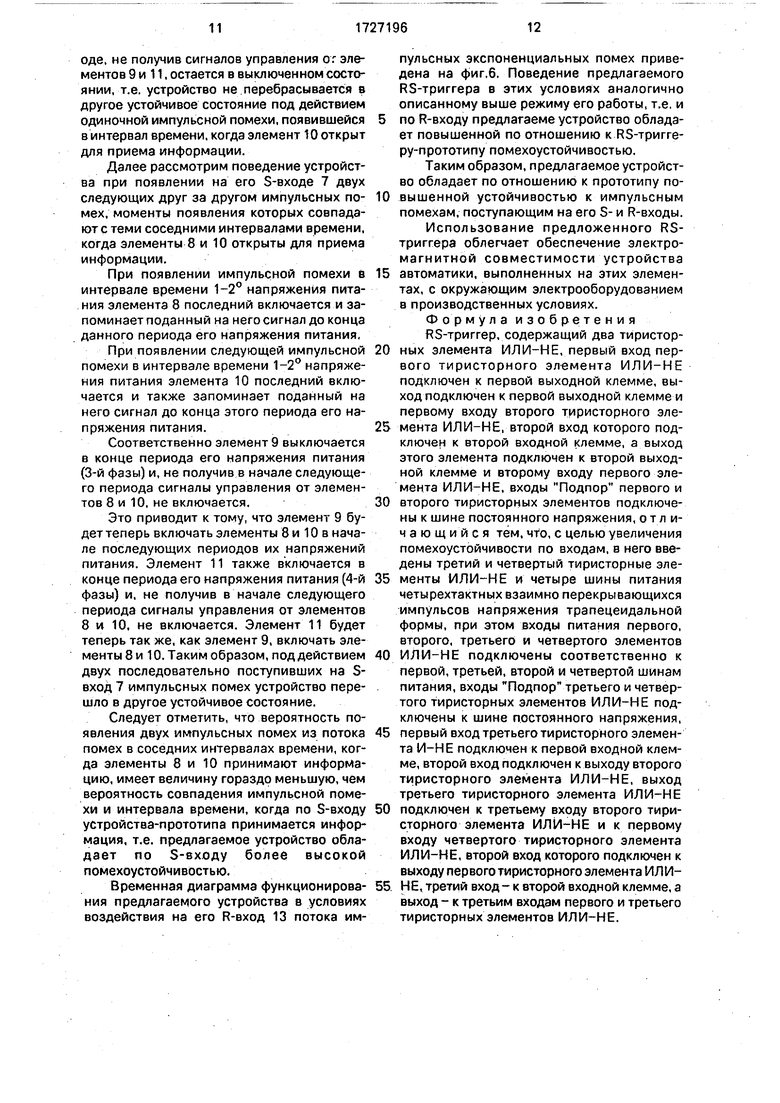

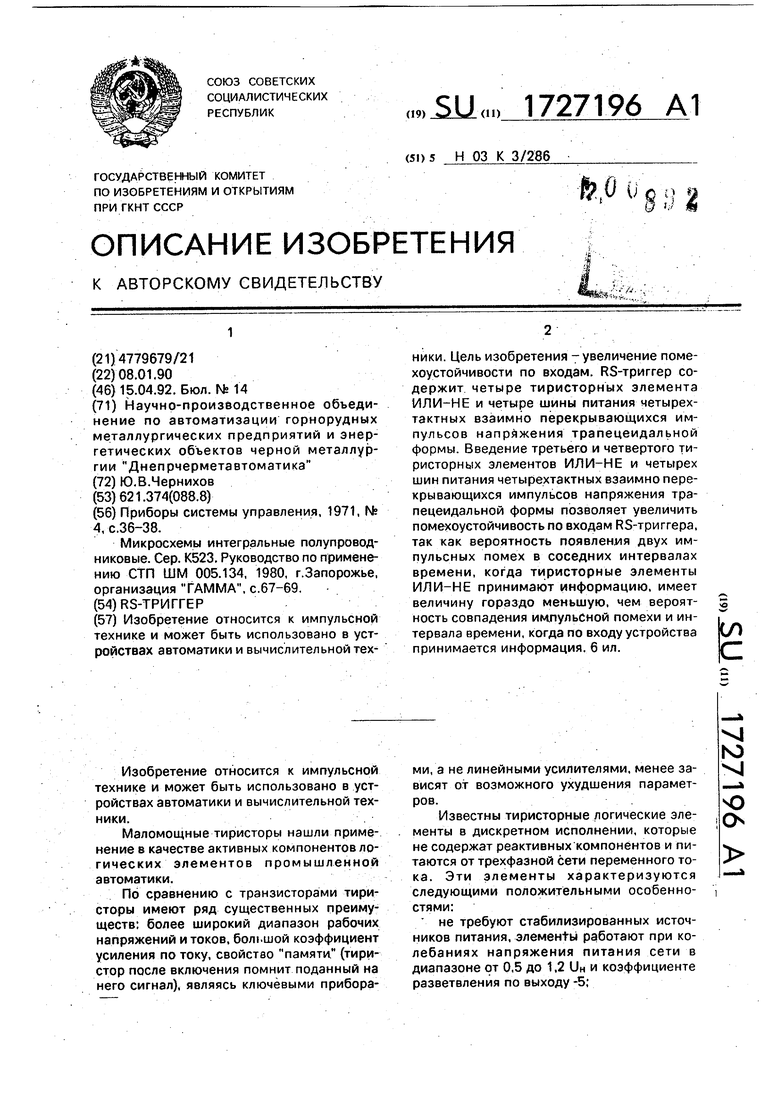

На фиг,1 приведена принципиальная схема базового элемента И С серии К523.

На фиг.1 обозначены; 1-4 - входы элемента; 5-15 - диоды; 16-25 - резисторы; 26-28 - транзисторы; 29 - тиристор; 30 - клемма для подключения напряжения подпора Упод; 31 - клемма для подключения импульсного трапецеидального напряжения питания; 32 - общая точка элемента; 33- выход элемента.

В составе логического элемента ИС серии К523 имеется узел защелки, выполненный на транзисторах 26 и 27, который обеспечивает включение элемента только в интервале времени 1-2° каждого периода его напряжения питания, что резко повышает порог срабатывания логического элемента Unop.1 до 25 В в интервале времени 2-360° его выключенного состояния. При подаче на вход элемента сигнала управления Uy, сдвинутого относительно напряжения питания, тиристор 29 включается и запоминает поданный на него сигнал до конца периода напряжения питания элемента. В этом состоянии логического элемента его порог срабатывания Unop.c 25 В, так как тиристор после включения благодаря внутренней положительной обратной связи нечувствителен к помехам по цепи управления.

Для повышения устойчивости интегральных тиристоров к импульсным помехам на их анодах используется как наиболее эффективный и экономический метод подавления эффекта

«U at

путем предварительного

заряда емкости центрального перехода тиристора от вспомогательного источника по- стоянного напряжения Ыпод, который подключается к неинформационному входу Подпор элемента.

При определении статических характеристик срабатывания логических ИС .различных серий наиболее достоверной является их оценка по методике, учитывающей мощность дестабилизирующих воздействий и механизм проникновения этих воздействий в систему автоматики (через емкостные или индуктивные связи, через электронное поле).

Выполненное по такой методике экспериментальное исследование ИС серии К523 показало, что максимальной устойчивостью ко всем видам дестабилизирующих воздействий в интервале времени 2-360° обладают ИС серии К523. В порядке уменьшения устойчивости остальные серии располагаются в следующем порядке: К5116. К 561, К155, К176. В интервале 0-2° максимальной устойчивостью обладают ИС серии К511. В порядке уменьшения устойчивости в этом интервале времени остальные серии располагаются в следующем порядке: К561, К523, К155, К176. Выполнение ИС серии К523 с использованием в качестве активных компонентов двуханодных тиристоров позволяет иметь в этом интервале времени устойчивость к дестабилизирующим воздействиям такую же, как и у серии К511. При этом следует отметить, что потребление мощности вентиля серии К523 составляет 40% потребления мощности вентиля серии К511.

Оценка помехоустойчивости тиристор- ной логической ИС ИЛИ-НЕ приведена в работе, где на основании математической модели процеса накапливания и рассасывания заряда в тиристоре логической ИС под действием входного импульса помехи предложена методика анализа помехоустойчивости тиристорной логической ИС ИЛИ-НЕ методом статистического моделирования на ЦВМ.

Помехоустойчивость тиристорной логической ИС определена как вероятность P(t) появления не менее одного одиночного сбоя за время т.. В качестве модели помех был принят поток экспоненциальных им- пульсов напряжения, экспериментально наблюдаемый на стане 350 металлургического завода им.Дзержинского. Этот поток имеет следующие статистические характеристики: распределение амплитуд импульсов описывается логнормальным законам (и Ud 8,83 В - оценка математического ожидания амплитудного значения импульса; 3,4 В -. оценка среднего квадратичного отклонения амплитудного значения импульса); распределение длительностей импульсов - законом Вейбулла ( fir 0,49 10 аС - оценка математического ожидания постоянной т. характеризующей спад экспоненциального импульса; 0,18 10 3С-оценка среднего квадратичного отклонения постоянной г); распределение появления импульсов во времени-законом Пуассона ( ,2 имп,/С - оценка интенсивности потока импульсных экспоненциальных помех).

В соответствии с предложенной методикой поток выбросов заряда Ош, накопленного в базах тиристора в интервалах времени 292,5 - 360°, 0 - 2° каждого периода напряжения питания и превышающих критический уровень Ош.кр., сравнивается со стационарным детерминированным пот током Хп, частота которого равна частоте питания тиристорных логических ИС, а дли- тельность каждого импульса равна длитель,- ности интервала (1-2°) напряжения питания, определяются области пересечения этих потоков, т.е. находится поток совмещенных импульсов Хс (сбоев) и определяются его статистические характеристики. Помехоустойчивость тиристорной логической ИС ИЛИ-НЕ при этом равна:

Рсб К523 (20с) - 0,12 (переход 1 /0);

Рсб К523 (20с) 0,15 (переход 0/1). Для сравнения отметим, что при тех же параметрах потока помех Pc6K5ii (20с) - 0,95 для обоих переходов.

5 Прототипом предлагаемого устройства является .RS-триггер, построенный на двух описанных выше тиристорных интегральных элементах ИЛИ-НЕ серии К523 (К523 ЛЕ1).

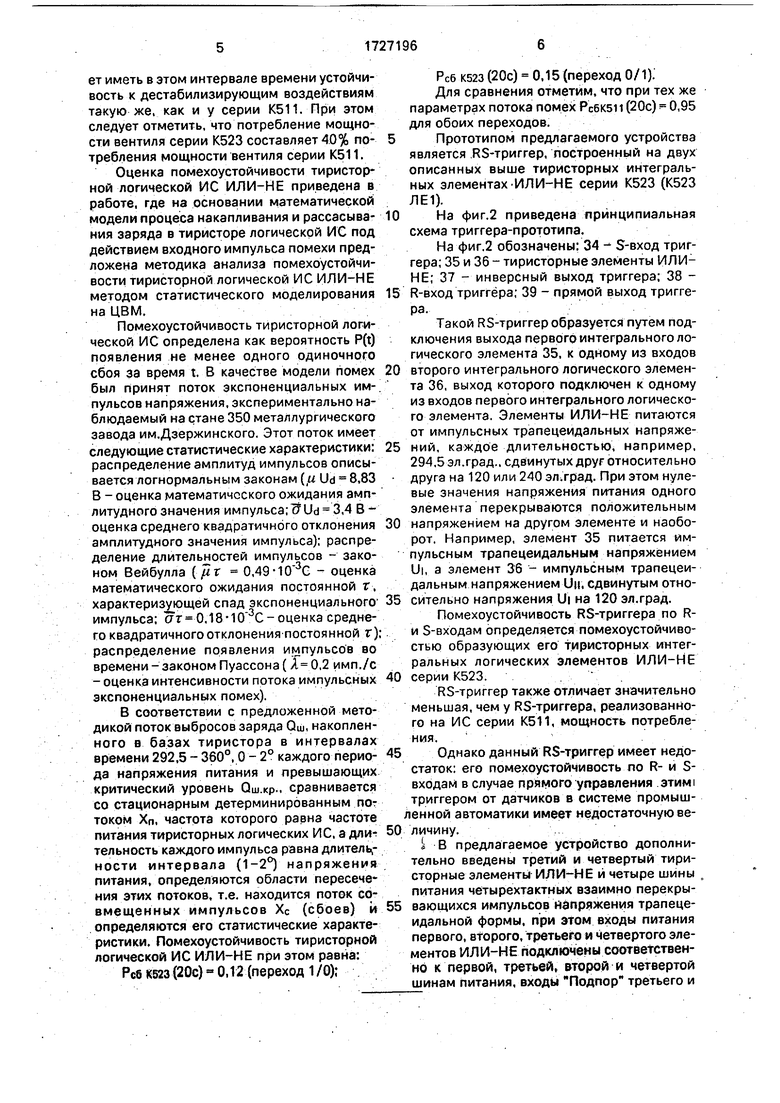

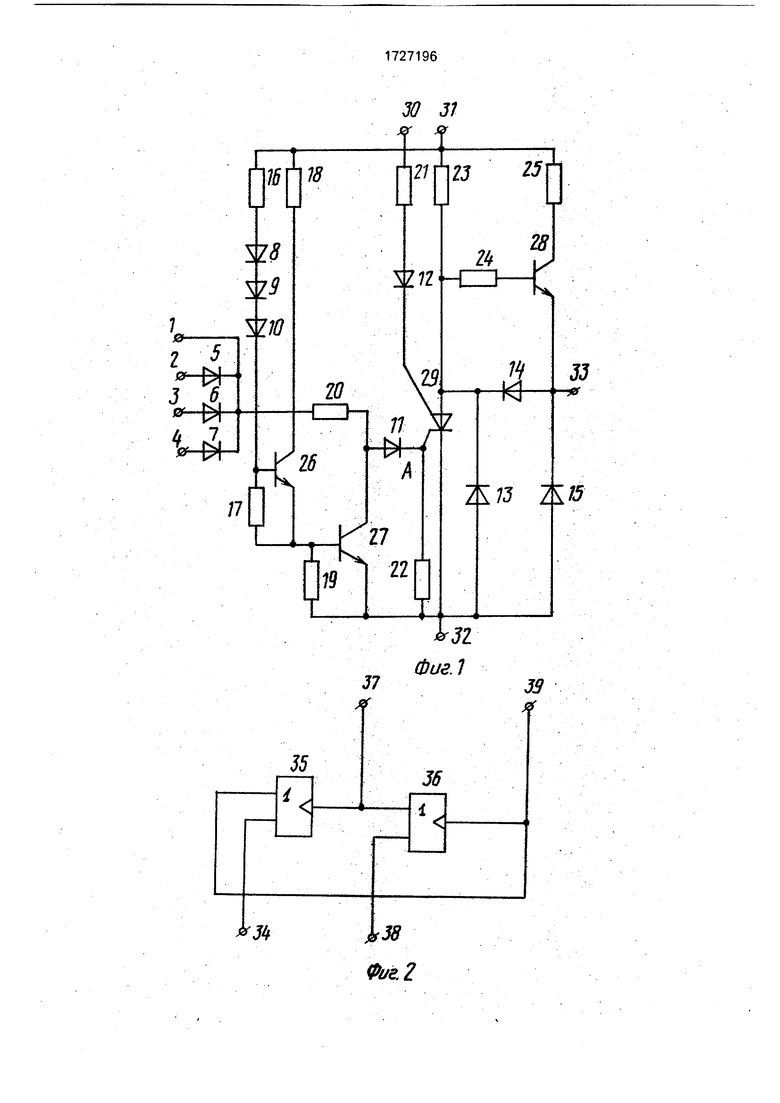

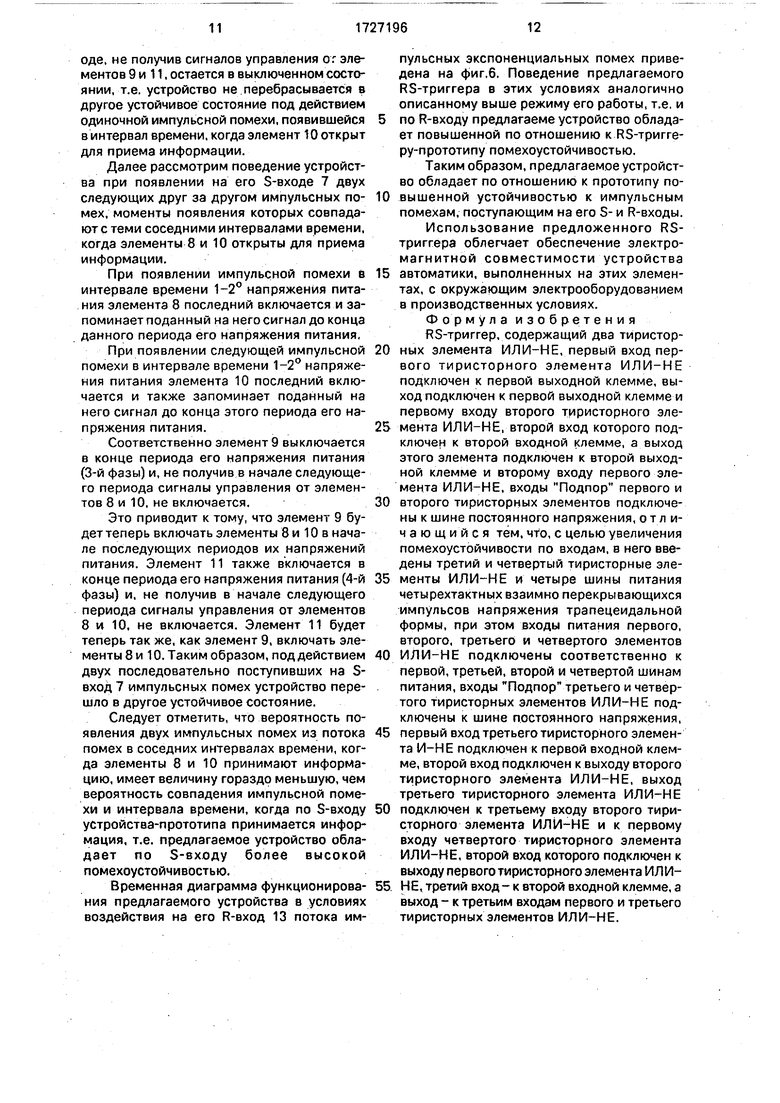

0 На фиг.2 приведена принципиальная схема триггера-прототипа.

На фиг.2 обозначены; 34 -1 S-вход триггера; 35 и 36 - тиристорные элементы ИЛИ- НЕ; 37 - инверсный выход триггера; 38 5 R-вход триггера; 39 - прямой выход триггера.

Такой RS-триггер образуется путем подключения выхода первого интегрального логического элемента 35, к одному из входов

0 второго интегрального логического элемента 36, выход которого подключен к одному из входов первого интегрального логического элемента. Элементы ИЛИ-НЕ питаются от импульсных трапецеидальных напряже5 ний, каждое длительностью, например, 294,5 эл.град.. сдвинутых друг относительно друга на 120 или 240 эл.град. При этом нулевые значения напряжения питания одного элемента перекрываются положительным

0 напряжением на другом элементе и наоборот. Например, элемент 35 питается импульсным трапецеидальным напряжением Ui, а элемент 36 - импульсным трапецеидальным напряжением DH, сдвинутым отно5 сительно напряжения Ui на 120 эл.град.

Помехоустойчивость RS-триггера no R. и S-входам определяется помехоустойчивостью образующих его тиристорных интегральных логических элементов ИЛИ-НЕ

0 серии К523..

RS-триггер также отличает значительно меньшая, чем у RS-триггера, реализованного на ИС серии К511, мощность потребления. . .

5 Однако данный RS-триггер имеет недостаток: его помехоустойчивость по R- и S- входам в случае прямого управления .этим триггером от датчиков в системе промышленной автоматики имеет недостаточную ве0 личину.

В предлагаемое устройство дополнительно введены третий и четвертый тиристорные элементы ИЛИ-НЕ и четыре шины питания четырехтактных взаимно перекры5 вающихся импульсов Напряжения трапецеидальной формы, при этом входы питания первого, второго, третьего и четвертого элементов ИЛИ-НЕ подключены соответственно к первой, третьей, второй и четвертой шинам питания, входы Подпор третьего и

четвертого тиристорных элементов ИЛИ- НЕ подключены к шине постоянного напряжения, первый вход третьего тиристорного элемента ИЛИ-НЕ подключен к первой входной клемме, второй вход подключен к выходу второго тиристорного элемента ИЛИ-НЕ, выход третьего тиристорного элемента ИЛИ-НЕ подключен к третьему входу второго тиристорного элемента ИЛИ-НЕ и первому входу четвертого тиристорного элемента ИЛИ-НЕ, второй вход которого подключен к выходу первого тиристорного элемента ИЛИ-НЕ, третий вход подключен к второй входной клемме, а выход подключен к третьим входам первого и третьего тиристорных элементов ИЛИ-НЕ.

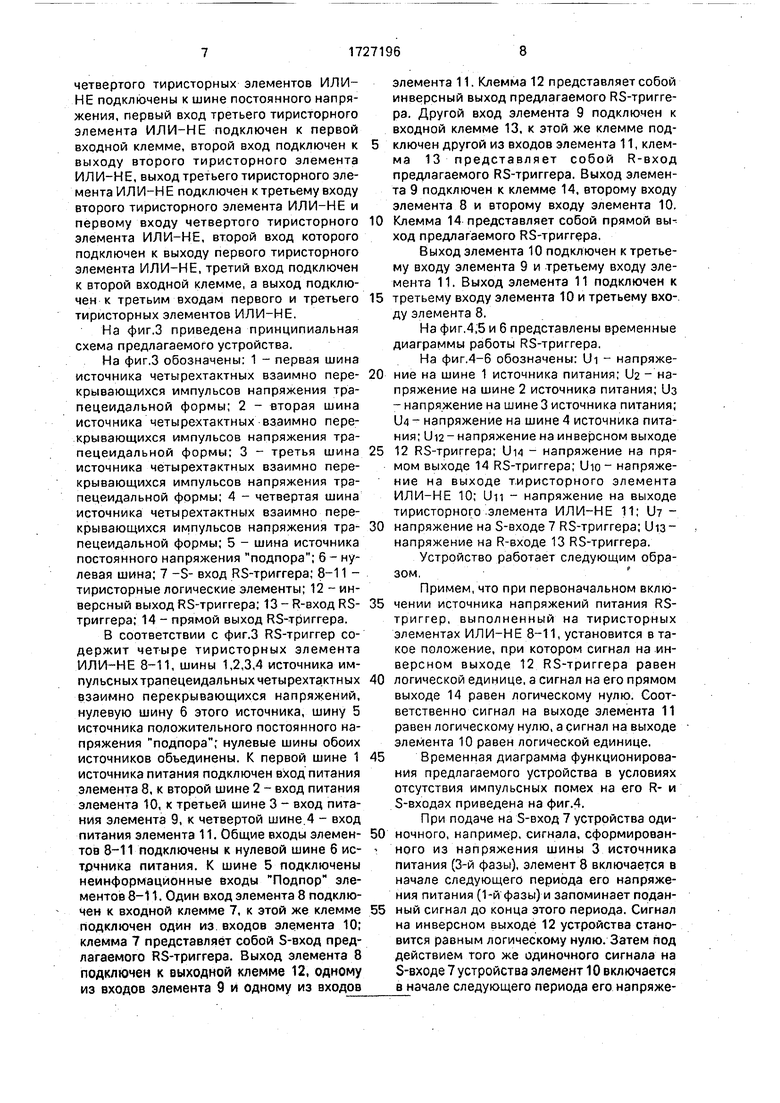

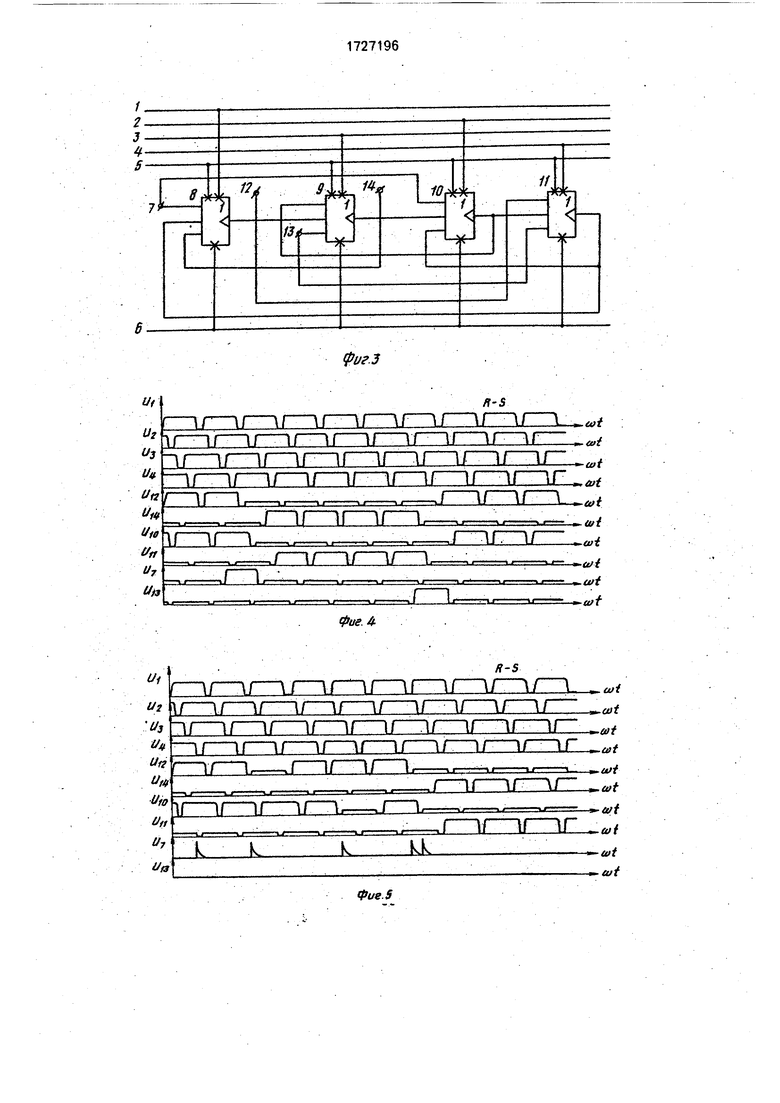

На фиг.З приведена принципиальная схема предлагаемого устройства.

На фиг.З обозначены: 1 - первая шина источника четырехтактных взаимно перекрывающихся импульсов напряжения трапецеидальной формы; 2 - вторая шина источника четырехтактных взаимно перекрывающихся импульсов напряжения трапецеидальной формы; 3 - третья шина источника четырехтактных взаимно перекрывающихся импульсов напряжения трапецеидальной формы; 4 - четвертая шина источника четырехтактных взаимно перекрывающихся импульсов напряжения трапецеидальной формы; 5 - шина источника постоянного напряжения подпора ; 6 - нулевая шина; 7 -S- вход RS-триггера; 8-11 - тиристорные логические элементы; 12 - инверсный выход RS-триггера; 13 - R-вход RS- триггера; 14 - прямой выход RS-триггера.

В соответствии с фиг.З RS-триггер содержит четыре тиристорных элемента ИЛИ-НЕ 8-11, шины 1,2,3,4 источника импульсных трапецеидальных четырехтактных взаимно перекрывающихся напряжений, нулевую шину 6 этого источника, шину 5 источника положительного постоянного напряжения подпора, нулевые шины обоих источников объединены. К первой шине 1 источника питания подключен вход питания элемента 8, к второй шине 2 - вход питания элемента 10, к третьей шине 3 - вход питания элемента 9, к четвертой шине.4 - вход питания элемента 11. Общие входы элементов 8-11 подключены к нулевой шине 6 источника питания. К шине 5 подключены неинформацйонные входы Подпор элементов 8-11. Один вход элемента 8 подключен к входной клемме 7, к этой же клемме подключен один из входов элемента 10; клемма 7 представляет собой S-вход предлагаемого RS-триггера. Выход элемента 8 подключен к выходной клемме 12, одному из входов элемента 9 и одному из входов

элемента 11. Клемма 12 представляет собой инверсный выход предлагаемого RS-триггера. Другой вход элемента 9 подключен к входной клемме 13, к этой же клемме подключей другой из входов элемента 11, клемма 13 представляет собой R-вход предлагаемого RS-триггера. Выход элемента 9 подключен к клемме 14, второму входу элемента 8 и второму входу элемента 10.

Клемма 14 представляет собой прямой выход предлагаемого RS-триггера,

Выход элемента 10 подключен к третьему входу элемента 9 и третьему входу элемента 11. Выход элемента 11 подключен к

третьему входу элемента 10 и третьему входу элемента 8.

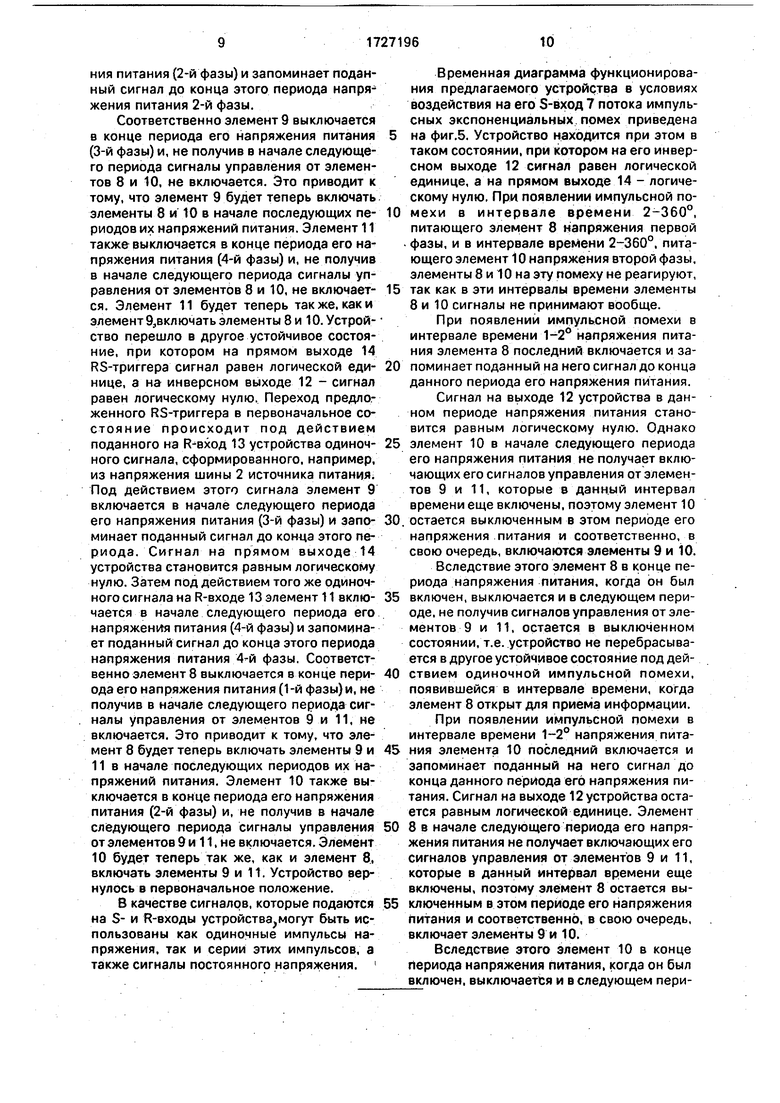

На фиг.4,5 и 6 представлены временные диаграммы работы RS-триггера.

На фиг.4-6 обозначены: Lh - напряжение на шине 1 источника питания; U2 - напряжение на шине 2 источника питания; 1)з -напряжение на шинеЗ источника питания; U4 - напряжение на шине 4 источника питания; U12 - напряжение на инверсном выходе

12 RS-триггера; Ui4 - напряжение на прямом выходе 14 RS-триггера; UIQ- напряжение на выходе тиристорного элемента ИЛИ-НЕ 10; DH - напряжение на выходе тиристорного элемента ИЛИ-НЕ 11; U напряжение на S-входе 7 RS-триггера; Ui3 напряжение на R-входе 13 RS-триггера.

Устройство работает следующим образом,

Примем, что при первоначальном включении источника напряжений питания RS- триггер, выполненный на тиристорных элементах ИЛИ-НЕ 8-11, установится в такое положение, при котором сигнал на инверсном выходе 12 RS-триггера равен

логической единице, а сигнал на его прямом выходе 14 равен логическому нулю. Соответственно сигнал на выходе элемента 11 равен логическому нулю, а сигнал на выходе элемента 10 равен логической единице,

Временная диаграмма функционирования предлагаемого устройства в условиях отсутствия импульсных помех на его R- и S-входах приведена на фиг.4.

При подаче на S-вход 7 устройства одиночного, например, сигнала, сформированного из напряжения шины 3 источника питания (3-й фазы), элемент 8 включается в начале следующего периода его напряжения питания (1-й фазы) и запоминает поданный сигнал до конца этого периода. Сигнал на инверсном выходе 12 устройства становится равным логическому нулю. Затем под действием того же одиночного сигнала на S-входе 7 устройства элемент 10 включается вначале следующего периода его напряжения питания (2-й фазы) и запоминает поданный сигнал до конца этого периода напряжения питания 2-й фазы.

Соответственно элемент 9 выключается в конце периода его напряжения питания (3-й фазы) и, не получив в начале следующего периода сигналы управления от элементов 8 и 10, не включается. Это приводит к тому, что элемент 9 будет теперь включать элементы 8 и 10 в начале последующих пе- риодов их напряжений питания. Элемент 11 также выключается в конце периода его напряжения питания (4-й фазы) и, не получив в начале следующего периода сигналы управления от элементов 8 и 10, не включает- ся. Элемент 11 будет теперь также, как и элемент 9.,включать элементы 8 и 10. Устрой- ство перешло в другое устойчивое состояние, при котором на прямом выходе 14 RS-триггера сигнал равен логической еди- нице, а на инверсном выходе 12 - сигнал равен логическому нулю. Переход предло.- женного RS-триггера в первоначальное состояние происходит под действием поданного на R-вход 13 устройства одиноч- ного сигнала, сформированного, например, из напряжения шины 2 источника питания; Под действием этого сигнала элемент 9 включается в начале следующего периода его напряжения питания (3-й фазы) и запо- минает поданный сигнал до конца этого периода. Сигнал на прямом выходе 14 устройства становится равным логическому нулю. Затем под действием того же одиночного сигнала на R-входе 13 элемент 11 вклю- чается в начале следующего периода его напряжения питания (4-й фазы) и запоминает поданный сигнал до конца этого периода напряжения питания 4-й фазы. Соответственно элемент 8 выключается в конце пери- ода его напряжения питания (1-й фазы) и, не получив в начале следующего периода сиг налы управления от элементов 9 и 11, не включается. Это приводит к тому, что элемент 8 будет теперь включать элементы 9 и 11 в начале последующих периодов их напряжений питания. Элемент 10 также выключается в конце периода его напряжения питания (2-й фазы) и, не получив в начале следующего периода сигналы управления от элементов 9 и 11, не включается. Элемент 10 будет теперь так же, как и элемент 8, включать элементы 9 и 11. Устройство вернулось в первоначальное положение.

В качестве сигналов, которые подаются на S- и R-входы устройства могут быть использованы как одиночные импульсы напряжения, так и серии этих импульсов, а также сигналы постоянного напряжения.

Временная диаграмма функционирования предлагаемого устройства в условиях воздействия на его S-вход 7 потока импульсных экспоненциальных помех приведена на фиг.5. Устройство находится при этом в таком состоянии, при котором на его инверсном выходе 12 сигнал равен логической единице, а на прямом выходе 14 - логическому нулю. При появлении импульсной помехи в интервале времени 2-360°, питающего элемент 8 напряжения первой фазы, и в интервале времени 2-360°. питающего элемент 10 напряжения второй фазы, элементы 8 и 10 на эту помеху не реагируют, так как в эти интервалы времени элементы 8 и 10 сигналы не принимают вообще.

При появлений импульсной помехи в интервале времени 1-2° напряжения питания элемента 8 последний включается и запоминает поданный на него сигнал до конца данного периода его напряжения питания.

Сигнал на выходе 12 устройства в данном периоде напряжения питания становится равным логическому нулю. Однако элемент 10 в начале следующего периода его напряжения питания не получает включающих его сигналов управления от элементов 9 и 11, которые в данный интервал времени еще включены, поэтому элемент 10 остается выключенным в этом периоде его напряжения питания и соответственно, в свою очередь, включаются элементы 9 и 10.

Вследствие этого элемент 8 в конце периода напряжения питания, когда он был включен, выключается и в следующем периоде, не получив сигналов управления от элементов 9 и 11, остается в выключенном состоянии, т.е. устройство не перебрасывается в другое устойчивое состояние под действием одиночной импульсной помехи, появившейся в интервале времени, когда элемент 8 открыт для приема информации.

При появлении импульсной помехи в интервале времени 1-2° напряжения питания элемента 10 последний включается и запоминает поданный на него сигнал до конца данного периода его напряжения питания. Сигнал на выходе 12 устройства остается равным логической единице. Элемент 8 в начале следующего периода его напряжения питания не получает включающих его сигналов управления от элементов 9 и 11, которые в данный интервал времени еще включены, поэтому элемент 8 остается выключенным в этом периоде его напряжения питания и соответственно, в свою очередь, включает элементы 9 и 10.

Вследствие этого элемент 10 в конце периода напряжения питания, когда он был включен, выключается и в следующем периоде, не получив сигналов управления ог элементов 9 и 11, остается в выключенном состоянии, т.е. устройство не перебрасывается в другое устойчивое состояние под действием одиночной импульсной помехи, появившейся в интервал времени, когда элемент 10 открыт для приема информации.

Далее рассмотрим поведение устройства при появлении на его S-входе 7 двух следующих друг за другом импульсных помех, моменты появления которых совпадают с теми соседними интервалами времени, когда элементы 8 и 10 открыты для приема информации.

При появлении импульсной помехи в интервале времени 1-2° напряжения питания элемента 8 последний включается и запоминает поданный на него сигнал до конца данного периода его напряжения питания.

При появлении следующей импульсной помехи в интервале времени 1-2° напряжения питания элемента 10 последний включается и также запоминает поданный на него сигнал до конца этого периода его напряжения питания.

Соответственно элемент 9 выключается в конце периода его напряжения питания (3-й фазы) и, не получив в начале следующего периода сигналы управления от элементов 8 и 10, не включается.

Это приводит к тому, что элемент 9 будет теперь включать элементы 8 и 10 в начале последующих периодов их напряжений питания. Элемент 11 также включается в конце периода его напряжения питания (4-й фазы) и, не получив в начале следующего периода сигналы управления от элементов 8 и 10, не включается. Элемент 11 будет теперь так же, как элемент 9, включать элементы 8 и 10. Таким образом, под действием двух последовательно поступивших на S- вход 7 импульсных помех устройство перешло в другое устойчивое состояние.

Следует отметить, что вероятность появления двух импульсных помех из потока помех в соседних интервалах времени, когда элементы 8 и 10 принимают информацию, имеет величину гораздо меньшую, чем вероятность совпадения импульсной помехи и интервала времени, когда по S-входу устройства-прототипа принимается информация, т.е. предлагаемое устройство обладает по S-входу более высокой помехоустойчивостью.

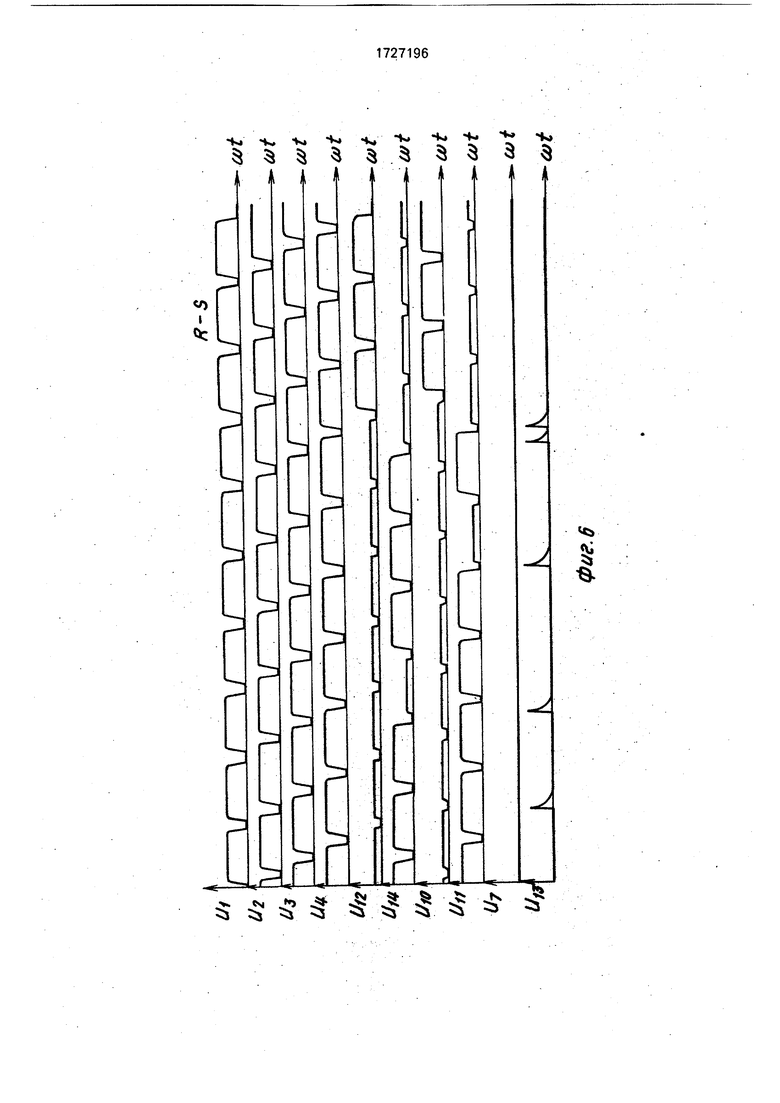

Временная диаграмма функционирования предлагаемого устройства в условиях воздействия на его R-вход 13 потока импульсных экспоненциальных помех приведена на фиг.6. Поведение предлагаемого RS-триггера в этих условиях аналогично описанному выше режиму его работы, т.е. и

по R-входу предлагаемо устройство обладает повышенной по отношению к RS-тригге- ру-прототипу помехоустойчивостью.

Таким образом, предлагаемое устройство обладает по отношению к прототипу повышенной устойчивостью к импульсным помехам, поступающим на его S- и R-входы. Использование предложенного RS- триггера облегчает обеспечение электромагнитной совместимости устройства

автоматики, выполненных на этих элементах, с окружающим электрооборудованием в производственных условиях.

Формула изобретения RS-триггер, содержащий два тиристорных элемента ИЛИ-НЕ, первый вход первого тиристорного элемента ИЛИ-НЕ подключен к первой выходной клемме, выход подключен к первой выходной клемме и первому входу второго тиристорного элемента ИЛИ-НЕ, второй вход которого подключен к второй входной клемме, а выход этого элемента подключен к второй выходной клемме и второму входу первого элемента ИЛИ-НЕ, входы Подпор первого и

второго тиристорных элементов подключены к шине постоянного напряжения, отличающийся тем, что, с целью увеличения помехоустойчивости по входам, в него введены третий и четвертый тиристорные элементы ИЛИ-НЕ и четыре шины питания четырехтактных взаимно перекрывающихся импульсов напряжения трапецеидальной формы, при этом входы питания первого, второго, третьего и четвертого элементов

ИЛИ-НЕ подключены соответственно к первой, третьей, второй и четвертой шинам питания, входы Подпор третьего и четвертого тиристорных элементов ИЛИ-НЕ подключены к шине постоянного напряжения,

первый вход третьего тиристорного элемента И-НЕ подключена первой входной клемме, второй вход подключен к выходу второго тиристорного элемента ИЛИ-НЕ, выход третьего тиристорного элемента ИЛИ-НЕ

подключен к третьему входу второго тиристорного элемента ИЛИ-НЕ и к первому входу четвертого тиристорного элемента ИЛИ-НЕ, второй вход которого подключен к выходу первого тиристорного элемента ИЛ ИНЕ, третий вход - к второй входной клемме, а выход - к третьим входам первого и третьего тиристорных элементов ИЛИ-НЕ.

зд зг

| название | год | авторы | номер документа |

|---|---|---|---|

| RS-триггер | 1989 |

|

SU1725364A1 |

| Устройство для защиты выпрямителя,работающего на импульсную нагрузку | 1986 |

|

SU1365237A1 |

| Устройство для управления тиристорным инвертором | 1985 |

|

SU1275709A1 |

| Устройство для управления вентильным преобразователем | 1983 |

|

SU1094129A1 |

| УСТРОЙСТВО ИМПУЛЬСНО-ФАЗОВОГО УПРАВЛЕНИЯ | 1999 |

|

RU2160957C2 |

| Стабилизированный импульсный преобразователь переменного напряжения | 1982 |

|

SU1026260A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МИНИМАЛЬНЫХ УГЛОВ УПРАВЛЕНИЯ | 2019 |

|

RU2709026C1 |

| Сетевой выпрямитель | 1990 |

|

SU1757058A1 |

| Устройство управления тиристорным коммутатором переменного тока | 1977 |

|

SU733106A1 |

| Способ генерирования импульсов магнитно-тиристорным генератором и магнитно-тиристорный генератор | 1984 |

|

SU1356217A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения -увеличение помехоустойчивости по входам. RS-триггер содержит четыре тиристорных элемента ИЛИ-НЕ и четыре шины питания четырехтактных взаимно перекрывающихся импульсов напряжения трапецеидальной формы. Введение третьего и четвертого тиристорных элементов ИЛИ-НЕ и четырех шин питания четырехтактных взаимно перекрывающихся импульсов напряжения трапецеидальной формы позволяет увеличить помехоустойчивость по входам RS-триггера, так как вероятность появления двух импульсных помех в соседних интервалах времени, когда тиристорные элементы ИЛИ-НЕ принимают информацию, имеет величину гораздо меньшую, чем вероятность совпадения импульсной помехи и интервала времени, когда по входу устройства принимается информация. 6 ил. со С

Й

18

J5

#М

12/ГШ 25

37 #

Фиг. 1

39 0

36

k38 Фиг. 2

5-V

J I L

CffJ

n

uff

Otfl

n n

Л

Јn n

Л

96li2il

W Ч -V V Ч. Ч. Ч- -К

ss зз5 53 з 5

| Приборы системы управления, 1971, № 4,с.36-38 | |||

| Микросхемы интегральные полупроводниковые | |||

| Сер | |||

| Машина для производства земляных работ | 1919 |

|

SU523A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-04-15—Публикация

1990-01-08—Подача