этих диодов объединены между собой и подключены к входам питания транзисторного элемента 10 задержки сигнала, транзисторных логических элементов НЕ 7 и 8. Общие входы элементов 7, 8 и 10 подклю- чены к нулевой шине А источников питания. Вход питания диодно-транзисторного логического элемента И 9 подключен к аноду диода 11. Первый вход двухвходового диодно-транзисторного логического элемента И

9подключен к выходу 25 первого тиристорного логического элемента ИЛИ-НЕ 5 (инверсному выходу устройства), выход 27 второго тиристорного логического элемента ИЛИ-НЕ 6 соединен с входом первоготран- зисторного логического элемента НЕ 7, выход которого подключен к входу второго транзисторного логического элемента НЕ 8. Выход этого элемента 8 соединен с вторым входом диодно-транзисторного логического элемента И 9, выход которого через транзисторный элемент 10 задержки сигнала соединен с первыми выводами резисторов 17 и

18. Вторые выводы этих резисторов 17 и 18 соединены соответственно с анодами дио- дов 13 и 14, катоды которых подключены соответственно к анодам диодов 12 и 15. Катод диода 12 соединен с дополнительным установочным входом 19 тиристорного логического элемента ИЛИ-НЕ 5, катод диода 15 соединен с дополнительным установочным входом 21 тиристорного логического элемента ИЛИ-НЕ 6.

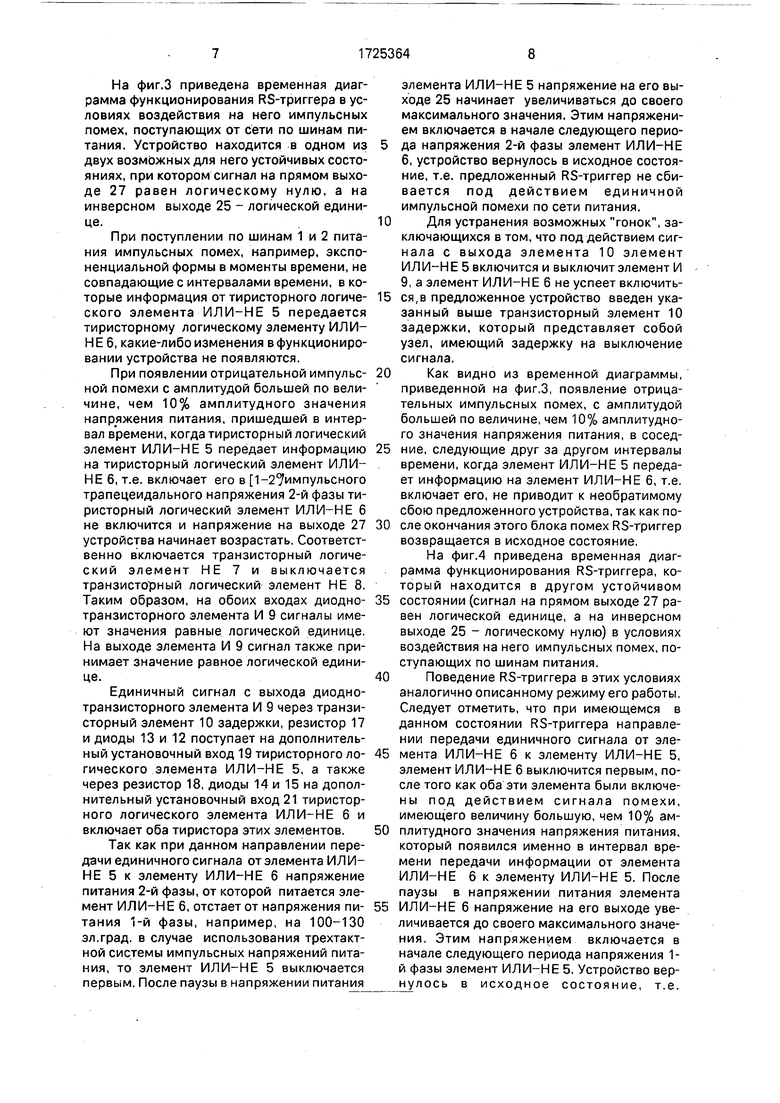

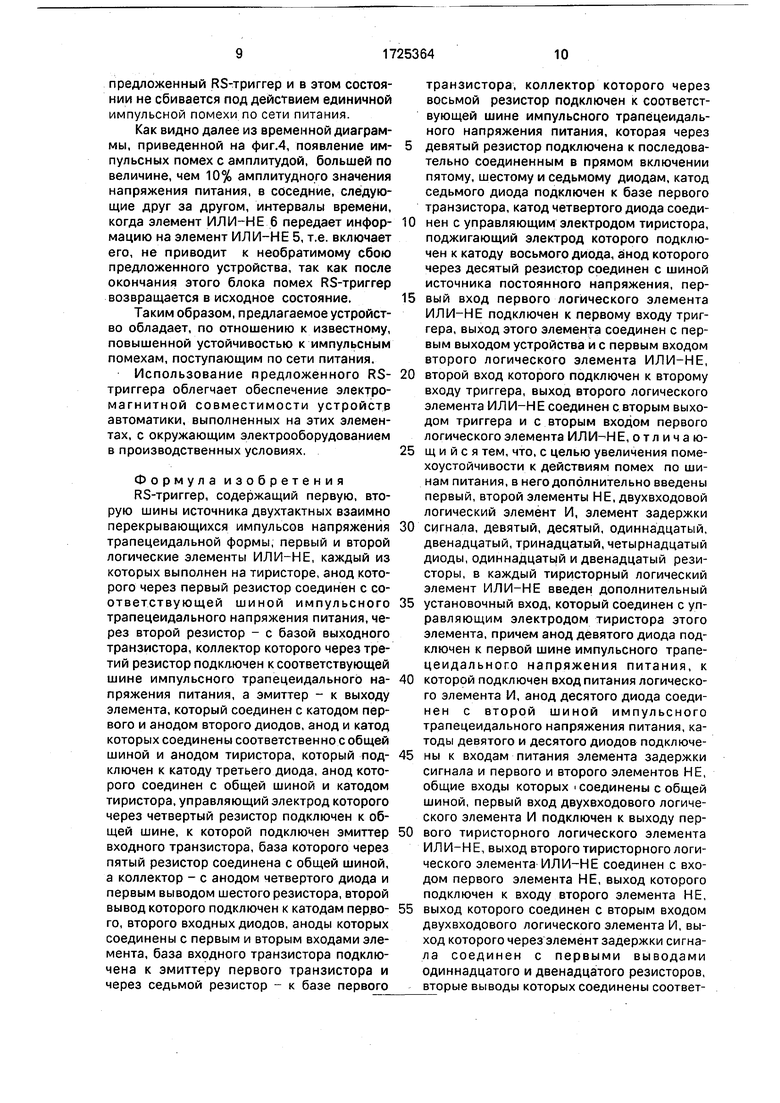

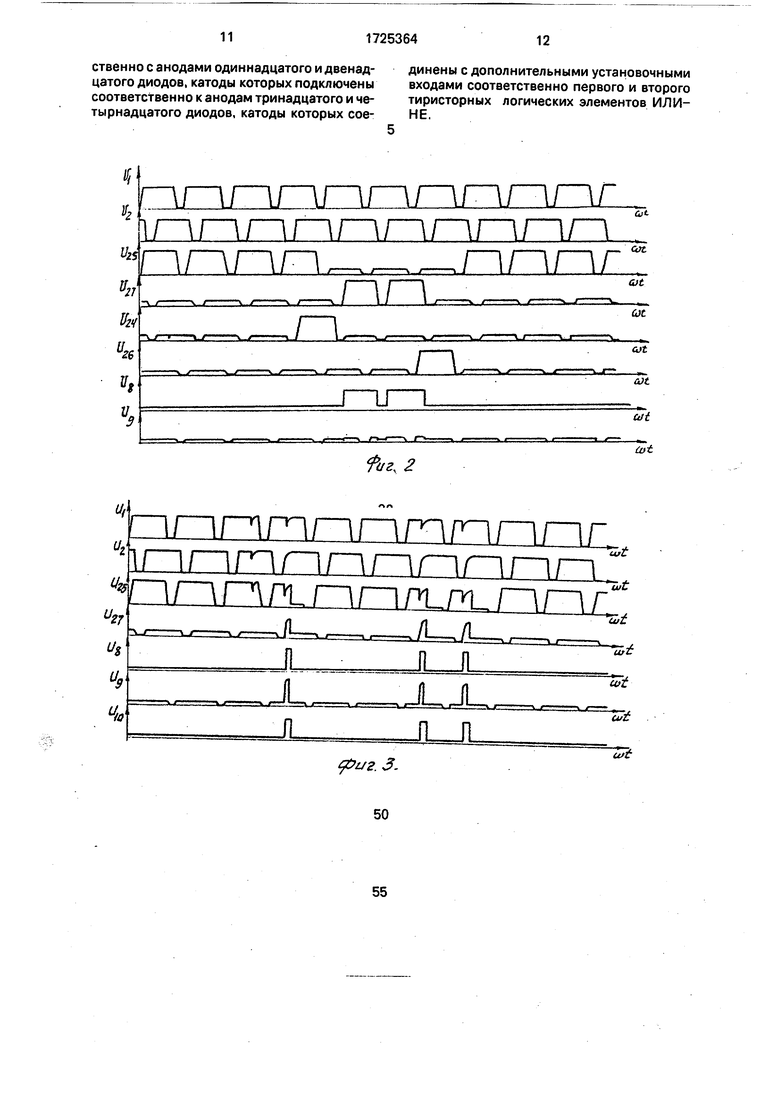

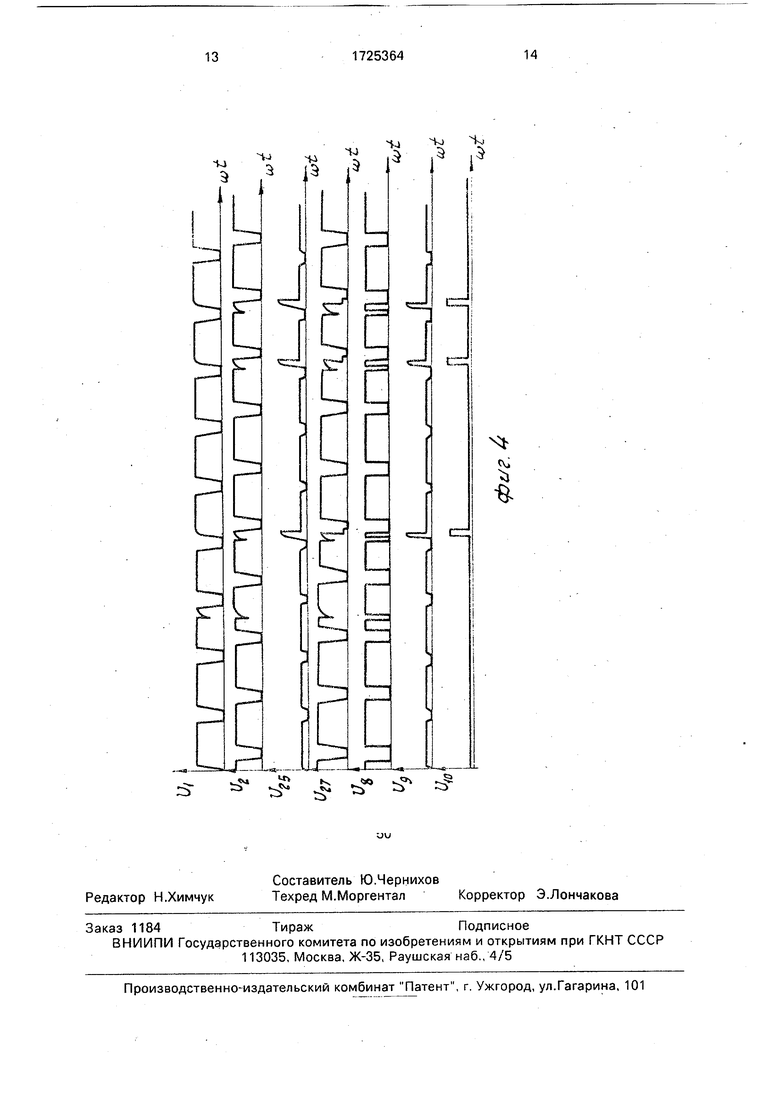

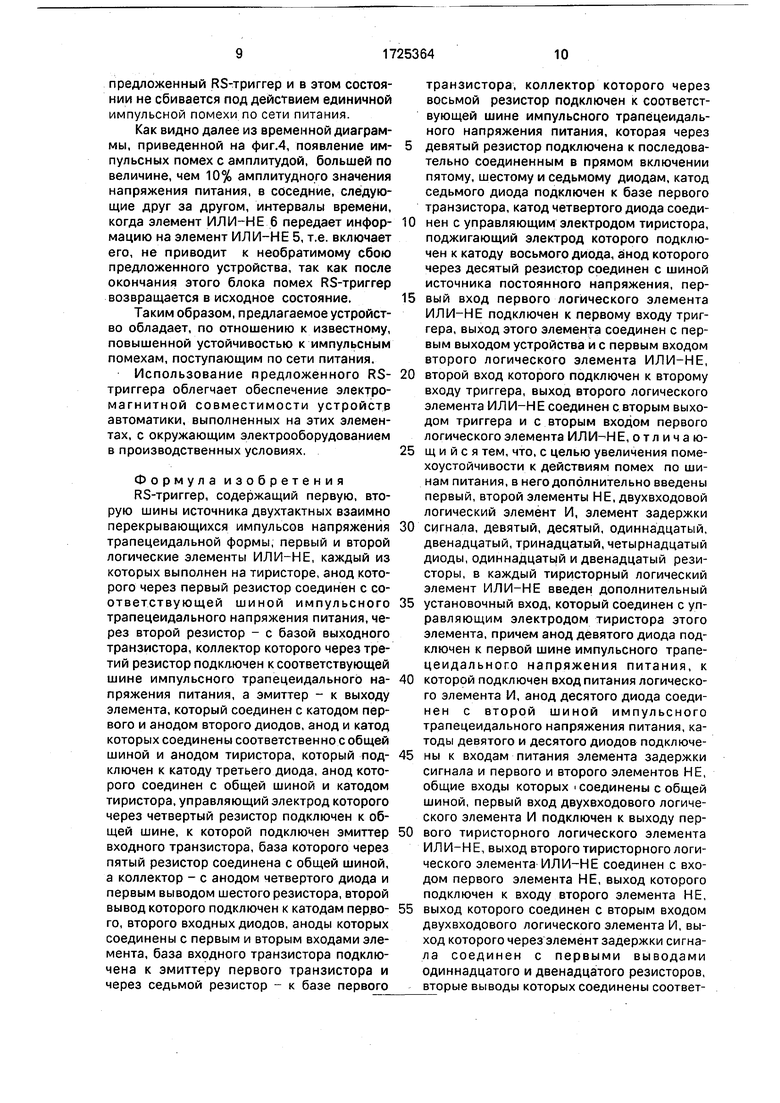

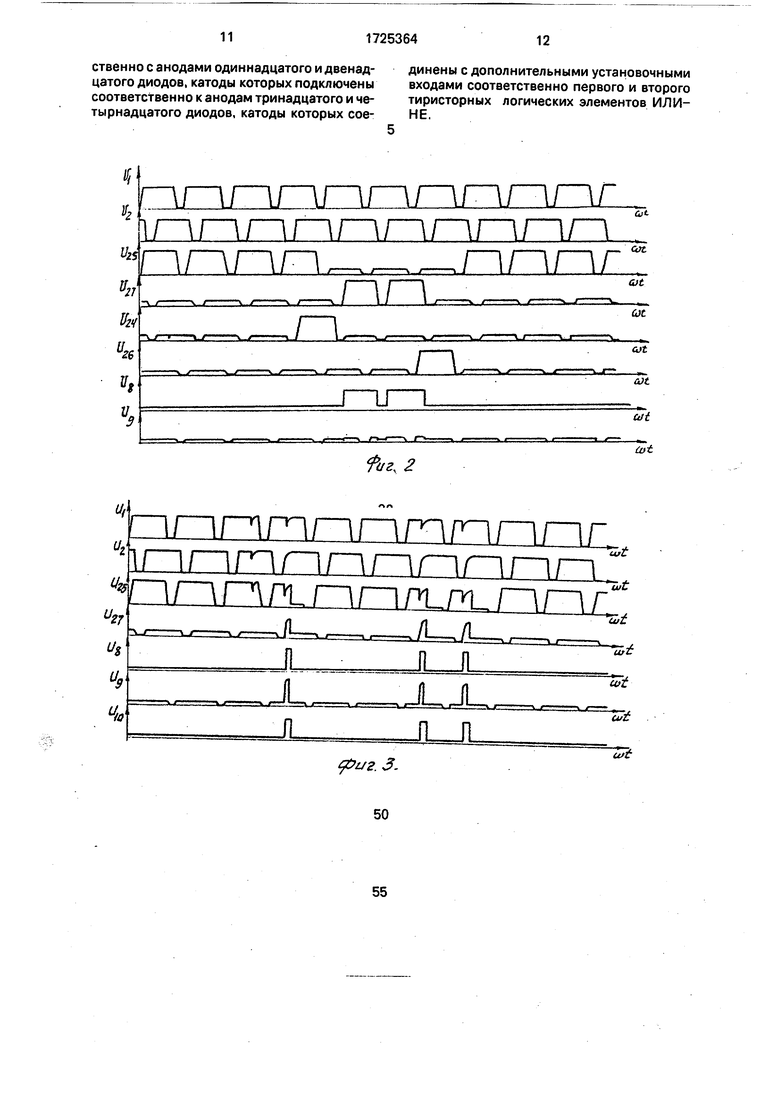

На временных диаграммах работы RS- триггера обозначено Ui - напряжение на шине 1 источника питания; Da-напряжение на шине 2 источника питания; U25 - напряжение на инверсном выходе 25 RS-триггера; U27 - напряжение на прямом выходе 27 RS- триггера; U24 - напряжение на S-входе 24 RS-триггера; Uae - напряжение на R-входе 26 RS-триггера; Us - напряжение на выходе транзисторного логического элемента НЕ 8; Ug - напряжение на выходе диодно-транзисторного логического элемента И 9; Ую - на- пряжение на выходе транзисторного элемента

10задержки сигнала (только на фиг.З, 4).

Устройство работает следующим образом.

Примем, что при первоначальном вклю- чении источника напряжений питания RS- триггер, выполненный на тиристорных логических элементах ИЛИ-НЕ 5 и 6, установится в такое положение, при котором сигнал на инверсном выходе 25 RS-триггера равен логической единице, а сигнал на его прямом выходе 27 равен логическому нулю.

Временная диаграмма функционирования предлагаемого устройства в условиях отсутствия импульсных помех по шинам питания приведена на фиг.2. При подаче на S-вход 24 устройства одиночного сигнала, сформированного, например, из напряжения шины 2 источника питания (2-й фазы), тиристорный логический элемент ИЛИ-НЕ

5включается в начале следующего периода его напряжения питания (1-й фазы) и запоминает поданный сигнал до конца этого периода. Соответственно, тиристорный логический элемент ИЛИ-НЕ 6 выключается в конце периода его напряжения питания (2-й фазы) и не получив в начале следующего периода сигнал управления от тиристорного логического элемента ИЛИ-НЕ 5 не включается. Это приводит к тому, что тиристорный логический элемент ИЛИ-НЕ

6будет теперь включать тиристорный логический элемент ИЛИ-НЕ 5 в начале последующих периодов его напряжения питания, т.е. устройство переходит в другое устойчивое состояние, при котором на прямом выходе 27 RS-триггера сигнал равен логической единице, а на инверсном выходе 25 сигнал равен логическому нулю.

Переход RS-триггера в первоначальное состояние происходит под действием поданного на R-вход 26 устройства одиночного сигнала, сформированного из напряжения шины 1 источника питания, и протекает аналогично описанному переходу. В качестве сигналов, которые подаются на S- и R- входы устройства могут быть использованы как одиночные импульсы напряжения, так и серии этих импульсов, а также сигналы постоянного напряжения.

На фиг.2 показано, что в рассматриваемом режиме работы устройства (отсутствие помех по шинам питания) его функционирование не нарушается от использования в составе RS-триггера элементов 7-10, так как в данном режиме его работы сигнал на одном из входов диодно-транзисторного элемента И 9 всегда равен логическому нулю и, соответственно, сигнал на выходе элемента И 9 также равен логическому нулю и, следовательно, воздействие на дополнительные установочные входы 19 и 21 логических элементов ИЛИ-НЕ 5 и 6 через транзисторный элемент 10 задержки не поступает.

Повторитель, выполненный на двух транзисторных логических элементах НЕТ и 8, предназначен для исключения возможности залипания тиристора логического элемента ИЛИ-НЕ 6 в конце периода его напряжения питания в случае, когда элемент ИЛИ-НЕ 6 находится во включенном состоянии и RS-триггер под действием сигнала на S-входе 24 должен перейти в другое устойчивое состояние.

На фиг.З приведена временная диаграмма функционирования RS-триггера в условиях воздействия на него импульсных помех, поступающих от сети по шинам питания, Устройство находится в одном из двух возможных для него устойчивых состояниях, при котором сигнал на прямом выходе 27 равен логическому нулю, а на инверсном выходе 25 - логической единице.

При поступлении по шинам 1 и 2 питания импульсных помех, например, экспоненциальной формы в моменты времени, не совпадающие с интервалами времени, в которые информация от тиристорного логического элемента ИЛИ-НЕ 5 передается тиристорному логическому элементу ИЛИ- НЕ 6, какие-либо изменения в функционировании устройства не появляются.

При появлении отрицательной импульсной помехи с амплитудой большей по величине, чем 10% амплитудного значения напряжения питания, пришедшей в интервал времени, когда тиристорный логический элемент ИЛИ-НЕ 5 передает информацию на тиристорный логический элемент ИЛИ- НЕ 6, т.е. включает его в 1-2 импульсного трапецеидального напряжения 2-й фазы тиристорный логический элемент ИЛИ-НЕ 6 не включится и напряжение на выходе 27 устройства начинает возрастать. Соответственно включается транзисторный логический элемент НЕ 7 и выключается транзисторный логический элемент НЕ 8. Таким образом, на обоих входах диодно- транзисторного элемента И 9 сигналы имеют значения равные логической единице, На выходе элемента И 9 сигнал также принимает значение равное логической единице.

Единичный сигнал с выхода диодно- транзисторного элемента И 9 через транзисторный элемент 10 задержки, резистор 17 и диоды 13 и 12 поступает на дополнительный установочный вход 19 тиристорного логического элемента ИЛИ-НЕ 5, а также через резистор 18, диоды 14 и 15 на дополнительный установочный вход 21 тиристорного логического элемента ИЛИ-НЕ 6 и включает оба тиристора этих элементов.

Так как при данном направлении передачи единичного сигнала от элемента ИЛИ- НЕ 5 к элементу ИЛИ-НЕ 6 напряжение питания 2-й фазы, от которой питается элемент ИЛИ-НЕ 6, отстает от напряжения питания 1-й фазы, например, на 100-130 эл.град. в случае использования трехтактной системы импульсных напряжений питания, то элемент ИЛИ-НЕ 5 выключается первым. После паузы в напряжении питания

элемента ИЛИ-НЕ 5 напряжение на его выходе 25 начинает увеличиваться до своего максимального значения. Этим напряжением включается в начале следующего периода напряжения 2-й фазы элемент ИЛИ-НЕ 6, устройство вернулось в исходное состояние, т.е. предложенный RS-триггер не сбивается под действием единичной импульсной помехи по сети питания.

0 Для устранения возможных гонок, заключающихся в том, что под действием сигнала с выхода элемента 10 элемент ИЛИ-НЕ 5 включится и выключит элемент И 9, а элемент ИЛИ-НЕ 6 не успеет включить5 ся,в предложенное устройство введен указанный выше транзисторный элемент 10 задержки, который представляет собой узел, имеющий задержку на выключение сигнала.

0 Как видно из временной диаграммы, приведенной на фиг.З, появление отрицательных импульсных помех, с амплитудой большей по величине, чем 10% амплитудного значения напряжения питания, в сосед5 ние, следующие друг за другом интервалы времени, когда элемент ИЛИ-НЕ 5 передает информацию на элемент ИЛИ-НЕ 6, т.е. включает его, не приводит к необратимому сбою предложенного устройства, так как по0 еле окончания этого блока помех RS-триггер возвращается в исходное состояние.

На фиг.4 приведена временная диаграмма функционирования RS-триггера, который находится в другом устойчивом

5 состоянии (сигнал на прямом выходе 27 равен логической единице, а на инверсном выходе 25 - логическому нулю) в условиях воздействия на него импульсных помех, поступающих по шинам питания.

0 Поведение RS-триггера в этих условиях аналогично описанному режиму его работы. Следует отметить, что при имеющемся в данном состоянии RS-триггера направлении передачи единичного сигнала от эле5 мента ИЛИ-НЕ 6 к элементу ИЛИ-НЕ 5, элемент ИЛИ-НЕ 6 выключится первым, после того как оба эти элемента были включены под действием сигнала помехи, имеющего величину большую, чем 10% ам0 плитудного значения напряжения питания, который появился именно в интервал времени передачи информации от элемента ИЛИ-НЕ 6 к элементу ИЛИ-НЕ 5. После паузы в напряжении питания элемента

5 ИЛИ-НЕ 6 напряжение на его выходе увеличивается до своего максимального значения. Этим напряжением включается в начале следующего периода напряжения 1- й фазы элемент ИЛИ-НЕ 5, Устройство вернулось в исходное состояние, т.е.

предложенный RS-триггер и в этом состоянии не сбивается под действием единичной импульсной помехи по сети питания.

Как видно далее из временной диаграммы, приведенной на фиг.4, появление импульсных помех с амплитудой, большей по величине, чем 10% амплитудного значения напряжения питания, в соседние, следующие друг за другом, интервалы времени, когда элемент ИЛИ-НЕ 6 передает информацию на элемент ИЛИ-НЕ 5, т.е. включает его, не приводит к необратимому сбою предложенного устройства, так как после окончания этого блока помех RS-триггер возвращается в исходное состояние.

Таким образом, предлагаемое устройство обладает, по отношению к известному, повышенной устойчивостью к импульсным помехам, поступающим по сети питания.

Использование предложенного RS- триггера облегчает обеспечение электромагнитной совместимости устройств автоматики, выполненных на этих элементах, с окружающим электрооборудованием в производственных условиях.

Формула изобретения RS-триггер, содержащий первую, вторую шины источника двухтактных взаимно перекрывающихся импульсов напряжения трапецеидальной формы, первый и второй логические элементы ИЛИ-НЕ, каждый из которых выполнен на тиристоре, анод которого через первый резистор соединен с соответствующей шиной импульсного трапецеидального напряжения питания, через второй резистор - с базой выходного транзистора, коллектор которого через третий резистор подключен к соответствующей шине импульсного трапецеидального напряжения питания, а эмиттер - к выходу элемента, который соединен с катодом первого и анодом второго диодов, анод и катод которых соединены соответственно с общей шиной и анодом тиристора, который подключен к катоду третьего диода, анод которого соединен с общей шиной и катодом тиристора, управляющий электрод которого через четвертый резистор подключен к общей шине, к которой подключен эмиттер входного транзистора, база которого через пятый резистор соединена с общей шиной, а коллектор - с анодом четвертого диода и первым выводом шестого резистора, второй вывод которого подключен к катодам первого, второго входных диодов, аноды которых соединены с первым и вторым входами элемента, база входного транзистора подключена к эмиттеру первого транзистора и через седьмой резистор - к базе первого

транзистора, коллектор которого через восьмой резистор подключен к соответствующей шине импульсного трапецеидального напряжения питания, которая через

девятый резистор подключена к последовательно соединенным в прямом включении пятому, шестому и седьмому диодам, катод седьмого диода подключен к базе первого транзистора, катод четвертого диода соеди0 нен с управляющим электродом тиристора, поджигающий электрод которого подключен к катоду восьмого диода, анод которого через десятый резистор соединен с шиной источника постоянного напряжения, пер5 вый вход первого логического элемента ИЛИ-НЕ подключен к первому входу триггера, выход этого элемента соединен с первым выходом устройства и с первым входом второго логического элемента ИЛИ-НЕ,

0 второй вход которого подключен к второму входу триггера, выход второго логического элемента ИЛИ-НЕ соединен с вторым выходом триггера и с вторым входом первого логического элемента ИЛИ-НЕ, отличаю5 щ и и с я тем, что, с целью увеличения помехоустойчивости к действиям помех по шинам питания, в него дополнительно введены первый, второй элементы НЕ, двухвходовой логический элемент И, элемент задержки

0 сигнала, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый,четырнадцатый диоды, одиннадцатый и двенадцатый резисторы, в каждый тиристорный логический элемент ИЛИ-НЕ введен дополнительный

5 установочный вход, который соединен с управляющим электродом тиристора этого элемента, причем анод девятого диода подключен к первой шине импульсного трапецеидального напряжения питания, к

0 которой подключен вход питания логического элемента И, анод десятого диода соединен с второй шиной импульсного трапецеидального напряжения питания, катоды девятого и десятого диодов подключе5 ны к входам питания элемента задержки сигнала и первого и второго элементов НЕ, общие входы которых соединены с общей шиной, первый вход двухвходового логического элемента И подключен к выходу пер0 вого тиристорного логического элемента ИЛИ-НЕ, выход второго тиристорного логического элемента ИЛИ-НЕ соединен с входом первого элемента НЕ, выход которого подключен к входу второго элемента НЕ,

5 выход которого соединен с вторым входом двухвходового логического элемента И, выход которого через элемент задержки сигна- ла соединен с первыми выводами одиннадцатого и двенадцатого резисторов, вторые выводы которых соединены соответственно с анодами одиннадцатого и двенадцатого диодов, катоды которых подключены соответственно к анодам тринадцатого и четырнадцатого диодов, катоды которых соединены с дополнительными установочными входами соответственно первого и второго тиристорных логических элементов ИЛИ- НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ключ переменного тока | 1990 |

|

SU1725380A1 |

| Многоканальное устройство согласования коммутационной цепи переменного тока с интегральной микросхемой | 1984 |

|

SU1307552A1 |

| Устройство для защиты выпрямителя,работающего на импульсную нагрузку | 1986 |

|

SU1365237A1 |

| УСТРОЙСТВО ИМПУЛЬСНО-ФАЗОВОГО УПРАВЛЕНИЯ | 1999 |

|

RU2160957C2 |

| @ -Канальный формирователь импульсов управления тиристорами | 1988 |

|

SU1598011A1 |

| Динамический триггер А.С.Гребнева | 1982 |

|

SU1058074A1 |

| RS-триггер | 1990 |

|

SU1727196A1 |

| Трехфазный тиристорный ключ | 1979 |

|

SU851777A1 |

| Устройство для задержки импульсов | 1980 |

|

SU917323A1 |

| Устройство для дифференциальной защиты | 1988 |

|

SU1610533A2 |

Авторы

Даты

1992-04-07—Публикация

1989-11-29—Подача