-ч со

ON

рой вход 15 для оперативного сброса наработанного текущего значения выдержки времени в ее исходное нулевое значение, исполнительный блок 12 имеет статический запрещающий второй вход 16 установки в состояние сигнализации Неисправность, взаимодействующий с первым входом 13 по схеме ЗАПРЕТ. Имеется также выпрямительный блок 17, формирующий на своих выходных выводах 18, 19 постоянное напряжение для питания элементов устройства при наличии на его входных выводах 1, 2, 3 по меньшей мере двух из трех синусоидальных напряжений контролируемой сети. В нормальном режиме работы сети исполнительный блок 12 находится в состоянии сигнализации Исправность, при этом блок 10 выдержки времени периодически сбрасывается в исходное нулевое состояние сигналом с выхода элемента И 9. В нормальном режиме работы сети исполнительный блок 12 сигналом, поступающим на вход 16с блока 10 после отработки этим блоком заданной выдержки времени, переводится в состояние сигнализации Неисправность. 1 з.п. ф-лы, 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты трехфазных сетей от неправильного чередования фаз | 1978 |

|

SU744830A1 |

| Устройство для контроля чередования фаз трехфазной сети | 1980 |

|

SU936173A1 |

| Устройство для защиты электроустановки от неправильного чередования фаз | 1983 |

|

SU1108548A1 |

| Светосигнальное предохранительное устройство | 1988 |

|

SU1621119A1 |

| Устройство для контроля чередования и обрыва фаз трехфазной сети | 1984 |

|

SU1181042A1 |

| УСТРОЙСТВО ЗАЩИТЫ ГРУППЫ ТРЕХФАЗНЫХ ЭЛЕКТРОДВИГАТЕЛЕЙ ОТ ОБРЫВА ФАЗЫ ПИТАНИЯ | 1998 |

|

RU2136037C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПРАВИЛЬНОСТИ ЧЕРЕДОВАНИЯ И ОБРЫВА ФАЗ И УРОВНЯ НАПРЯЖЕНИЯ В ТРЕХФАЗНЫХ СЕТЯХ | 1992 |

|

RU2033621C1 |

| Устройство для контроля чередования фаз трехфазной сети | 1980 |

|

SU936166A1 |

| Устройство для непрерывного контроля наличия и правильности чередования фаз трехфазного напряжения | 1978 |

|

SU744828A1 |

| Устройство для непрерывного контроля наличия и правильности чередования фаз сети трехфазного напряжения | 1982 |

|

SU1112468A1 |

Использование: для защиты электроустановок от изменения чередования и обрыва фаз. Сущность изобретения: устройство содержит входные выводы 1, 2, 3, входные преобразователи 4, 5, 6, D-триг- геры 7, 8, элементы И 9, блок 10 выдержки времени со статическим первым входом 11 включения отработки заданной временной задержки, исполнительный блок 12 со статическим разрешающим первым входом 13 установки в состояние сигнализации Исправность. Вход D-триггера 7 снабжен выводом для подключения к шине 14 потенциала лог.1. Блок 10 выдержки времени имеет втоСП

Изобретение относится к электротехнике и предназначено для использования в системах релейной защиты и электроавтоматики электродвигателей и электроустановок.

Известно устройство для контроля чередования фаз трехфазной сети, содержащее пороговый блок, состоящий из подключенных к каждой фазе пороговых элементов, логический блок, включающий в себя два триггера с разделенными входами и элемент И, выходной усилитель и исполнительный орган.

Однако известное устройство не характеризуется достаточной функциональной надежностью, так как возможны его ложные срабатывания при изменении формы напряжения в одной или двух фазах вследствие наличия зависимости ширины формируемых пороговым блоком импульсов отампли- туды и формы контролируемых напряжений. Кроме того, формируемая в номинальном режиме сети последовательность импульсов на выходе логического блока при возникновении аварийной ситуа- ции превращается в постоянный сигнал, уровень которого не однозначен (логический О или логическая 1), так как зависит от момента возникновения аварии.

Известно также устройство для контро- ля чередования фаз трехфазной сети.

Основными недостатками устройства являются та же неоднозначность сигнала на входе исполнительного устройства и недостаточная помехоустойчивость.

Наиболее близким к предлагаемому является устройство для контроля чередования фаз трехфазной сети, содержащее подключенные к фазам формирователи импульсов, одновибратор, синхронные D-триг-

геры, логический элемент И и исполнительный элемент.

Недостатком данного устройства является та же неоднозначность сигнала на выходе элемента И при нарушении режима сети, т.е. номинальная последовательность импульсов превращается в постоянный сигнал, уровень которого случаен и определяется состоянием D-триггеров в момент аварии сети. Кроме того, недостатком устройства является срабатывание его при кратковременных снижениях напряжения в сети, вызванных, например, пуском рядом расположенного двигателя, захлестыванием проводов воздушной линии и т.п.

Таким образом, известное устройство имеет низкую функциональную надежность.

Цель изобретения - повышение надежности и расширение функциональных возможностей путем обеспечения защиты от обрыва фазы контролируемой сети.

Поставленная цель достигается тем, что в устройстве для контроля чередования фаз трехфазной сети, содержащем три входных вывода для подключения к фазам контролируемой сети, три входных преобразователя однополярных полуволн трех синусоидальных напряжений контролируемой трехфазной сети, сдвинутых одно относительно другого не менее чем на 120 эл. градусов, в, три последовательности прямоугольных импульсов, каждая из которых формируется на выходе соответствующего преобразователя,, два D-триггера, элемент И и исполнительный блок, причем D-вход первого триггера снабжен выводом для подключения к шине потенциала Логическая единица, а выход второго D-триггера подключен к первому входу элемента И, выход первого преобразователя подключен к С-входу первого и R-входу второго D-триггеров, вход второго преобразователя подключен к С- входу второго D-триггера, D-вход которого подключен к прямому выходу первого D- триггера, выход третьего преобразователя подключен к R-входу первого D-триггера и к второму входу элемента И, причем входные преобразователи выполнены так, что выходные импульсы каждого из них отделены временными интервалами от импульсов любого другого преобразователя, исполнительный блок выполнен с статическим разрешающим первым входом установки в состояние сигнализации Исправность и статическим запрещающим вторым входом установки в состояние сигнализации Неисправность, взаимодействующим с первым входом по логической схеме ЗАПРЕТ, и в устройство введены блок выдержки времени, выполненный со статическим первым входом включения отработки заданной временной задержки и вторым входом оперативного сброса наработанного текущего значения выдержки времени в исходное нулевое значение, и выпрямительный блок, входы кото- рого подключены к входным выводам устройства для подключения к фазам контролируемой сети, формирующий на своих выходных выводах постоянное напряжение при наличии на входных выводах устройст- ва по меньшей мере двух из трех синусоидальных напряжений контролируемой трехфазной сети, при этом выход элемента И подключен к второму входу блока выдержки времени, первый вход которого под- ключей к соответствующему выходному выводу выпрямительного блока и к первому входу исполнительного блока, второй вход которого подключен к выходу блока выдержки времени, при этом выводы питания эле- ментов устройства подключены к соответствующим выводам выпрямительного блока.

В качестве первого входа блока выдержки времени и первого входа исполнитель- ного блока могут служить выводы питания этих блоков.

Предлагаемая организация связей между элементами устройства обеспечивает появление однозначного сигнала на выходе элемента И при любом нарушении режима сети независимо от момента и места (какой- либо из фаз) его возникновения, что приводит к срабатыванию исполнительного блока и чем обеспечивается сигнализация отсутствия симметричного трехфазного напряжения с заданным порядком чередования фаз.

Таким образом, предлагаемое решение позволяет повысить надежность устройства

для контроля чередования фаз трехфазной сети и расширить его функциональные возможности в результате фиксации и исчезновения напряжения в любой из фаз, вызванного обрывом одного из линейных проводов или его коротким замыканием.

Кроме того, предлагаемое устройство характеризуется малым энергопотреблением, что позволяет его питание, включая исполнительный блок, осуществлять от измерительных цепей и тем самым исключить необходимость цепи оперативного тока.

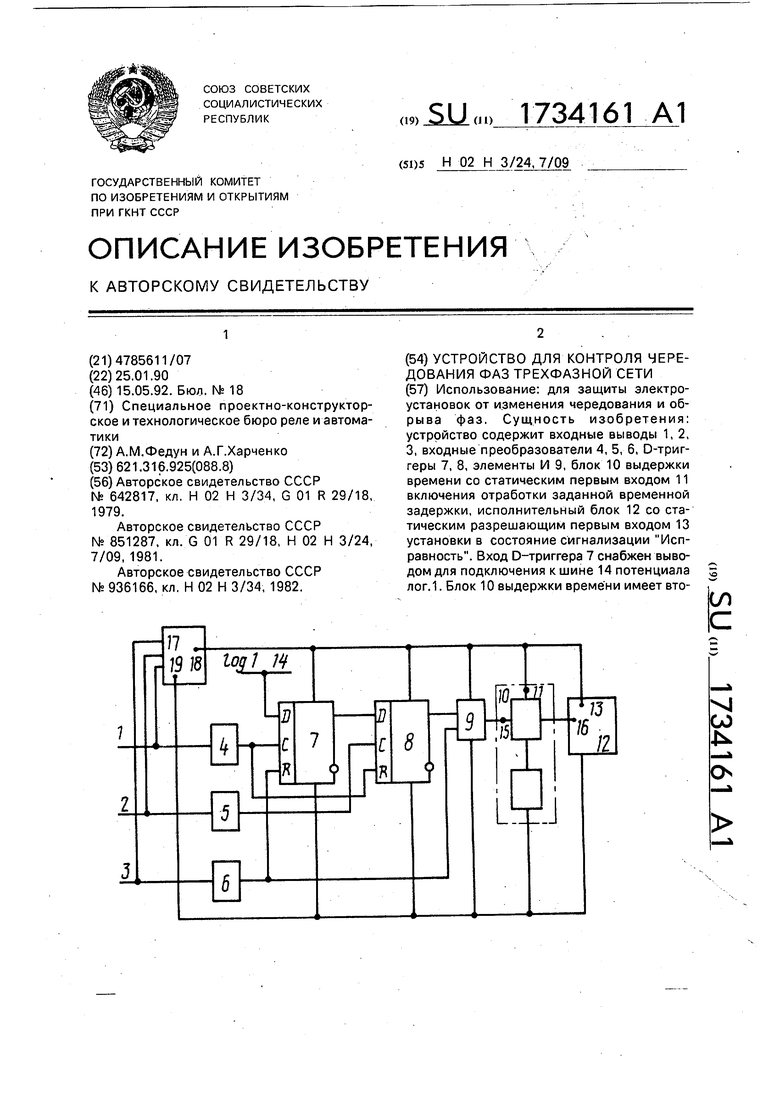

На чертеже представлена схема устройства.

Устройство для контроля чередования фаз трехфазной сети содержит три входных вывода 1-3 для подключения к фазам контролируемой сети, три входных преобразователя 4-6 однополярных полуволн трех синусоидальных напряжений контролируемой трехфазной сети, сдвинутых одно относительно другого на 120 эл. град., в три последовательности прямоугольных импульсов, каждая из которых формируется на выходе соответствующего преобразователя, два D-триггера 7 и 8, элемент 9 И, исполнительный блок 12. D-вход первого триггера 7 снабжен выводом для подключения к шине 14 потенциала Логическая единица, а выход второго D-триггера 8 подключен к первому входу элемента 9 И. Выход первого преобразователя 4 подключен к С-входу первого 7 и R-входу второго 8 D-триггеров. Выход второго преобразователя 5 подключен к С-входу второго D-триггера 8, D-вход которого подключен к прямому выходу первого D-триггера 7, выход YpeTbero преобразователя 6 подключен к R-входу первого D-триггера 7 и к второму входу элемента 9 И. Входные преобразователи 4-6 выполнены так, что выходные импульсы каждого из них отделены временными интервалами от импульсов любого другого преобразователя. Исполнительный блок 12 выполнен со статическим разрешающим первым входом 13 установки в состояние сигнализации Исправность и статическим запрещающим вторым входом 16 установки в состояние сигнализации Неисправность, взаимодействующим с первым входом по логической схеме ЗАПРЕТ.

Блок 10 выдержки времени выполнен со статическим первым входом 11 включения отработки заданной выдержки времени и вторым входом 15 оперативного сброса наработанного текущего значения выдержки времени в исходное нулевое значение. Устройство содержит выпрямительный блок 17, входы которого подключены к входным выводам 1-3 устройства для подключения к фазам контролируемой сети, формирующий на своих выходных выводах 18 и 19 постоянное напряжение при наличии на входных выводах устройства по меньшей мере двух из трех синусоидальных напряжений контролируемой трехфазной сети. Выход элемента 9 И подключен к второму входу 15 блока 10 выдержки времени, первый вход 11 которого подключен к соответствующему выходному выводу 18 выпрямительного блока 17 и к первому входу 13 исполнительного блока 12, второй вход 16 которого подключен к выходу блока 10 выдержки времени, при этом выводы питания элемен- тов устройства подключены к соответствующим выходным выводам 18 и 19 выпрямительного блока.

Устройство работает следующим образом.

При подаче трехфазного напряжения на вход устройства контроля чередования фаз срабатывает исполнительный блок 12 и переходит в дежурный режим (состояние сигнализации Исправность). Одновременно напряжение питания поступает на остальные элементы схемы, вступаете работу блок 10 выдержки времени и начинается отсчет выдержки времени.

При номинальном напряжении и пря- мом порядке чередования фаз импульсы на выходах преобразователей 4-6 составляют последовательность (очередность) 4-5-6- 4-5..., вызывая поочередное переключение D-триггеров 7 и 8, в результате чего на вы- ходе элемента И 9 присутствует последовательность 10010010... Каждый импульс высокого уровня (лог.1), поступая на вход 15 блока 10 выдержки времени, сбрасывает в нуль наработанное текущее значение вы- держки времени, и на вход 16 исполнительного блока 12 сигнала на срабатывание не поступает, что соответствует нормальному режиму контролируемой трехфазной сети.

Если порядок чередования фаз наруша- ется (например, нарушился порядок фаз В и С) или напряжение в любой из фаз понижается ниже установленного (допустимого) значения, то изменяется последовательность сигналов на выходах элементов 7 и 8, а на выходе элемента 9 вместо последовательности импульсов 10010... устанавливается сигнал низкого уровня, что разрешает счет, т.е. отсчет заданной выдержки времени на срабатывание.

Применение в блоке 10 счетчика с переменным коэффициентом деления или генератора с регулируемой частотой позволяет изменять задержку срабатывания и тем самым обеспечить селективность защиты.

В случае кратковременного нарушения режима сети, когда в течение заданного промежутка времени напряжение фаз восстанавливается, первый же импульс высокого уровня с выхода элемента 9 производит сброс счетчика узла 10 в нулевое состояние, что предотвращает ложное срабатывание исполнительного блока 12.

Кроме того, предлагаемое построение схемы повышает ее помехоустойчивость, так как в случае возникновения в сети значительного импульсного перенапряжения и его проникновения по паразитным емкостям и сопротивлениям утечки вдоль схемы, импульс помехи, достигнув счетчика, сбрасывает его в нуль, но не сможет воздействовать на исполнительный блок 12. Потому схема работоспособна не только при синусоидальных напряжениях, но и в условиях значительных (до 40%) нелинейных искажений, вызываемых, например, работой тири- сторных преобразователей или сварочного оборудования.

Формула изобретения

времени, первый вход которого подключен к соответствующему выходному выводу выпрямительного блока и к первому входу исполнительного блока, второй вход которого подключен к выходу блока выдержки времени, при этом выводы питания элементов устройства подключены к соответствующим выходным выводам выпрямительного блока.

| Устройство для контроля чередования фаз трехфазной сети | 1977 |

|

SU642817A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля чередованияфАз ТРЕХфАзНОгО пЕРЕМЕННОгО НАпРяжЕНия | 1979 |

|

SU851287A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля чередования фаз трехфазной сети | 1980 |

|

SU936166A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-05-15—Публикация

1990-01-25—Подача