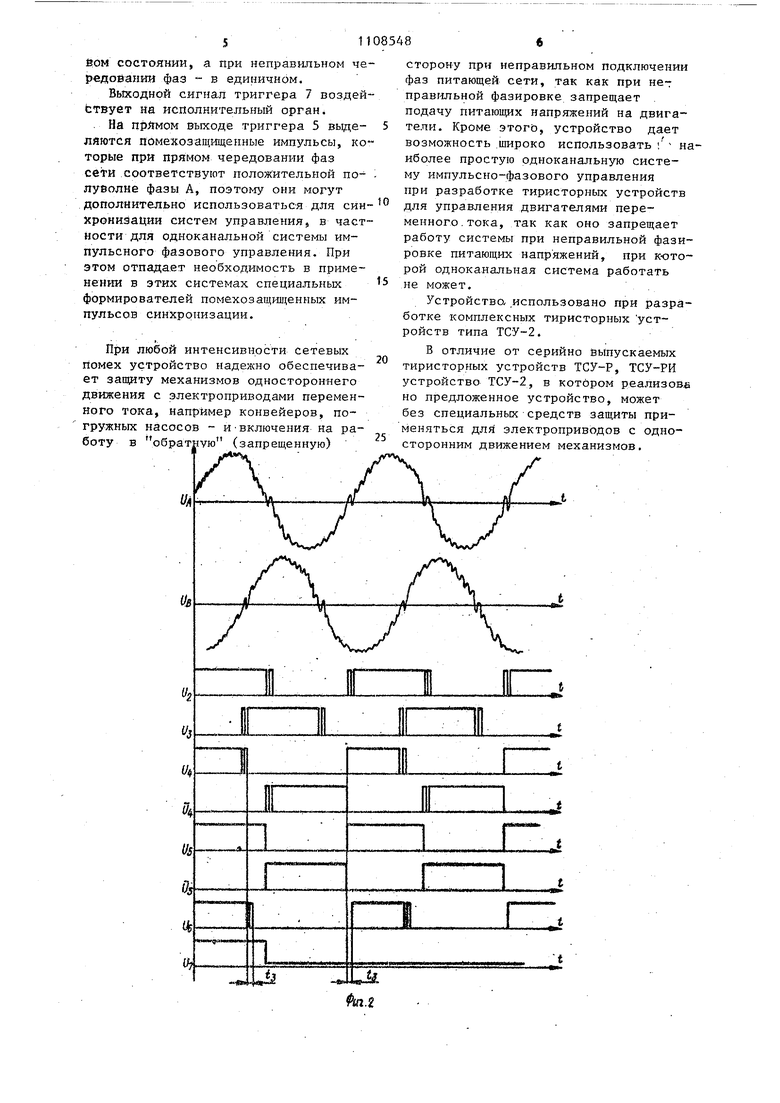

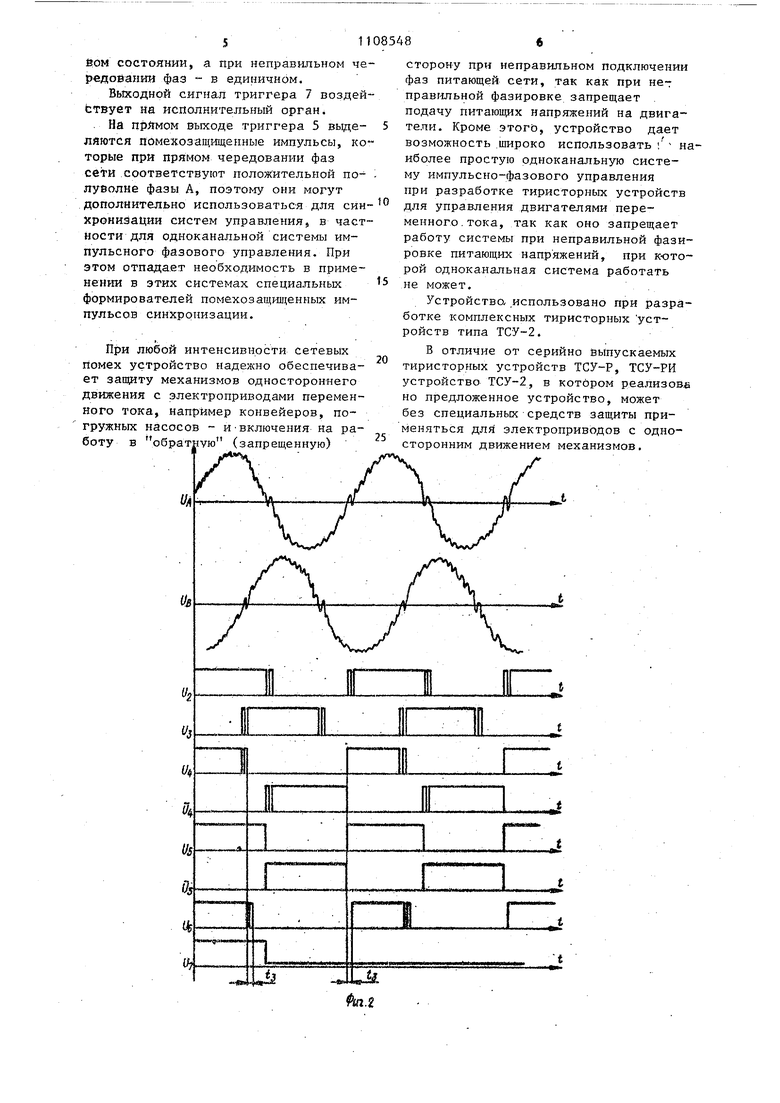

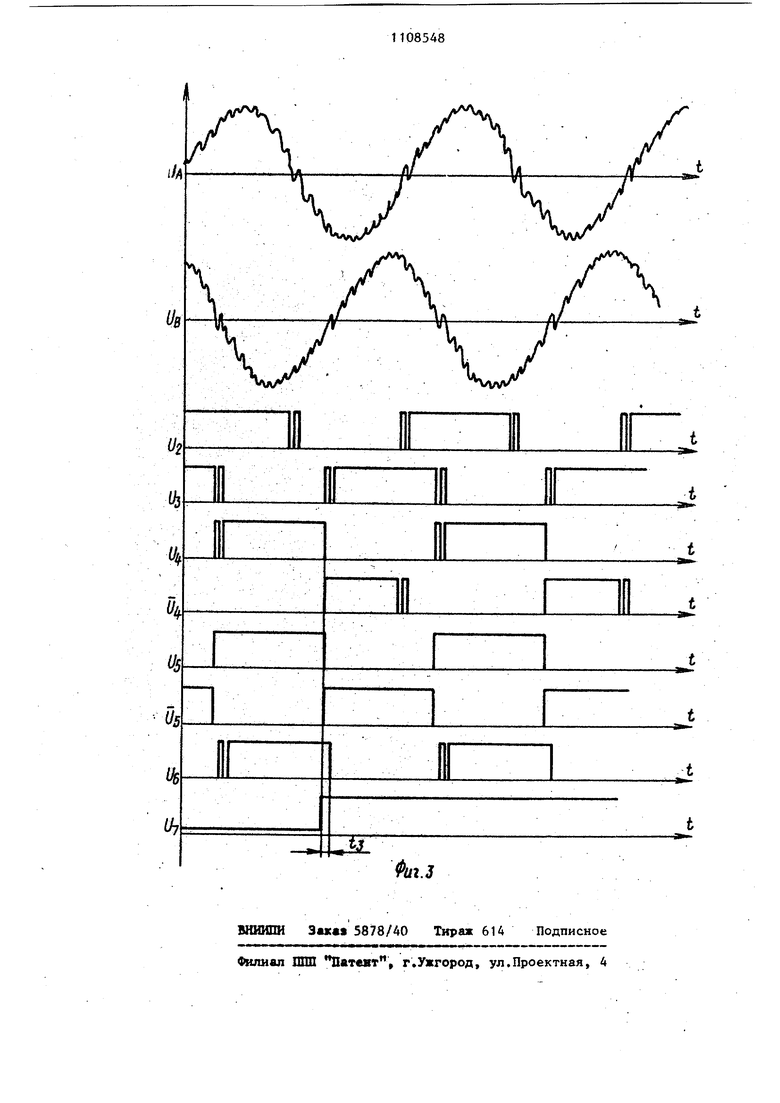

Изобретение относится к электротехнике и может быть использовано для защиты систем управления трехфазной нагрузкой и самой .трехфазной нагрузки от неправильного чередования фаз, например, в электроприводе, где требуется обязательное соблю дение направления вращения двигателя или в системах управления трехфазной нагрузкой с одноканальнйй сие импульсно-фазового управления. Известно устройство для защиты трехфазного электродвигателя от вращения в обратном направлении, содержащее три преобразователя синусоидального сигнала в серию прямоугольных импульсов, четыре логически элемента И, триггер и исполнительное устройство Т3. Недостатками этого устройства являются инерционность отсутствие однозначной информации о чередовании фаз сети в любой произвольный момент времени, а также необходимость приме нения трехканального преобразователя синусоидальных сигналов в импульсные и узла интегрирования выходных .импульсных сигналов. Наиболее близким по технической сущности к предлагаемому является устройство защиты от неправильного включения фазы, содержащее пороговы блок, два триггера, интегрирующую цепь и выходное устройство. Выходы порогового блока подклйчены к D -вхо ду и синхронизирующему входу первого Б -Триггера, на выходе которого установлена интегрирующая RC-цепь (f 1 с), выполняющая роль элемента задержки, выход которого подключе КО второй половине микросхемы - второму D-триггеру, используемому в качестве согласующего элемента 2. Устройство работает следующим образом. Передний фронт каждого сигнала, поступающего на синхронизирующий вхо первого D-триггера, при правильном чередовании фаз приходится на единич ный уровень сигнапа на его D-входе, а при неправильном чередовании фаз на нулевой уровень сигнала. Поэтому при отсутствия помех в первом случае первый 0 триггер постоянно находится в единичном состоянии, а во втором в нулевом, что надежно обеспечивает соответственно отключенное и включенное состояние исполнительного ус ройства. Происходит это из-за следую щего. При наличии помех на фронтах выходных сигналов порогового блока появляется дребезг и, если фазы сети подключены правильно ,-то по за. нему фронту сигнала на синхронизирующем входе первого D-триггера он ложно устанавливается в нулевое состояние, а по переднему фронту следующего сигнала - вновь устанавливается в единичное; в случае неправильного чередования фаз по дребезгу на зад нем фронте сигнала, поступающего на синхронизирующий вход первого D-тpи гepa, он ложно устанавливается в единичное состояние, а по переднему фронту очередного сигнала триггер сбрасывается в нулевое состояние. При большой интенсивности помех на выходе первого триггера появляются импульсы, скважность которых может доходить до двух, как при правильном, так и неправильном чередовании фаз сети. При этом в обоих случа л сигнал на выходе элемента задержки может иметь практически один и тот же уровень, что неизбежно приводит к сбоям в работе устройства. Наличие элемента задержки предотвращает сбои устройства лить при малой интенсивности помех, так как уровень сигнала на выходе этого элемента при правильном чередовании фаз имеет значение, близкое к максимальному, а при неправильном чередовании близкое к нулевому. Недостатками известного устройства является то, что оно имеет большую инерционность и при работе в сетях с больщим уровнем Промыпшенных помех, в частности питающих статические преобразователи, устройство дает сбои. .Целью изобретения является повышение помехоустойчивости и быстродействия устройства защиты от неправильного подключения фаз трехфазной сети. Указанная цель достигается тем, что устройство для защиты электроустан&вки от неправильного чередования фаз, содержащее пороговый блок, подключенный к двум контролируемым фазам, D -триггер, элемент задержки и исполнительньй орган, дополнительно снабжено двумя R5 -триггерами, причем запускающий и сбрасывающий входы первого RS-триггера подсоединены соответственно к первому и второму выходам порогевого блока, запускающий и сбрасывающий входы второго RS-триггера, подключены соответственно к прямому и инверсному вькодам первого тригге ра, вход элемента задержки подключен к прямому выходу первого триггера, D -триггер С-входом . под ключен к инверсному выходу второго триггера и D -входом - к выходу элемента задержки. На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 - временные диаграммы работы элементов устройства при прямой цоследовательности чередования фаз; на фиг.З - то же, при обратной посл довательности . Устройство содержит пороговый блок 1, состоящий из двух пороговы элементов 2 и 3, подключенных к фа зам А и В контролируемой сети, R5 триггеры 4 и 5, элемент задержки 6, D -триггер 7 и исполнительньй орган 8. R и 5 -входы триггера 4 подключены к выходам пороговых элементов 2иЗ, а Ри 5 -входы триггера 5 подключены соответственно к прямому и инверсному выходам триггера 4. Вход элемента задержки 6 подключен к прямому выходу триггера 4. С-вход D -триггера 7 подключен к инверсно му выходу триггера 5, а его D -вход к вьгходу элемента задержки 6.Устройство работает следующим об разом. На входы пороговых элементов 2 и 3 поступают синусоидальные сигналы напряжения фаз А и В. С выходов элементов 2 и 3 выдаются импульсы. и и Ua с периодом повторения, ра ным периоду сети, и длительност н), р ной полпериода сети. При наличии се тевых помех на фронтах этих сигнало появляется дребезг в виде одного или нескольких кратковременных импульсов. При правильном чередовании фаз передний фронт импульса И опережает передний фронт импульса И на 120 эл.град. По переднему фронту импульса и R5 -триггер 4 устанавли ется в единичное состояние, его выходной сигнал и имеет единичный ур вень, а сигнал соответственно нулевой. Если сигналы Uj и Uj одновременно имеют единичньй уровень, то сигналы и н U также одновремен но имеют нулевой уровень, поэтому 8 - 4 и.. уро по переднему фронту сигнала вень и становится нулевым. Однако при наличии дребезга на переднем фронте сигнала Ujзадний фронт сигнала и также имеет дребезг. - --Li По заднему фронту сигнала триггер 4 устанавливается в нулевое состояние, но при наличии дребезга на заднем фронте сигнала U передний фронт сигнала U также имеет дребезг. Передний фронт сигнала U. и задний фронт сигнала U/ формируются по переднему фронту сигнала U они помехозащиценные, так как передний фронт сигнала. Ug совпадает с нулевым уровнем сигнала Uj и кратковременные исчезновения сигнала U. не изме нягот состояния триггера. Импульсы и 64 поступают соответственно на 5 и R -входы триггера 5, но так как искаженные помехами фронты сигналов VJ.vl U не имеют одновременно единичного уровня, то на выходах триггера 5 формируются Ugс обоими помехозащиимпульсы ис и щенными фронтами. Импульсы Uj поступают на С-вход Б -триггера 7, а на его D -вход через элемент задержки 6 поступают импульсы U.4 с прямого вьгхода триггера 4. Элемент задержки задерживает передний и задний фронт импульсов только на время tл необходимое для последовательного срабаты-. вания триггеров 5 и 7, составляющее 0,15-0,5 МКС. Поэтому при правильном чередовании фаз сети во время прихода переднего фронта каждого импульса JC на D-входе триггера 7 будет нулевой уровень, и D -триггер становится в нулевое состояние или подтверждается его нулевое состояние. .При неправильном чередовании фаз сигнал и опережает сигнал V на 120 эл.град,, при этом аналогично триггер 4 фopмlipyeт сигналы U, имеющие по одному помехозащищенному фронту, а,триггер 5 формирует сигналы Uyii Uj с обоими помехозащищенными фронтами. При этом по переднему фронту каждого импульса Uj, который при неправильном чередовании фаз всегда совпадает с единичным уровнем 7 устанавливается сигнала Ц триггер в единичное состояние или подтверлща-ется его единичное состояние. Таким образом, независимо от наличия и интенсивности сетевых помех, при правильном чередовании фаз сети триггер 7 постоянно находится в нулейом состоянии, а при неправильном че редовании фаз - в единичном. Выходной сигнал триггера 7 воздей ствует на исполнительный орган. . На прймом выходе триггера 5 выделяются помехозащищенные импульсы, ко торые при прямом чередовании фаз сети соответствуют положительной полуйолне фазы А, поэтому они могут дополнительно использоваться для син хрониэации систем управления, в част ности для одноканальной системы импульсного фазового управления. При этом отпадает необходимость в применении в этих системах специальных формирователей помехозащищенных импульсов синхронизации. При любой интенсивности сетевых Помех устройство надежно обеспечивает защиту механизмов одностороннего движения с электроприводами переменного тока, например конвейеров, погружных насосов - иВключения на работу в обратную (запрещенную) сторону при неправильном подключении фаз питающей сети, так как при неправильной фазировке запрещает подачу питающих напряжений на двигатели. Кроме этого, устройство дает возможность широко использовать . наиболее простую рдноканальную систему импульсно-фазового управления при разработке тиристорньпс устройств для управления двигателями переменного . тока, так как оно запрещает работу системы при неправильной фазировке питающих напряжений, при которой одноканальная система работать не может. Устройство, .использовано при разработке комплексных тиристорных устройств типа ТСУ-2. В отличие от серийно выпускаемых тиристорных устройств ТСУ-Р, ТСУ-РИ устройство ТСУ-2, в котором реализовй но предложенное устройство, может без специальных средств защиты применяться для электроприводов с односторонним движением механизмов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов датчика положения | 1991 |

|

SU1836661A3 |

| Устройство для обнаружения первого события | 1986 |

|

SU1385290A1 |

| Формирователь дискретных сигналов | 1979 |

|

SU809523A1 |

| Способ селекции импульсных сигналов и устройство для его осуществления | 1988 |

|

SU1541762A1 |

| Устройство для контроля чередования фаз трехфазной сети | 1980 |

|

SU936166A1 |

| Устройство для автоматической настройки дугогасящего реактора в режиме однофазного замыкания на землю в сети | 1986 |

|

SU1367096A1 |

| Устройство для контроля чередования и обрыва фаз трехфазной сети | 1987 |

|

SU1429213A1 |

| Формирователь дискретных сигналов | 1982 |

|

SU1115210A1 |

| Устройство для защиты трехфазных сетей от неправильного чередования фаз | 1978 |

|

SU744830A1 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ЭЛЕКТРОУСТАНОВКИ ОТ НЕПРАВИЛЬНОГО ЧЕРЕДОВАНИЯ ФАЗ, содержащее пороговый блок, подключенный к двум. . ЛВС контролйруер- ым фазам, D-триггер, элемент задержки и исполнительный оргай, отличающееся тем, что., с целью повышения помехоустойчивости и быстродействия, оно дополнительно снабжено двумя RS-триггерами, причем S и R-входы первого RS-триггера подсоединены соответственно к первому и второму выходам порогового блока, запускающий и сбрасывающий входы второго RS-триггера подключены соответственно к прямому и инверсному выходам первого триггера, вход элемента задержки подключен к прямому выходу г;арвогЬ триггера, а D-триггер С-входом подключен к инверсному выходу второго (Л триггера и D-входом к выходу элес мента задержки. 00 СП 4; 00, / Н ft/t./

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для защиты трехфазного электродвигателя от вращения в обратном направлении | 1978 |

|

SU744838A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электроника, М,, Мир, 1982, № 11, с.80 | |||

Авторы

Даты

1984-08-15—Публикация

1983-04-16—Подача