1

GO

сл

00

Јь

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета для подключения к общей магистрали | 1990 |

|

SU1749896A2 |

| Многоканальное устройство приоритета для подключения к общей магистрали | 1990 |

|

SU1714601A2 |

| Многоканальное устройство приоритета для подключения к общей магистрали | 1986 |

|

SU1386994A1 |

| Многоканальное устройство приоритета для подключения к общей магистрали | 1988 |

|

SU1508212A2 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1986 |

|

SU1381508A1 |

| Многоканальное приоритетное устройство | 1984 |

|

SU1239716A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1987 |

|

SU1462338A1 |

| Устройство для сопряжения электронной вычислительной машины с общей магистралью | 1987 |

|

SU1411765A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1989 |

|

SU1589277A2 |

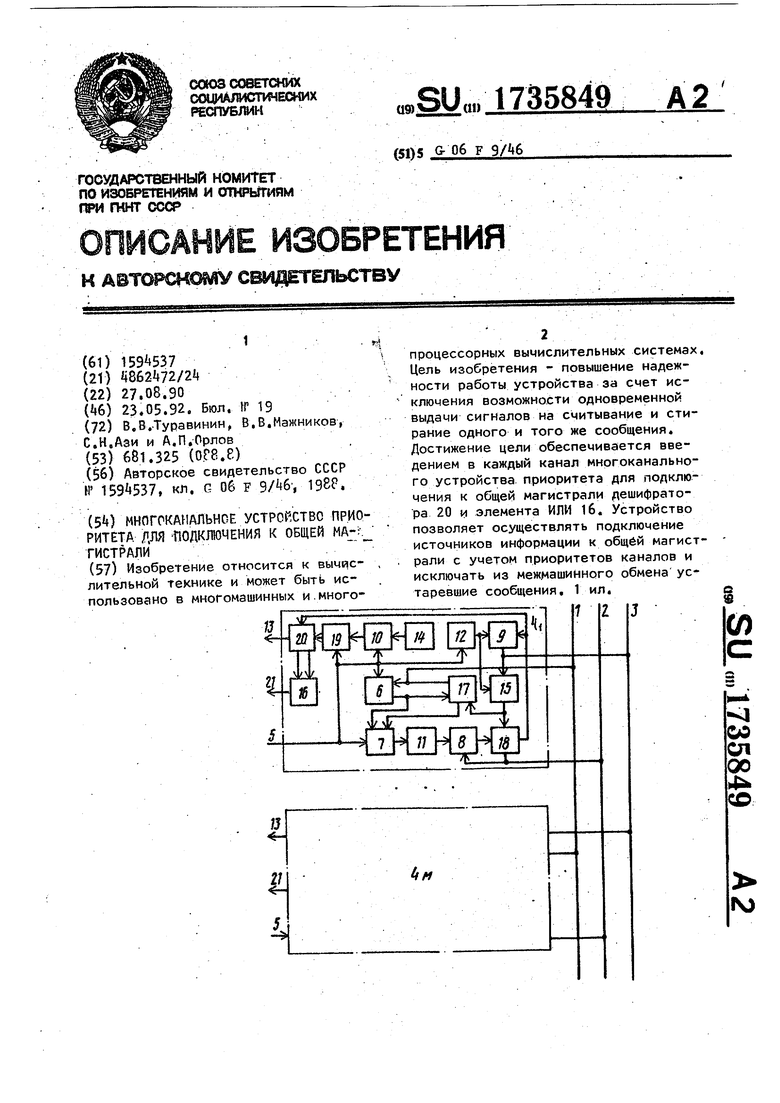

Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах. Цель изобретения - повышение надежности работы устройства за счет исключения возможности одновременной выдачи сигналов на считывание и стирание одного и того же сообщения. Достижение цели обеспечивается введением в каждый канал многоканального устройства приоритета для подключения к общей магистрали дешифратора 20 и элемента ИЛИ 16. Устройство позволяет осуществлять подключение источников информации к общей магистрали с учетом приоритетов каналов и исключать из межмашинного обмена устаревшие сообщения. 1 ил.

)

3-

Изобретение относится к вычислительной технике, может быть применено в многомашинных и многопроцессорных вычислительных системах, использующих для оГмена данными общую магистраль и является усовершенствованием изобретения по авт. св.

Г 1Ь94557.

Известно многоканальное устройств приоритета для подключения к общей магистрали, содержащее сигнальные выходы, каналы, каждый из которых включает запросный вход, элемент И, элемент задержки, формирователь импульсов, информационный выход, генератор импульсов, элемент ИЛИ, выход, триггеры и счетчик, причем в каждом канале выход генератора импульсов соединен с вторым входом пятого элемента И, запросный вход соединен с первыми входами первого, второго и пятого элементов И, входом сброса счетчика и входом формирователя импульсов, выход которого соединен с первыми входами четвертого элемента и элемента ИЛИ, выход которого соединен с входами сброса первого и второго триггеров, второй вход элемента ИЛИ соединен с выходом четвертого элемента И, второй вход которого соединен с информационным выходом канала и единичным выходом второго триггера , единичный вход которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом элемента задержки, вход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом первого элемента И и единичным входом первого триггера, единичный выход которого соединен с третьим входом второго элемента И, выход пятого элемента И соединен со счетным входом счетчика, выход которого является выходом канала, первый сигнальный выход устройства соединен с вторыми входами первых элементов И и нулевыми выходами первых триггеров всех каналов. Второй сигнальный выход устройства соединен с вторыми входами третьих элементов И и нулевыми выходами вторых триггеров всех каналов. Третий сигнальный выход устройства соединен с выходами четвертых элементов И всех каналов.

Данное устройство обеспечивает приоритетный доступ к общей магистрали (ПМ) источников информации, фор

15

-4

мируя для этого сигналы на информационных выходах каналов, и отсев из очереди на передачу через ОМ источниками информации сообщений, время ожидания которых превысило допустимое, формируя для этого сигналы на выходах каналов.

Сигналы на выходе и информационном

JQ выходе каждого канала формируются независимо один от другого, что не исключает их одновременного появления, а это может привести к тому, что одновременно начнет передаваться в ОМ (по сигналу с информационного выхода) сообщение и оно же начнет стираться из ячейки буферной памяти источника информации (например, ЭВМ). В этом случае за счет разброса во

2Q время срабатывания элементов в ОМ может выдаться искаженное сообщение (некоторые разряды успели стереться а некоторые нет), что приведет к сбою в работе вычислительной системы.

25 Таким образом, недостатком известного устройства является низкая надежность.

Цель изобретения - повышение надежности работы устройства за счет исключения возможности одновременной выдачи сигналов на считывание и стирание одного и того же сообщения.

Цель достигается тем, что в каждый канал многоканального устрой35 ства приоритета для подключения к общей магистрали дополнительно введены дешифратор и элемент ИЛИ, причем единичный выход второго триггера и выход счетчика соединены

40 соответственно с первым и вторым входами дешифратора, первый выход которого является выходом захвата магистрали устройства, а второй и третий выходы дешифратора сое45 динены с входами элемента ИЛИ, выход которого является выходом устаревших сообщений устройства. 1

На чертеже изображена структур50 пая схема устройства.

Устройство содержит сигнальные выходы 1-3, каналы А, каждый из которых включает запросный вход 5, элементы И 6 - 10, элемент 11 за30

55

держки, формирователь 12 импульсов, выход 13 захвата магистрали устройства, генератор 1 импульсов, элементы ИЛИ 15 и 16, триггеры 1 и 1Р,

3

счетчик 19, дешифратор 20 и выход 21 устаревших сообщений устройства.

Устройство работает следующим образом,

В исходном состоянии триггеры 17 и 18 и счетчики 19 всех каналов находятся в нулевом состоянии, На входы 5 всех каналов k от соответствующих источников информации (например, ЭВМ) поступают сигналы логического нуля, что обуславливает нличие сигналов логической единицы (высоких уровней) на первом 1 и втором 2 сигнальных выходах устройства и сигналов логического нуля на выходах 13 и 21 каналов k и третьем сигнальном выходе 3 устройства.

Объединение выходов элементов устройства на первом и втором сигнальных выходах устройства реализуют функцию проводное И, а на тре- тьем сигнальном выходе проводное ИЛИ.

В случайные моменты времени ЭВМ заносит в свои ячейки буферной памяти сообщения, предназначенные для передачи через ОМ. Каждый источник информации подключен через.запросный вход 5, выход 21 и выход 13 к соответствующему каналу (источники информации и ОМ не показаны), При появлении в ячейке буферной памяти какой,-либо ЭВМ сообщения на входе 5 соответствующего канала k устройства устанавливается сигнал логической единицы (этот сигнал исчезает при освобождении соответствующей ячейки памяти).

Далее рассмотрим работу одного из каналов Ь, так как в остальных кналах работа осуществляется аналогичным образом.

Единичный сигнал с запросного входа 5 в рассматриваемом канале (например, в первом канале k) поступает на вход элемента И б и открывает элемент И 10, через который на счетчик 19 начнут поступать импульсы с генератора }h импульсов, отсчитывая время ожидания сообщения в очереди на передачу через СМ, Единичный сигнал, пройдя через открыты элемент И 6, устанавливает триггер 17 в единичное состояние, что приво дит к установлению на первом сигналном выходе 1 устройства сигнала логического нуля, следовательно, крываются элементы И 6 всех каналов 4 (т.е. запросы от ЭВМ на захват ОМ

-

с данного момента времени в уст ройст- ве не фиксируются).

После установления на единичном , выходе триггера 17 сигнала логической единицы и до момента пропадания единичного сигнала на выходе элемента И 6 на выходе элемента И 7 будет установлен сигнал логической едиJQ ницы, который, пройдя через элемент 11 задержки и открытый элемент И 8, устанавливает триггер 18 в единичное состояние. Задержка на элементе 11 задержки в каждом канале устанавли. 5 вается со значением, отличающимся от задержки на элементе 11 в других каналах на величину интервала времени большую, чем необходимо для прохождения сигнала по элементам 8 и 18

2Q и сигнальному выходу 2 устройства

между двумя наиболее удаленными каналами 4. При этом исключается возможность одновременного подключения нескольких каналов к ОМ,

25 Сигнал с единичного выхода триг гера 18 поступает на перзый вход дешифратора 20, в результате чего на его первом выходе появляется единичный сигнал, который через выход 1.3 канала А сигнализирует ЭВМ о том, что ОМ захвачена и можно начинать передачу информации Одновременно сигнал логического нуля с нуле юго выхода триггера 18 через сигнальный выход 2 устройства закрывает во всех

35 каналах 4 элементы И 8 и, если одновременно осуществлялись попытки захватить ОМ другими каналами, у которых приоритет ниже (больше время задержки сигнала на элементе 11),

40 чем у данного канала 4, то попытки будут блокироваться.

После того, как ЭВМ, подключенная к данному каналу г, закончит передачу сообщения, она установит на за4$ просном входе 5 своего канала сигнал логического нуля. По отрицательному перепаду уровня сигнала на запросном входе 5 происходит обнуление счетчика 19 и формирователь 12 импульсов

50 в данном канале А сформирует одиночV,

ный импульс, который через элемент ИЛИ 15 установит триггеры 17 и 18 этого канала (а через элемент М 9, сигнальный выход 3 устройства и эле- менты ИЛИ 15 менее приоритетных каналов триггеры 17 в этих каналах, где i

осуществлялась одновременная попытке

захвата ОМ) в нулевое состояние.

30

Если при поступлении сигнала на запросный вход 5 первого канала k ОМ была занята другим каналом vt к мог- менту времени Т « Т + Тд, .где Т - ( время поступления сообщения в ячейку буферной памяти I ЭВМ, а ТЛ - допустимое время ожидания сообщения в очереди на передачу первому каналу А не удалось захватить ОМ, то в этот момент в первом канале на выходе счетчика 19, а следовательно, на втором входе и втором выходе дешифратора 20 появится единичный сигнал, который через элемент ИЛИ 16 поступит на вы- хбд 21 первого канала, свидетельствуя о том, что сообщение, записанное в ячейку буферной памяти I ЭВМ, ожидает в очереди на передачу потребителю через ОМ время, равное допустимому и, следовательно, уже потеряло свою ценность. Передавать такое сообщение через ОМ нецелесообразно, поэтому CHI- нал с выхода 21 первого канала k поступает в I ЭВМ и обеспечивает стирание сообщения в ячейке буферной памяти, т.е. ликвидацию заявки на захват ОМ, что приводит к появлению на входе 5 первого канала логического нуля.

Отрицательный перепад сигнала на входе- 5 поступает на вход формирователя 12 импульсов и он формирует оди«- ночный импульс, который установит триггер 17, через элемент ИЛИ 15, (если он ранее при одновременной попытке захвата ОМ был установлен в единичное состояние, а канал 4 по , причине своего низкого приоритета все же не захватил ОМ) в нулевое состояние, а на другие каналы воздействия не окажет, Так как элемент И 9 закрыт по второму входу сигналом логического нуля с единичного выхода триггера 18.

Если при поступлении сигнала на запросный вход 5 первого канала А ОМ была занята другим каналом 4, но вскоре освободилась и первый канал захватил ее к моменту времени Т « Tj + Тд, то в этот момент на первом и втором входах дешифратора 20 появятся единичные сигналы которые вызовут формирование единичного сигнала на третьем выходе дешифратора

20и через элемент ИЛИ 16, на выходе

21канала, причем на выходе 13 канала единичный сигнал не появится, что исключает возможность передачи через ОМ устаревшего и возможно искаженного (за счет того, что ряд разрядов со

общения могли быть стерты ,и в таком / виде сообщение выдано в ОМ, как это не исключалось в известном устройст. ве, поскольку сообщение при -выдаче в ОМ одновременно и стиралось, так как одновременно могли выдаваться сигналы на информационный выход и выход канала А сообщения.

JQ Таким образом, предлагаемое устройство позволяет повысить достоверность сообщений, передаваемых через ОМ, т.е. имеет более высокую надежность по сравнению с известным уст15 ройством.

Дес ятимашинная вычислительная система на этапе межмашинного обмена работает следующим образом.

Пусть вероятность одновременного

20 появления сигналов на выходе 21 (сигнал для стирания сообщения) и выходе 13 (сигнал для передачи сообщения) в одном канале равна 0,01. Тогда при равновероятных возможностях появле25 ния таких событий в каждом канале, вероятность выдачи искаженного сообщения в ОМ (появления сбоя в работе вычислительной системы) при исполь- зовании базового устройства будет

30 равна 0,1.

При использовании предлагаемого устройства для организации межмашинного обмена за счет него искажения сообщений возникать не будут. Таким образом, использование предлагаемого

35 устройства позволяет на 10% повысить надежность работы вычислительной системы.

Ф ормула изобретения

Многоканальное устройство приоритета для подключения к общей магистрали по авт. св. К , отличающееся тем, что, с целью

повышения надежности за счет исключения возможности одновременной выдачи сигналов на считывание и стирание одного и того же сообщения, оно дополнительно содержит дешифратор и

элемент ИЛИ, причем единичный выход второго триггера и выход счетчи-ка соединены соответственно с первым и вторым входами дешифратора, первый выход которого является выходом захвата магистрали устройства, а второй и третий выходы дешифратора соединены с входами элемента ИЛИ, выход которого является выходом устаревших сообщений устройства.

| Авторское свидетельство СССР № , кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1992-05-23—Публикация

1990-08-27—Подача