1

(61 ) 1458873

(21 ) 4639245/24-24

(22) 18,01.89

(46) 30.08.90. Бюл. № 32

(72) В.В.Туравинин, С.Н.Ази,

В.В.Мажников и В.Г,Попов

(53) 681.325 (088.8)

(56)Авторское свидетельство СССР № 1458873. кл. G 06 f 9/46, 1987.

(54); МНОГС;КАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРИОРИТЕТНОГО ПОДКЛЮЧЕНИЯ АБОНЕНТОВ К ОБЩЕЙ МАГИСТРАПИ

(57)Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах. Цель изобретения - повышение быстродействия устройства. Устройство в каждом канале содержит триггеры 5-7, элементы И 8-11, формирователи 12, 13 импульсов, элементы НЕ 14, 15, элементы И-НЕ 16, 17, элемент 18 задержки, блок 23 задержки. .Устройство позволяет организовать подключение абонентов к общей магистрали в соответствии с их приоритетами, которые могут оперативно изменяться при настройке вычислительной системы. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1987 |

|

SU1458873A2 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1984 |

|

SU1239717A1 |

| Устройство для связи процессоров в вычислительной системе | 1988 |

|

SU1515170A1 |

| Устройство для сопряжения процессоров в вычислительной системе | 1985 |

|

SU1332327A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1986 |

|

SU1397914A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1987 |

|

SU1462311A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1989 |

|

SU1709312A1 |

| Многопроцессорная вычислительная система | 1991 |

|

SU1837309A1 |

| Устройство для формирования и анализа семантических сетей | 1989 |

|

SU1619289A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах. Цель изобретения - повышение быстродействия устройства. Устройство в каждом канале содержит триггеры 5-7, элементы И8-11, формирователи импульсов 12,13, элементы НЕ 14,15, элементы И-НЕ 16, 17, элемент задержки 18, блок 23 задержки. Устройство позволяет организовать подключение абонентов к общей магистрали в соответствии с их приоритетами, которые могут оперативно изменяться при настройке вычислительной системы. 2 ил.

Фиг.1

Иэооретение относится к вычислительной техшке, может быть применено в нoгoмaшннныx и .многопроцессор- ;ных вычислительных системах, исполь- эукхцих для обмене данными общую магас- траль (ом), и является усовершенствованием изобретею1я по авт.. св..№ 1458873.

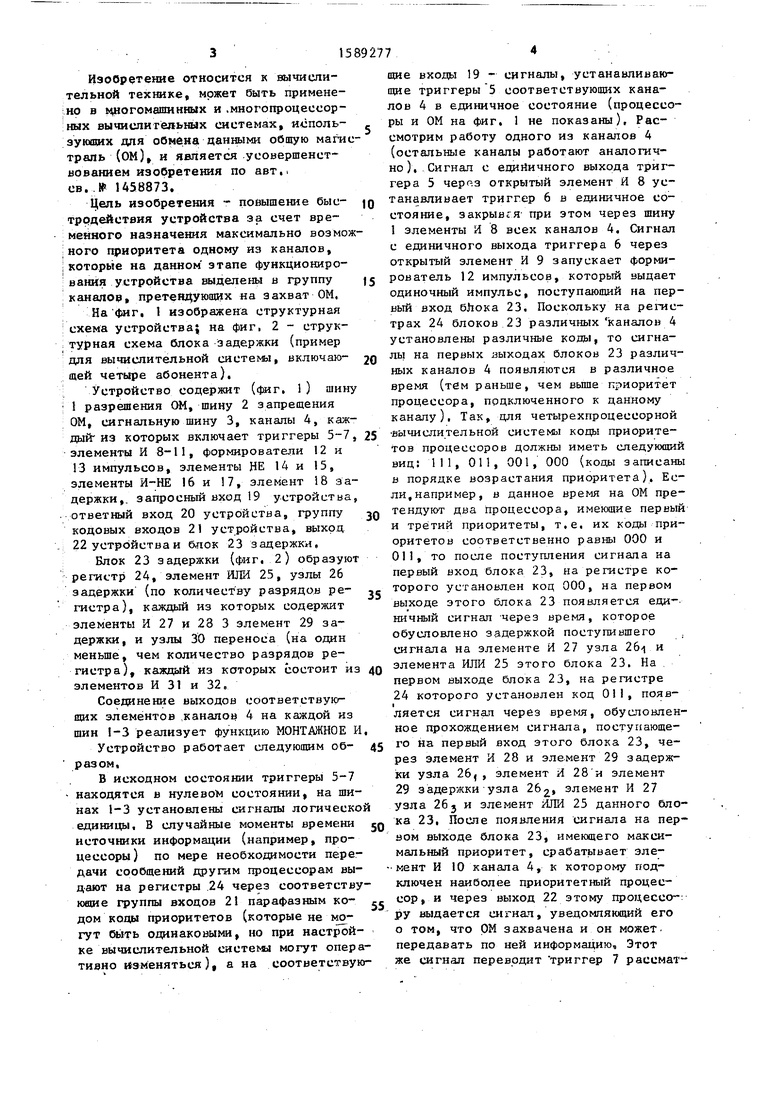

Цель изобретения - повышение быс- тррдействия устройства за счет вре- мейного назначения максимально возмож- ного приоритета одному из каналов, I которые на данном зтапе функциониро- вания устройства выделень в группу каналов, претендующих на захват ОМ. На фиг, 1 изображена структурная Гсхема устройства на фиг, 2 - струк- ; турная схема блока задержки (пример для вычислительной систе1УЫ, включаю- щей четыре абонента). : Устройство содержит (фиг. 1) шину

1 разрешения ОМ, шину 2 запрещения ОМ, сигнальную шину 3, каналы 4, к,зж- хдай из которых включает триггеры 5-7, элементы И 8-11, формирователи 12 и

13 импульсов, элементы НЕ 14 и 15, элементы И-НЕ 16 и 17, элемент 18 задержки,, запросный вход 19 устройства, ответный вход 20 устройства, группу кодовых входов 21 устройства, выход 22 устройстваи блок 23 задержки.

Блок 23 задержки (фиг. 2) образуют регистр 24, элемент ИЛИ 25, узлы 26 задержки (по количеству разрядов ре- гистра), каждый из которых содержит элементы И 27 и 23 3 элемент 29 задержки, и узлы 30 переноса (на один меньше, чем количество разрядов регистра), каждый из которых состоит из элементов И 31 и 32.

Соединение выходов соответствующих элементов каналов 4 на каждой из шин 1-3 реализует функцию МОНТАЖНОЕ И

Устройство работает еэтедующим об-

разом,

В исходном состоянии триггеры 5-7

находятся в нулево1м состоянии, на шинах 1-3 установлены сигналы логическо единицы, В случайные моменты времени источники информации (например, процессоры) по мере необходимости передачи сообщений другим процессорам выдают на регистры 24 через соответствующие группы входов 21 парафазным ко- дом коды приоритетов (которые не NIO- гут GbVTb одинаковыми, но при настройке вычислительной системы могут опертивно изменяться), а на соответствующие входы 19 - сигналы, устанавливающие триггеры 5 соответствующ11х каналов 4 в единичное состояние (процессоры и ОМ на фиг. 1 не показаны). Рассмотрим работу одного из каналов 4 (остальные каналы работают аналогично). Сигнал с единичного выхода триггера 5 черр-з открытый элемент И 8 устанавливает триггер 6 в единичное состояние, закрывая при этом через шину 1 элементы И 8 всех каналов 4. Сигнал с единичного выхода триггера 6 через открытый элемент И 9 запускает формирователь 12 импульсов, который выдает одиночный импульс, поступающий на первый вход бЛока 23. Поскольку на регистрах 24 блоков 23 различных каналов 4 установлены различные коды, то сигналы на первых выходах блоков 23 различных каналов 4 появляются в различное время (тем раньше, чем вьш1е приоритет процессора, подключенного к данному каналу), Так, для четырехпроцессорной вычислительной системы коды приоритетов процессоров должны иметь следуюаий вид: 111, 011, 001, 000 (коды записаны в порядке возрастания приоритета). Если, например, в данное время на ОМ претендуют два процессора, имеющие первый и третий приоритеты, т.е. их коды приоритетов соответственно равны 000 и 011, то после поступления сигнала на первый вход блока 23, на регистре которого установлен код 000, на первом выходе этого блока 23 появляется еди- ничный сигнал -через время, которое обусловлено задержкой поступившего сигнала на элементе И 27 узла 26/1 и элемента ИЛИ 25 этого блока 23. На . первом выходе блока 23, на регистре 24 которого установлен код 011, появляется сигнал через время, обусловленное прохождением сигнала, поступающего на первый вход этого блока 23, через элемент И 28 и элемент 29 задержки узла 26, , элемент И 28 и элемент 29 задержки узла 2б2, элемент И 27 узла 265 и элемент ИЛИ 25 данного блока 23, После появления сигнала на первом выходе блока 23, имеющего максимальный приоритет, срабатывает эле- мент И 10 канала 4, к которому подключен наиболее приоритетизш процессор, и через выход 22 этому процессору выдается сигнал, уведомляющий его о том, что ОМ захвачена и он может, передавать по ней информацию. Этот же сигнал переводит триггер 7 рассмат1589277

риваемого канала в единичное состояние, устанавливая нулевой сигнал на шине 2, закрывая (так как шина 2 реат- лизует функцию МОНТАЖНОЕ И) элементы И 9 и 10 и открывая через элементы НЕ 14,элементы И 11 (по второму входу) всех каналов. При этом к моменту выдачи сигнала с пер вого выхода блока 23 канала 4 (не захватившего ОМ), на регистре 24 которого установлен код 011, элемент И 10 этого канала 4 закрыт, а на выходе элемента И 11 который открыт в данном канале 4 по первому входу единичным сигналом с еди ничного выхода триггера 6, по третьему входу - единичным сигналом с выхода элемента НЕ 15, а по четвертому входу - единичным сигналом с выхода

И

32 узлов 3Cfg и

30,

; переноса уста- «.л

навливает триггер первого разряда регистра 24 в нулевое состояние, т,е, временно придает данному 1$аналу 4 мак симальный приоритет, что обеспечива- ет в дальнейшем при захвате ОМ Спосле того, как ее освободит первый процес- сор) исключение задержки сигн;ала (на 10 первом выходе блока 23) на элементах И 28 и элементах 29 задержки узлов 26, и 26,2, задержки. После того, как в третьем канапе на втором выходе бло ка 23 появится единичный сигнал (он 15 появится при установке триггера первого разряда регистра 24 в нулевое состояние), на выходе элемента И-НЕ 16, а следовательно, и на шине 3 уст навливается нулевой сигнал, что исСИ1 HcUIwM V DOl Л: t- ПаХЗЛП . t. л ,/ и j «- -f

элемента И-НЕ 17, на первый вход кото-20 лшючает формирование новых импульсов рого подан нулевой сигнал с выходана выходе формирователя 13 импульU J 1 J I I - /J on njrji.j- , -- - - - -- - - 1

элемента 18 задержки) появляется единичный сигнал (высокий потендиал), по переднему фронту которого запускается формирователь 13 импульсов, вы- даюощй одиночный импульс, поступакг- щий на элемент 18 задержки и на второй вход блока 23 данного канала 4. Этот сигнал через открытые элемент И 32 узла 302 переноса и элемент И 31 узла переноса 30, устанавливает .триггер второго разряда (фиг. 2) регистра 24 в нулевое состояние, т.е. временно придает данному каналу 4 код приоритета 001, После этого в данном, канале 4 с выхода элемента 18 задержки на вход элемента И-НЕ 17 поступает oiuiH04Hbm импульс (единичный сигнал), который приводит к кратковременному (на время действия импульса) появлению на выходе элемента И-НЕ 17 нулевого сигнала, а после того, как на выходе элемента И-НЕ 17 вновь появится единичный сигнал, через элемент И 11 (вновь запускается по переднему фронту единичного сигнала) фop иpoвaтeльlЗ импульсов, который выдает одиночный импульс, поступаю- ясий на элемент 18 задержки и на второй вход блока 23 данного канала 4, Этот сигнал через открытые элементы

25

сов.

фор мул а

изобретени

Многоканальное устройство для при оритетного подключения абонеитов к - общей магистрали по авт.св. № 145887 отличающееся тем, что, с 30 целью повышения быстродействия, в

каждый канал устройства дополнительн введены два элемента И-НЕ и элемент задержки, причем дополнительный втор выход блока задержки соединен О пар вым входом первого элемента И-НЕ вт рой и третий входы которого соединен соответственно с выходом второ.го эле мента НЕ и с единичным выходом второго триггера, выход первого элемента И-Н

40 соединен с дополнительной сигнальной шиной устройства, выход второго формирователя импульсов соединен через элемент задержки с первым входом вто рого элемента И-НЕ, второй г ход и вы

45 ход которого соединены соответственн с дополнительной сигнальной шиной ус тройства и с дополнительным четверга входом четвертого элемента И, едщнич . ный выход первого разряда регистра

50 блока задержки является дополнительным вторым выходом блока задержки.

И

32 узлов 3Cfg и

6

30,

; переноса уста- «.л

навливает триггер первого разряда регистра 24 в нулевое состояние, т,е, временно придает данному 1$аналу 4 максимальный приоритет, что обеспечива- ет в дальнейшем при захвате ОМ Спосле того, как ее освободит первый процес- сор) исключение задержки сигн;ала (на первом выходе блока 23) на элементах И 28 и элементах 29 задержки узлов 26, и 26,2, задержки. После того, как в третьем канапе на втором выходе блока 23 появится единичный сигнал (он 5 появится при установке триггера первого разряда регистра 24 в нулевое состояние), на выходе элемента И-НЕ 16, а следовательно, и на шине 3 устанавливается нулевой сигнал, что исПаХЗЛП . t. л ,/ и j «- -f

0 лшючает формирование новых импульсов на выходе формирователя 13 импульсов.

5

фор мул а

изобретения

Многоканальное устройство для приоритетного подключения абонеитов к - общей магистрали по авт.св. № 1458873, отличающееся тем, что, с 0 целью повышения быстродействия, в

каждый канал устройства дополнительно введены два элемента И-НЕ и элемент задержки, причем дополнительный второй выход блока задержки соединен О пар вым входом первого элемента И-НЕ вто- рой и третий входы которого соединены соответственно с выходом второ.го элемента НЕ и с единичным выходом второго - триггера, выход первого элемента И-НБ

0 соединен с дополнительной сигнальной шиной устройства, выход второго формирователя импульсов соединен через элемент задержки с первым входом второго элемента И-НЕ, второй г ход и вы45 ход которого соединены соответственно с дополнительной сигнальной шиной устройства и с дополнительным четвергам входом четвертого элемента И, едщнич- . ный выход первого разряда регистра

50 блока задержки является дополнительным вторым выходом блока задержки.

I l.J

d УШа

Шмм У|И11И11|||1И I ill г Т iiiJr

3-0

LJ

I

Ф

.J

-/ разряд

Ьй PCfSMff

/

rI

Фиг. 2

Авторы

Даты

1990-08-30—Публикация

1989-01-18—Подача