XI CJ О

со а

Изобретение относится к информационно-измерительной технике и предназначено для измерения квазипиковых, среднеквадратических значений сигналов, а также коэффициентов формы (форм-фактора).

Известна схема измерителя коэффициента формы, содержащая два измерительных преобразователя, один из которых преобразует измеряемое переменное напряжение в постоянное, пропорциональное средневыпрямленному значению измеряемого, другой - в постоянное, пропорциональное среднеквадратическому значению измеряемого. Напряжения с выходов преобразователей поступают на катушки лого- метра, шкала которого проградуирована в единицах коэффициента формы.

Точность преобразования в данном устройстве, построенном по разомкнутой схеме с одновременным преобразованием сигнала в двух независимых каналах, ограничена погрешностями входящих в него элементов. Помимо низкой точности, устройство не обеспечивает работу в автоматическом режиме.

Известна схема измерительного преобразователя интегральных характеристик формы сигналов, содержащая четыре переключателя, пиковый детектор, блок умножения, квадратор, дифференциальный интегратор, блок выборки и хранения, формирователь импульсов, источник опорного напряжения, формирователь модуля, тактовый генератор, причем второй неподвижный контакт первого переключателя соединен с первым входом преобразователя, переключающий контакт первого переключателя соединен с входом пикового детектора, выход которого соединен с первым входом блока умножения, выход последнего соединен с входом квадратора и первым неподвижным контактом четвертого переключателя, второй неподвижный контакт которого соединен с выходом квадратора, переключающий контакт четвертого переключателя соединен с переключающим контактом второго переключателя, два неподвижных контакта которого соединены с двумя соответствующими входами дифференциального интегратора, выход которого соединен с входом блока выборки и хранения, выход последнего является выходом преобразователя и соединен с первым неподвижным контактом первого переключателя, первый неподвижный контакт третьего переключателя соединен с вторым входом преобразователя, второй неподвижный контакт- с выходом источника опорного напряжения, а переключающий контакт с входом формирователя модуля, выход которого соединен с вторым входом блока умножения, управляющие входы первого, второго и третьего переключателей и вход

формирователя импульсов соединены с выходом тактового генератора, а выход формирователя импульсов соединен с управляющим входом блока выборки и хранения.

Указанный преобразователь позволяет в каждом из двух режимов автоматически осуществлять преобразование входных сигналов в напряжение, пропорциональное соответственно коэффициентам амплитуды и

усреднения. Переход с режима на режим осуществляется вручную. При этом систематические погрешности входящих в преобразователь блоков корректируются и не оказывают практического влияния на результат преобразования.

Однако данное устройство не обеспечивает возможности измерения квазипиковых и среднеквадратических значений сигналов, а также коэффициентов формы (формфактора), кроме того, оно не позволяет осуществлять автоматическую смену режимов работы.

Целью изобретения является расширение функциональных возможностей.

Указанная цель достигается введением пяти новых элементов и организацией ряда новых связей. В устройство, содержащее четыре переключателя, блок умножения,

квадратор, дифференциальный интегратор, первый блок выборки и хранения, источник опорного напряжения, формирователь модуля, тактовый генератор и первый формирователь импульсов, где второй

неподвижный контакт первого переключателя соединен с первым входом преобразователя, выход блока умножения соединен с входом квадратора, переключающий контакт четвертого переключателя соединен с

переключающим контактом второго, неподвижные контакты последнего соединены с двумя входами интегратора, выход которого соединен с входом первого блока выборки и хранение, выход которого соединен с первым неподвижным контактом первого переключателя, первый неподвижный контакт третьего переключателя соединен с вторым входом преобразователя, второй неподвижный контакт третьего переключателя соединен с выходом источника опорного напряжения, переключающий контакт третьего переключателя соединен с входом формирователя модуля, выход последнего соединен с вторым входом блока умножения, управляющие входы первого и второго

переключателей и вход первого формирователя импульсов соединены с выходом такто- вого генератора, а выход первого формирователя импульсов соединен с управляющим входом первого блока выборки и хранения, введены пятый переключатель, второй формирователь импульсов, второй блок выборки и хранения, аналоговый делитель напряжений и пересчетный блок, причем вход пересчетного блока соединен с выходом тактового генератора, а выход - с управляющими входами третьего, четвертого и пятого переключателей и входом второго формирователя импульсов, выход последнего соединен с управляющим вхо- дом второго блока выборки и хранения, вход которого соединен с выходом первого блока выборки и хранения, а также с неподвижным контактом пятого переключателя и первым входом аналогового делителя на- пряжений, выход второго блока выборки и хранения соединен с третьим выходом преобразователя и вторым входом аналогового делителя напряжений, выход которого соединен с первым выходом преобразователя, переключающий контакт пятого переключателя соединен с вторым выходом преобразователя, переключающий контакт первого переключателя соединен с первым входом блока умножения, выход которого соединен с первым неподвижным контактом четвертого переключателя, второй неподвижный контакт которого соединен с выходом квадратора.

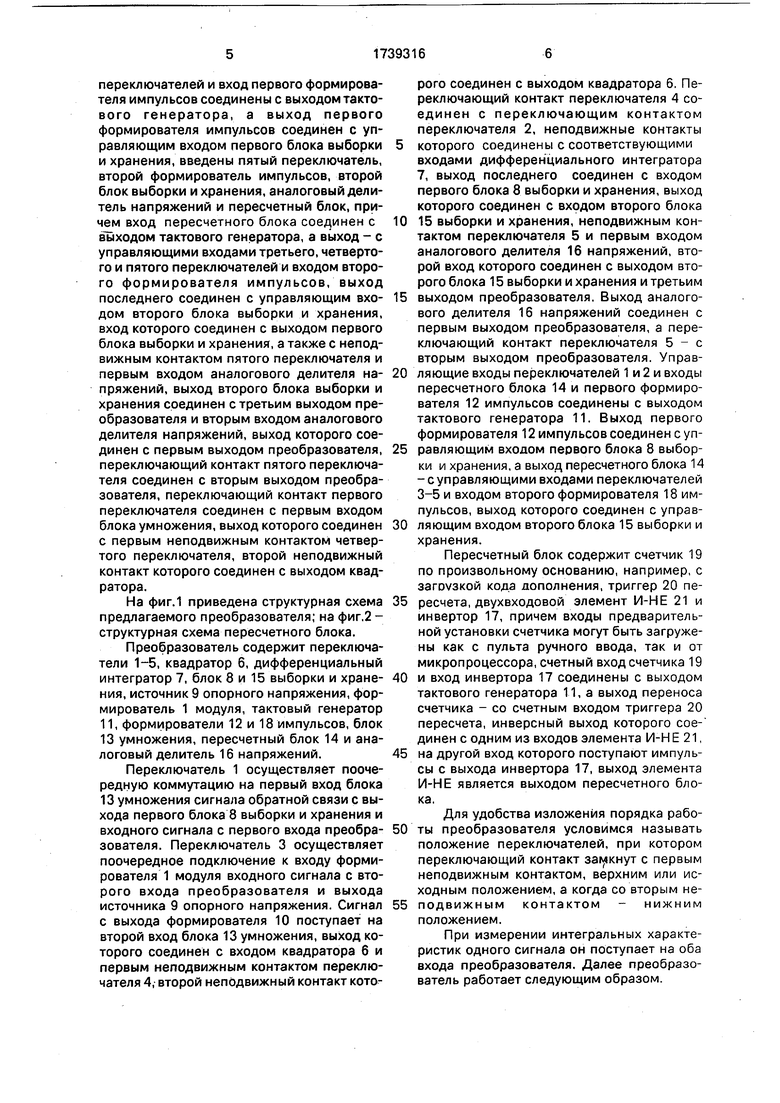

На фиг.1 приведена структурная схема предлагаемого преобразователя; на фиг,2 - структурная схема пересчетного блока.

Преобразователь содержит переключатели 1-5, квадратор б, дифференциальный интегратор 7, блок 8 и 15 выборки и хране- ния, источник 9 опорного напряжения, формирователь 1 модуля, тактовый генератор 11, формирователи 12 и 18 импульсов, блок 13 умножения, пересчетный блок 14 и аналоговый делитель 16 напряжений.

Переключатель 1 осуществляет поочередную коммутацию на первый вход блока 13 умножения сигнала обратной связи с выхода первого блока 8 выборки и хранения и входного сигнала с первого входа преобра- зователя. Переключатель 3 осуществляет поочередное подключение к входу формирователя 1 модуля входного сигнала с второго входа преобразователя и выхода источника 9 опорного напряжения. Сигнал с выхода формирователя 10 поступает на второй вход блока 13 умножения, выход которого соединен с входом квадратора б и первым неподвижным контактом переключателя 4, второй неподвижный контакт которого соединен с выходом квадратора 6. Переключающий контакт переключателя 4 соединен с переключающим контактом переключателя 2, неподвижные контакты которого соединены с соответствующими входами дифференциального интегратора 7, выход последнего соединен с входом первого блока 8 выборки и хранения,выход которого соединен с входом второго блока 15 выборки и хранения, неподвижным контактом переключателя 5 и первым входом аналогового делителя 16 напряжений, второй вход которого соединен с выходом второго блока 15 выборки и хранения и третьим выходом преобразователя. Выход аналогового делителя 16 напряжений соединен с первым выходом преобразователя, а переключающий контакт переключателя 5 - с вторым выходом преобразователя. Управляющие входы переключателей 1 и 2 и входы пересчетного блока 14 и первого формирователя 12 импульсов соединены с выходом тактового генератора 11. Выход первого формирователя 12 импульсов соединен с управляющим входом первого блока 8 выборки и хранения, а выход пересчетного блока 14 -суправляющими входами переключателей 3-5 и входом второго формирователя 18 импульсов, выход которого соединен с управляющим входом второго блока 15 выборки и хранения.

Пересчетный блок содержит счетчик 19 по произвольному основанию, например, с ЗЗГОУЗКОЙ кода дополнения, триггер 20 пересчета, двухвходовой элемент И-НЕ 21 и инвертор 17, причем входы предварительной установки счетчика могут быть загружены как с пульта ручного ввода, так и от микропроцессора, счетный вход счетчика 19 и вход инвертора 17 соединены с выходом тактового генератора 11, а выход переноса счетчика - со счетным входом триггера 20 пересчета, инверсный выход которого соединен с одним из входов элемента И-Н Е 21, на другой вход которого поступают импульсы с выхода инвертора 17, выход элемента И-НЕ является выходом пересчетного блока.

Для удобства изложения порядка работы преобразователя условимся называть положение переключателей, при котором переключающий контакт замкнут с первым неподвижным контактом, верхним или исходным положением, а когда со вторым неподвижным контактом - нижним положением.

При измерении интегральных характеристик одного сигнала он поступает на оба входа преобразователя. Далее преобразователь работает следующим образом.

Перед началом работы по тракту параллельной загрузки пересчетный блок 14 загружается кодом дополнения требуемого числа тактов, который в процессе работы перезаписывается автоматически.

Режим измерения квазипиковых значений.

В первом такте переключатели 1-4 переводятся в нижнее положение. При этом переключатель 1 подключает на первый вход блока 13 умножения напряжение входного сигнала U(t), переключатель 3 подключает выход источника 9 опорного напряжения Uon к входу формирователя 10 модуля и далее на второй вход блока 13 умножения. На выходе последнего появляется напряжение

UMyi U(t)Uon(1)

которое поступает на вход квадратора 6. На выходе последнего образуется напряжение

(t)(2)

Это напряжение через переключатели 4 и 2 поступает на один из входов дифференци- ального интегратора 7 (предположим, на ). Производится интегрирование поступившего напряжения в течение длительности импульса тактового генератора 11, и напряжение на выходе интегратора 7 стано- вится равным

иИ1 i / U(t) dt

(3)

где т - постоянная времени дифференциального интегратора 7;

Т - длительность импульсов тактового генератора 11.

По спаду тактового импульса схемы формирователей 12 и 18 импульсов выдают короткие импульсы на управляющие входы блоков 8 и 15 выборки и хранения и производится запись напряжения с выхода дифференциального интегратора 7.

Во втором такте (в паузе между импульсами тактового генератора) переключатели 1-4 находятся в исходном положении (верхнем). Переключатель 1 подключает на первый вход блока 13 умножения напряжение с выхода блока 8 выборки и хранения, переключатель 3 подключает к входу формирователя 10 модуля напряжение, поступающее на второй вход преобразователя (в рассматриваемом случае U(t). На выходе блока 13 умножения появляется напряжение

UMy2 UMl|U(t)|,(4)

которое через переключатели 4 и 2 поступает на второй вход интегратора 7 (вход -).

Производится интегрирование поступившего напряжения в течение времени Т, в результате чего выходное напряжение дифференциального интегратора 7 в конце второго такта оказывается равным

UM2 / (t) - UMJ U(t)|}. dt. (5) о

В третьем такте повторяются действия, осуществляемые в первом такте. В результате на выходе дифференциального интегратора 7 появляется напряжение

ТТ

ииз -1 / U(t) dt - f uJu(t| dt,

оо

(6)

Далее описанная процедура может быть продолжена неограниченное количество раз. При этом n-е выходное напряжение дифференциального интегратора 7 определяется из выражения

|/ U(t) if Uni|U(t)|dt, оо

(7)

Учитывая, что в каждом цикле интегрирования величины Uon и UMn постоянны, получим

иип и

оп

|/U2(t)dt

о

T/iU(t)fdt

1 n

(8)

0

5

0

5

Из (8) следует, что Dun является оценкой квазипикового значения сигнала. При этом, также как и в известном устройстве, систематические погрешности используемых блоков корректируются, а точность ограничивается практически лишь точностью источника 9 опорного напряжения. Квазипиковые значения сигналов поступают на выход 3 преобразователя и одновременно на второй вход аналогового делителя 16 напряжений.

Режим измерения среднеквадратиче- ских значений.

После выполнения заданного количества тактов пересчетный блок 14 блокирует прохождение импульсов тактового генератора 11 и формирует на своем выходе сигнал высокого уровня. При этом переключатели 3-5 переводятся в нижнее положение и остаются в нем до окончания текущего цикла измерений (количество тактов в этом цикле такое же, как и в предыдущем).

В первом такте переключатели 1 и 2 переводятся в нижнее положение. По аналогии с предыдущим режимом напряжение на выходе блока 13 умножения равно

UMyi U(t)Uon .(9)

Это напряжение поступает на вход квадратора 6, на выходе которого образуется напряжение

(t)Uonf(Ю)

Далее через переключатели 4 и 2 оно поступает на один из входов дифференциального интегратора 7 (предположим, на вход +). Производится интегрирование поступивше- го напряжения в течение длительности импульса тактового генератора 11, и напряжение на выходе интегратора 7 становится равным

11и1 | / U(t)Uonf dt(11)

о

Напряжение (11) по сигналу формирователя 12 импульсов переписывается в блок 8 выборки и хранения.

Во втором такте переключатели 1 и 2 возвращаются в исходное состояние и на выходе блока 13 умножения появляется напряжение

UMy2 UMlUon,(12)

которое поступает на вход квадратора 6. На вых оде последнего появляется напряжение

UKB2 (11и1 Uon)2,(13)

которое через переключатели 4 и 2 поступа- ет на второй вход () дифференциального интегратора 7. В конце второго такта (по истечении времени Т) выходное напряжение дифференциального интегратора 7 оказывается равным

UM2 |/ (t)Uonf-(UMiUon)} dt.

(14)

В третьем такте повторяются действия, осуществляемые в первом такте. В результате на выходе дифференциального интегратора 7 появляется напряжение

ии3 | / UMUon 2 dt-j } -

(UniUon)2 dt ,(15)

Выходное напряжение интегратора 7 после п тактов определяется из выражения

тт

i / U(t)Uonf dt / (UnnUon)2 dt.

оо

(16)

Из (16) с учетом сделанных для предыдущего режима замечаний получим

U2(t)dt

(17)

0

5

0

j.

5

0

0

5

Как следует из (17) 11ип является оценкой среднеквадратического значения сигнала U(t), при этом наряду с систематическими погрешностями используемых блоков устраняется влияние источника 9 опорного напряжения на точность преобразования. Среднеквадратические значения сигналов U(t) через переключатель 5 поступают на второй выход преобразователя и одновременно на первый вход аналогового делителя 16 напряжений.

Режим измерения коэффициентов формы (форм-фактора).

Выполнение режима измерения коэффициента формы, определяемого из выраже ния

Кф (,8)

где UKn - квазипиковое значение сигнала U(t);

UCK - среднеквадратическое значение сикнала U(t),

начинается одновременно с выполнением режима измерения среднеквадратического значения сигнала U(t). К этому времени на одном из входов аналогового делителя 16 напряжений имеется значение делимого икп. По мере выполнения итерационной процедуры формирования значения делителя UCK, поступающего на второй вход аналогового делителя 16 напряжений, результат деления все больше приближается к искомому значению Кф. После п тактов измерения UCK выходной сигнал идп аналогового делителя 16 напряжений является оценкой коэффициента формы Кф сигнала U(t). Кроме отмеченных интегральных характеристик (икп, ). предлагаемый преобразователь позволяет измерять функционалы более общего вида. Так, при подаче на первый вход сигнала Ui(t), а на второй вход сигнала Ua(t) на основании (8), (17), (18) получим: для первого режима

1

Y/U2(t)dt

, 09)

Y / IU2(t)ldt

для второго режима

Ui2(t)dt, о

для третьего режима

(20)

i}tf(t)dt

о

1 / IU2(t)ldt

(21)

Т

Известно, что при производстве интегральных микросхем необходим контроль токовых шумов резисторов как полупроводниковых, так и изготовленных по тонкопленочной технологии. Для характеристики шумов резисторов используют понятие коэффициента шума Кш. Согласно ГОСТ коэффициент шума резисторов Кш измеряется как отношение среднеквадратиче- ского значения напряжения токового шума к постоянному напряжению U-, приложенному к резистору.

В настоящее время не имеется устройств, позволяющих в автоматическом режиме измерять значения Кш. В связи с этим представляет практический интерес использование предлагаемого преобразователя в задаче измерения Кш. Так, при подключении к первому входу напряжения токового шума Um испытуемого резистора, а к второму входу - постоянного напряжения U-, подаваемого на него, на основании (8), (17) и (18) в третьем режиме получим искомую оценку

Ji / UJLdt

I, ,, 24 О

идп UonП

(22)

Очевидно, что во всех рассмотренных режимах использование итерационной коррекции систематических погрешностей блоков обеспечивает предлагаемому преобразователю высокую точность преобразования. Функциональные возможности предлагаемого преобразователя существенно расширены (получено три новых режима работы) введением переключателя 5, пересчетного блока 14, второго блока 15 выборки и хранения, второго формирователя 18 импульсов и аналогового делителя 16 напряжения. Для измерения периодических сигналов в диапазоне частот в схеме тактового генератора 11 предусмотрена возможность изменения длительности и периода следования импульсов.

Формула изобретения 1. Измерительный преобразователь интегральных характеристик сигналов, содержащий четыре переключателя, блок умножения, квадратор, дифференциальный интегратор, первый блок выборки и

хранения, источник опорного напряжения, формирователь модуля, тактовый генератор и первый формирователь импульсов, при этом второй неподвижный контакт первого

переключателя соединен с первым входом преобразователя, выход блока умножения соединен с входом квадратора, переключающий контакт четвертого переключателя соединен с переключающим контактом

второго, неподвижные контакты последнего соединены с двумя входами интегратора, выход которого соединен с входом первого блока выборки и хранения, выход которого соединен с первым неподвижным контактом первого переключателя, первый неподвижный контакт третьего переключателя соединен с вторым входом преобразователя, второй неподвижный контакт третьего переключателя соединен с выходом источника опорного напряжения, переключающий контакт третьего переключателя соединен с входом формирователя модуля, выход которого соединен с вторым входом блока умножения, управляющие входы первого и второго переключателей и вход первого формирователя импульсов соединены с выходом тактового генератора, а выход первого формирователя импульсов соединен с управляющим входом первого блока

выборки и хранения, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены пятый переключатель, второй формирователь импульсов, второй блок выборки и хранения,

делитель напряжений и пересчетный блок, причем вход последнего соединен с выходом тактового генератора, а выход - с управляющими входами третьего, четвертого и пятого переключателей и входом второго

формирователя импульсов, выход последнего соединен с управляющим входом второго блока выборки и хранения, вход которого соединен с выходом первого блока выборки и хранения, а также с неподвижным контактом пятого переключателя и первым входом делителя напряжений, выход второго блока выборки и хранения соединен с третьим выходом преобразователя и с вторым ЕХОДОМ делителя напряжений, выход которого соединен с первым выходом

преобразователя, переключающий контакт

ч пятого переключателя соединен с вторым

выходом преобразователя, переключающий

контакт первого переключателя соединен с

первым входом блока умножения, выход которого соединен с первым неподвижным контактом четвертого переключателя, второй неподвижный контакт которого соединен с выходом квадратора.

2. Преобразователь по п.1, о т л и ч а ю- щ и и с я тем, что пересчетный блок содержит счетчик по произвольному основанию, например, с загрузкой кода дополнения, триггер пересчета, двухвходовой элемент И-НЕ и инвертор, счетный вход счетчика и вход инвертора соединены с выходом тактового генератора, а выход переноса счетчика - со счетным входом триггера пересчета, инверсный выход которого соединен с одним из входов элемента И-НЕ, на другой вход которого поступают импульсы с выхода инвертора, выход элемента И-НЕ является выходом пересчетного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительный преобразователь отношений двух сигналов | 1990 |

|

SU1734029A1 |

| Логометрический измерительный преобразователь | 1986 |

|

SU1396074A1 |

| Способ измерения среднеквадратического значения напряжения переменного тока и устройство для его осуществления | 1985 |

|

SU1357857A1 |

| Цифровой омметр | 1983 |

|

SU1129553A2 |

| Цифровой измеритель напряжения | 1984 |

|

SU1239606A1 |

| Преобразователь величины мощности и действующего значения напряжения в цифровой код | 1985 |

|

SU1330572A1 |

| Цифровой измеритель мощности | 1983 |

|

SU1155954A1 |

| Цифровой измеритель мощности | 1979 |

|

SU828102A1 |

| Устройство для моделирования функций с помощью частных сумм сигналов Уолша | 1990 |

|

SU1741121A2 |

| Квадратор | 1979 |

|

SU860088A1 |

Изобретение относится к информационно-измерительной технике и может быть ис- пользовано для преобразования электрического сигнала в постоянное напряжение, пропорциональное его квазипиковому, среднеквадритическому значению, а также коэффициенту формы. Измерительный преобразователь содержит пять переключателей 1, 2, 3, 4, 5, квадратор 6, дифференциальный интегратор 7, блоки 8, 15 выборки-хранения, источник 9 опорного напряжения, формирователь 10 модуля, тактовый генератор 11, формирователи 12, 18 импульсов, блок 13 умножения, пересчетный блок 14 и аналоговый делитель 16 напряжения. 1 з.п. ф-лы, 2 ил. сл С

в выхода т г(11)

Код 2-К

Уст.

1 Выход

21

2Q

Q

Фиг. 2

| Волгин Л.И | |||

| Измерительные преобразователи переменного напряжения в постоянное | |||

| - М.: Советское радио, 1977, с.5-6 | |||

| Рудницкий Б.П | |||

| и др | |||

| Измерители нестабильности напряжений | |||

| - М.: Советское радио, 1975, с.130 | |||

| Логометрический измерительный преобразователь | 1989 |

|

SU1626204A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-06-07—Публикация

1990-05-07—Подача