(54) КВАДРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| Двухтактный измеритель энергии одиночных импульсов | 1990 |

|

SU1721520A1 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

| Интегратор | 1985 |

|

SU1298775A1 |

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

| Функциональный аналого-цифровой преобразователь | 1986 |

|

SU1310855A1 |

| Аналоговый перемножитель | 1984 |

|

SU1166143A1 |

| Устройство для вычисления алгебраических выражений | 1979 |

|

SU864298A1 |

| Дискретный интегратор | 1975 |

|

SU705468A1 |

Изобретение относится к аналоговой и аналого-цифровой вычислительной технике. Известен квадратор, содержащий интегратор и генератор линейно изменяющегося напряжения 1. Его недостаток - низкая точность преобразования, так как- в функцию преобразования устройства входит постоянная времени генератора линейно изменякяцегося напряжения. Наиболее близок к предлагаемому квадратор, содержащий два интегратора, четыре ключа, источник опорного напряжения, два нуль-органа, узел управления, формирователь временного интервала, первый вход первого интег ратора соединен с выходом первого ключа, а первый вход второго интегратора соединен с выходом второго ключа, входы первого и второго ключей связаны с входной шиной устройства, вторые входы первого и второго интеграторов соединены соответственн с выходом третьего и четвертого ключей, входы которых связаны с выходом источника опорного напряжения, выход первого интегратора подключен к выходу- первого нуль-органа, а выход второго интеграт.ора подключен к выходу второго нуль-органа, выходы обоих нуль-органов соединены с соответствующими входами узла управления, выходы узла управления связаны с выходом формирователя временного интервала и управляющими входами ключей, выход фор дарователя временного интервала соединен с рыходной шиной устройства 21. Недостатками такого квадратора являются низкая точность и низкое быстродействие. Низкое быстродействие обусловлено тем, что цикл преобразования состоит из трех тактов. Низкая точность преобразования - т&л, что э указаннем устройстве осуществляется перемножение интегральных значений входного сигнала, взятых в разные моменты времени. В первом такте интегрируется напряжение вторьо интегратором в течение времени Т , и только по окончании этого .такта происходит интегрирование входного напряжения первым интегратором в течение интервала времени Т. При преобразовании непостоянных напряжений это обстоятельство приводит к иашичию динамической погрешности, так как

а время первого такта входное напряение может измениться.

Цель изобретения - повышение точости и быстродействия квадратора.

Поставленная цель достигается тем,. то квадратор, содержащий интегратор, зел управления, источник опорного апряжения, нуль-орган, вход котороо соединен с выходом интегратора, а ыход подключен к первому входу узла правления, формирователь временного нтервала, вход которого соединен с первым выходом узла управления,а выод является выходом квадратора,дополнительно содержит два усилителя постоянного тока, два элемента с управляемой проводимостью, два переключателя, два масштабных резистора, аналоговое запоминающее устройство и генератор тактовых импульсов, выход которого соединен со вторым вкодом для управления, первый информационный вход первого переключателя соединен со входом аналогового запоминающего устройства и является входом квадратора, второй информационный вход первого переключателя соединен с выходом источника опорного напряжения, с первым информационным входом второго переключателя и выходом первого элемента с управляемой проводимостью, второй информационный . вход второго переключателя соединен с выходом аналогового запоминающего устройства, выход первого переключателя через первый масштабный резистор, а выход второго переключателя через второй элемент с управляемой проводимостью соединены с входом первого усилителя постоянного тока, выход которого соединен с управляющими входами первого и второго элементов с управляемой проводимостью, первого элемента с управляемой проводимостью соединен с входом второго усилителя постоянного тока, между входом и выходом которого включен второй масштабный резистор, выход второго усилителя постоянного тока соединен с входом интегратора, управляющие входы переключателей и управляющий вход аналогового запоминающего устройства подключены ко второму выходу узла управления.

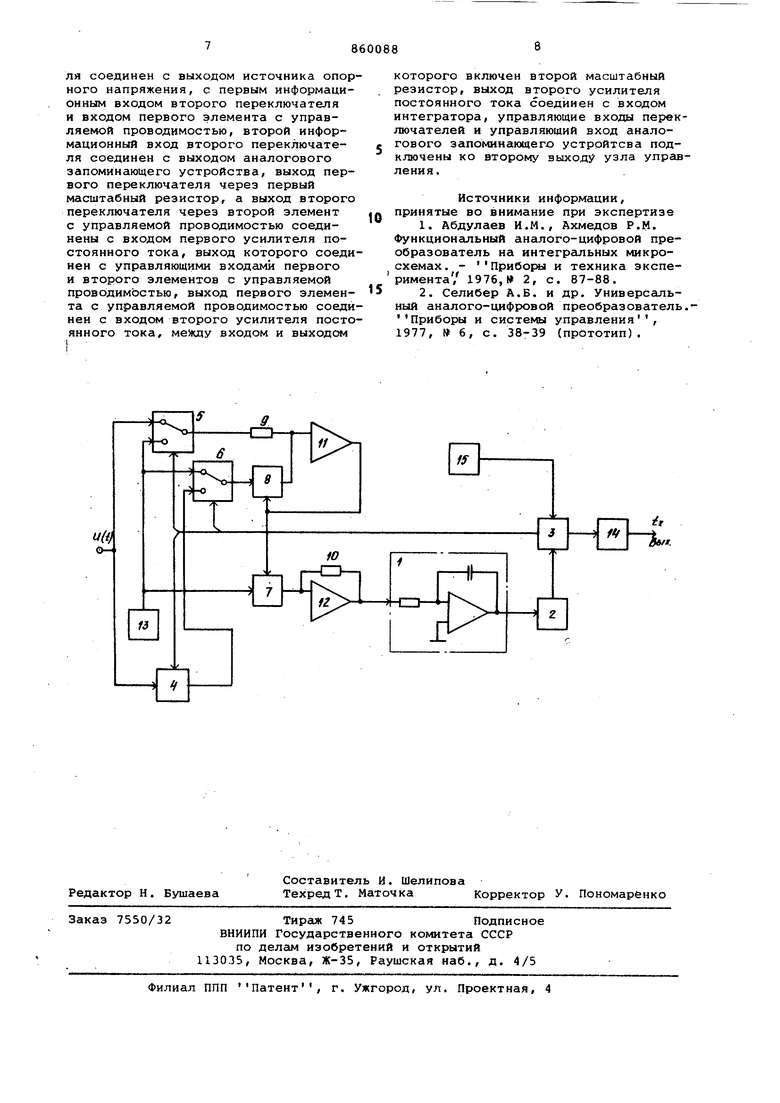

На Чертеже приведена блок-схема квадратора.

Квадратор содержит интегратор 1, нульЧорган 2, узел 3 управления, аналЭговое запоминающее устройство 4, первый и второй переключатели 5 и 6, первый и второй элементы 7 и 8 управляемой проводимостью,первый и второй масштабные резисторы 9 и 10 первый и второй усилители 11 и 12 постоянного тока,источник 13 второго напряжения , формирователь 14 временного интервала, генератор 15 тактовых импульсов.

Квадратор работает следующим о-бразом.

В первом такте по команде с узла управления переключатели 5 и 6 устанавливаются в верхнее положение. Длительность первого такта Т/ задается узлом 3 управления.

В течение первого такта интегратор 1 заряжается выходным напряжением и (t) усилителя 12, которое пропорционально входному напряжению U)((t). Для первого усилителя, охваченного отрицательной обратной связь через элемент 8, можно записать уравнение

u (fc)

Vo-°

U.

откуда

v-, G

- значение прюводимости эле-fмента 8; R - значение сопротивления резистора ;

V - напряжение источника опорного напряжения 13. Выходное напряжение усилителя 12 определяют из уравнения

.

откуда

U jC-tl -NoQa a,

где Rg значение сопротивления резистора 10;

G - значение проводимости второго элемента 7.

В общем случае неидентичность характеристик элементов 7 и 8 с управляемой проводимостью приводит к тсжу что проводимости Си G, не равны между собой, т.е.

Gii-aQ, дг)

где а - коэффициент, учитывающий

неидентичиость характеристик элементов 7 и 8. С учетом (1) и (3) уравнение (2)

можно записать.в виде

U,U.- Н% (4,

За время первого такта Т., интегратор 1 заряжается до напряжения

,, (.,

где - постоянная времени интегратора 1 . f Одновременно в первом такте проис ходит (по команде с узла 3 управления) запоминание инвертированного мгновенного значения входного напряжения квадратора в аналоговом запоMHHcUomeM устройстве 4. Во втором такте по команде с узла 3 управлени переключатели 5 и 6 переводятся в нижнее положение, при этом на выход второго переключателя 6.подключается выходное напряжение аналогового запоминающего устройства 4.В течени второгчэ такта интегратор 1 разряжае ся до нуля выходным напряжением усилителя 12, которое обратно пропор ционально мгновенному значению входного напряжения, запомненного в аналоговом эапсминающем устройстве 4 в первом такте. Момент равенства нулю выходного напряжения интегратора 1 фиксируется нуль-оргёшом 2, который выдает |сигнал на узел 3 управления. На вы|Ходе формирователя 14 временного интервала с помощью узла 3 управления формируется выходной интервал времени, длительность которого равна длительности второго такта работы квгщратораНаходят выражение для выходного напряжения усилителя 12 и(t), коtoptSM разряжается интегратор 1 во втором такте. Пренебрегая входным током усилителя 11, можно записать где д - выходное напряжение анал гового запоминающего уст ройства 4. С учетом того, что --V, по лучают -. . (6) Уравнение для входной цепи усилите 12 имеет вид v...Mii-.., . откуда с учетом (3) и (6) получгиот JaW- o () Во время второго такта напряжени на выходе интегратора 1 изменяется в соответствии с выражением ) Приравнивая 7ц-2.нулю и подставл яя значения Ущ из (5) и U,(t) из (7), получают ; . 1 NuRVl-. откуда ,--К, U) где К - постоянный коэффициент. Как видно из выражения (8) , неидентичность характеристик элементов 7 и 8 с управляемой проводимостью не приводит к дополнительным погрешностям, так как результат преобразования не зависит от коэффициента а, характеризующего их соотношения.Кроме того, как видно из (8), значение выходной величины квадратора не зависит от отношения резисторов 9 и 10 и элементов 7 и 8. Предлагаемый квадратор имеет более высокое быстродействие, чем иэвестный 2, поскольку цикл преобразования состоит всего из двух тактов работы интегратора, в то время как цикл работы известного состоит из трех аналогичных тактов. Кроме того, предлагаемый квадратор обладает более высокой точностью..Последнее объясняется тем, что в нем осуществляется перемножение значений входного напряжения U(t) (квадратирование), взятых в течение одногои того же интервала времени - первого такта преобразования, следовательно, отсутствует, динамическая погрешность, Свойственная известному квадратору. Формула изобретения Квадратор,содержащий интегратор, узел управления, источник опорного напряжения, нуль-орган, вход которого соединен с выходом интегратора, а выход подключен к первому входу узла управления, формирователь времен ного интервала, вход которого соединен с первым выходом узла управления, а выход является выходом квадратора, отличающийся тем, что, с целью псшьииения точности и быстродействия, он содержит два усилителя постоянного тока, два элемента с управляемой проводимостью, два переключателя, два масштабных резистора, ансшоговое запоминающее устройство и генератор тактовых импульсов, выход которого Соединен со вторым входом узла управления, первый информационный вход первого переключателя соединен со входом аналогового запомингиощего устройства и является входом квадратора, второй информационный вход первого переключателя соединен с выходом источника опорного напряжения, с первым информационным входом второго переключателя и входом первого элемента с управляемой проводимостью, второй информационный вход второго переключателя соединен с выходом аналогового запоминающего устройства, выход первого переключателя через первый масштабный резистор, а выход второго переключателя через второй элемент с управляемой проводимостью соединены с входом первого усилителя постоянного тока, выход которого соединен с управляющими входами первого и второго элементов с управляемой проводимостью, выход первого элемента с управляемой проводимостью соединен с входом второго усилителя постоянного тока, между входом и выходс 1

которого включен второй масштабный резистор, выход второго усилителя постоянного тока соединен с входом интегратора, управляющие входы переключателей и управляющий вход аналогового запоминающего устройтсва подключены ко второму выходу узла управления.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-08-30—Публикация

1979-07-13—Подача