v fe

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения механических параметров коммутирующих элементов | 1984 |

|

SU1215094A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 1996 |

|

RU2106679C1 |

| Устройство для контроля степени заряженности аккумуляторной батареи | 1985 |

|

SU1377937A1 |

| РЕЛЕ НАПРАВЛЕНИЯ МОЩНОСТИ | 2002 |

|

RU2205466C1 |

| Устройство для испытания электрической прочности изоляции | 1988 |

|

SU1647476A1 |

| Устройство для измерения параметров тиристоров | 1984 |

|

SU1187113A1 |

| Устройство для неразрушающего контроля прочности изоляции электрических цепей | 1990 |

|

SU1780053A1 |

| Устройство для управления температурным режимом печей графитации | 1983 |

|

SU1211710A1 |

| Устройство для программного регулирования температры | 1986 |

|

SU1374194A1 |

| Устройство для управления фотоколориметрическим газоанализатором | 1982 |

|

SU1092468A1 |

Изобретение относится к контрольно- измерительной технике и может быть использовано для испытания электрической прочности изоляции электротехнических и электронных изделий, а также для их классификации. Сущность изобретения: устройство содержит генератор 1. блок 2 управления, делитель 3 частоты, элементы И 4, 5, реверсивный счетчик 6, задатчик 7 начального кода, управляемый источник 8 испытательного напряжения, преобразователь 9 кода, дешифраторы 10, 11, элемент ИЛИ 12, инвертор 13, датчик 15 предельного кода, блок 16 фиксации результатов, исполнительный орган 17. 3 з.п. ф-лы, 4 ил.

л

о

OJ 00

Изобретение относится к контрольно- измерительной технике и может быть использовано для испытания электрической прочности изоляции электротехнических и электронных изделий, а также для их клас- сификации.

Цель изобретения - повышение надежности достоверности исследования изделий.

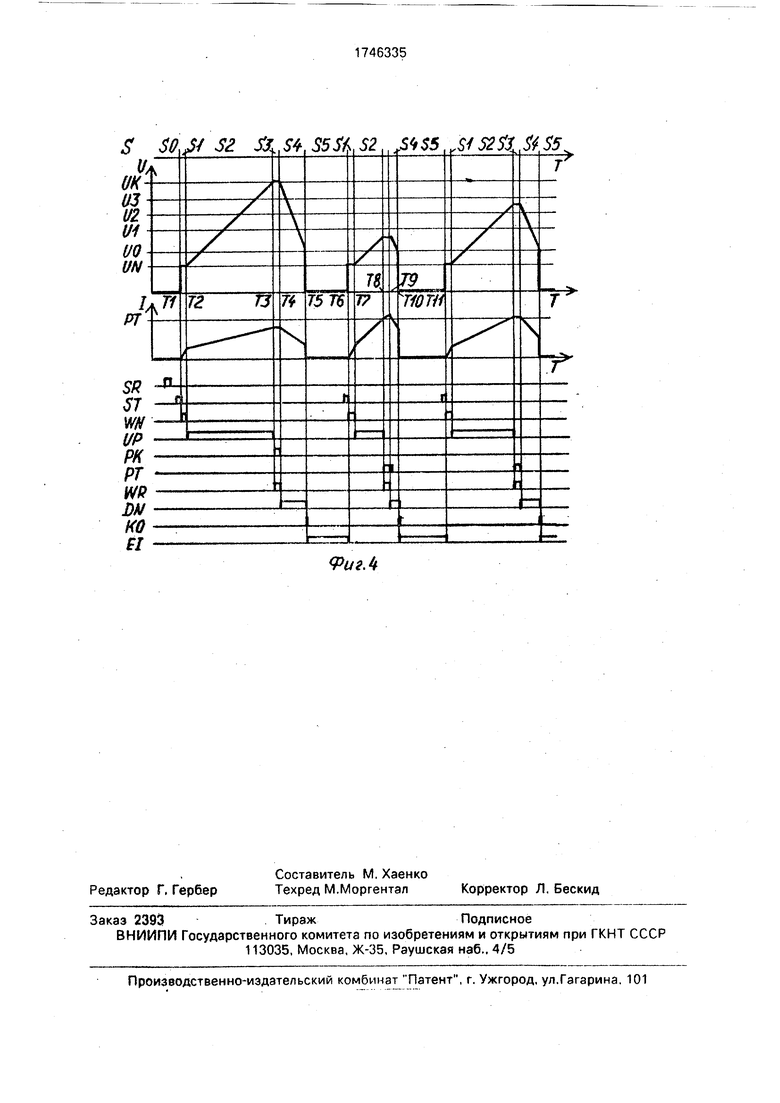

На фиг. 1 представлена структурная схема испытателя прочности изоляции; на фиг. 2 - схема одного из возможных вариантов выполнения блока управления; на фиг. 3 - его граф; на фиг, 4 - временная диаграмма работы устройства.

Устройство содержит генератор 1 тактовых импульсов, выход которого подключен к синхровходу блока 2 управления и к входу делителя 3 частоты, выходы которого подключены к входам элементов И 4 и 5, выходы которых подключены соответственно к инк- рементирующему и декрементирующему входам реверсивного счетчика 6. Его информационный параллельный вход подключен к задатчику, начального кода, а вход запи- си кода - к третьему выходу блока 2 управления, Параллельный выход реверсивного счетчика соединен с входами управляемого источника 8 испытательного напряжения, преобразователя 9 кодов, дешифратора 10 предельного кода и дешифратора 11 кода отключения, выходом подключенного к входу сброса реверсивного счетчика 6 и к одному из входов блока 2 управления. Выход дешифратора 10 предельного кода со- единен с одним из входов блока 2 управления и с одним из входов элемента ИЛИ 12, выходом связанного через инвертор 13 с одним из входов элемента И 4. Выход управляемого источника 8 испыта- тельного напряжения через исследуемое изделие 14 связан с датчиком 15 предельного тока, выход которого подключен к другому входу элемента ИЛИ 12 и к одному из входов блока 2 управления. Параллельный выход преобразователя 9 кодов связан через блок 16 фиксации результатов с исполнительным органом 17. Входы разрешения двух последних подключены к выходам блока 2 управления, входы пуска и остановки которого соединены соответственно с шиной 18 пуска и с шиной 19 останова.

Блок 2 управления выполнен в виде цифрового автомата (фиг.2) Мура, содержащего шифратор 20 состояний, блок 21 памяти переменных состояний и .программируемую логическую матрицу 22. Цифровой автомат 2 полностью и однозначно определен совокупностью входного и выходного векторов (фиг. 1 и 2) и графом (фиг.

3), отображающим как совокупность всех состояний автомата, так и все переходы. Кроме того, совокупность всех состояний, входного и выходного векторов представлены также и на временной диаграмме (фиг. 4) работы устройства с изображением функциональных меток всех сигналов.

Делитель 3 частоты может быть выполнен в виде суммирующего счетчика с выходами от двух разрядов или в виде двух независимых счетчиков с объединенными счетными входами. Задатчик 7 начального кода может быть выполнен в виде совокупности переключателей для набора начального кода.

Управляемый источник 8 испытательного напряжения представляет из себя преобразователь код-напряжение с высоким выходным напряжением. Преобразователь 9 кодов представляет из себя блок постоянной памяти, адресный вход которого подключен к выходу реверсивного счетчика, а выход данных подключен к входу блока 16 фиксации результатов, выполненного в виде параллельного регистра. Исполнительный орган 17 в простейшем случае представляет из себя индикатор с входом разрешения индикации, например совокупность светодиодов, подключенных к шинному формирователю, вход выбора кристалла которого соединен с выходом блока 2 управления.

Устройство работает следующим образом.

При включении устройства сигнал системного сброса, поступающий по шине 19, устанавливает блок 21 памяти состояний (параллельный регистр) блока 2 управления в исходное нулевое состояние (фиг. 1 и 4), в котором не вырабатывается ни один выходной сигнал. Одновременно реверсивный счетчик 6 также сбрасывается в нулевое состояние, благодаря чему на выходе управляемого источника 8 испытательного напряжения нулевой уровень испытательного напряжения, что необходимо для подключения очередного исследуемого изделия 14. На исполнительный орган 17 также поступает запрещающий потенциал. Элементы И 4 и 5 запрещают проход импульсов на инкрементирующий и декрементирующий входы. Запрещена также и запись кода с задатчика 7 начального кода.

После подключения к выходу управляемого источника 8 испытательного напряжения очередного подлежащего исследованию изделия 14 последовательно с датчиком предельного тока устройство готово к работе.

Поступающий по шине 18 запускающий импульс в момент времени Т1 переводит блок 2 управления из нулевого состояния в первое состояние. В этом состоянии блок управления находится только один такт и вырабатывает при этом сигнал WN, по которому в реверсивный счетчик 6 записывается из задатчика 7 начального кода код, пропорциональный начальному напряжению, при котором не происходит пробой изоляции исследуемого изделия. Напряжение на исследуемом изделии скачком возрастает до начального уровня UN.

По окончании такта блок 2 управления переходит во второе состояние (момент Т2). При этом сигнал записи начального кода заканчивается и появляется сигнал UP повышения испытательного напряжения. Этот сигнал поступает на один из входов элемента И 4, разрешая тем самым прохождение импульсов пониженной частоты с генератора 1 через делитель 3 частоты. Эта частота устанавливается выбором коэффициента деления таким образом, чтобы обеспечить требуемую скорость повышения испытательного напряжения. По мере поступления импульсов инкрементируется реверсивный счетчик б, который увеличением выходного кода увеличивает и испытательное напряжение на выходе управляемого источника 8 испытательного напряжения. Постепенно повышающееся напряжение прикладывается к исследуемому изделию 14. По мере повышения напряжения растет и ток утечки через изоляцию изделия. Датчик 15 предельного тока анализирует этот ток и пока ток не достигает предельного уровня имеет низкий потенциал на своем выходе. Одновременное этим дешифратор 10 предельного кода выявляет код, соответствующий предельно допустимому для данного типа испытательному напряжению. При этом не имеет значения погрешность линейности управления источника 8 испытательного напряжения, поскольку дешифратор 10 может быть настроен по фактическому напряжению на выходе источника 8, представляющего собой преобразователь кода в напряжение. Если предполагается исследовать различные типы изделий, то удобно выполнить дешифратор 10 не в виде комбинационной схемы, а в виде постоянного блока памяти (например, в виде репрограммируемой памяти с ультрафиолетовым стиранием), к адресному входу которого подключен задатчик предельного допустимого кода в виде переключателей.

Таким образом, начиная с момента 12 по мере роста испытательного напряжения и увеличения вследствие этого тока через

изделие, одновременно анализируется до- снижение ими предельных значений. Как только любой, хотя бы один из этих параметров, достигает своего предельного значе- 5 ния, блок 2 управления переходит в третье состояние (фиг. 3). На фиг. 4 показано, что, начиная с момента времени Т2, при росте испытательного напряжения до его предельного значения ток не достигает пре0 дельного уровня, что характерно для изделий, относящихся к высшей классификационной группе по величине прочности электрической изоляции. Для таких изделий проверка фактического напряжения пробоя

5 не должна производиться, так как это значение больше предельно допустимого уровня. Таким образом, при достижении в момент ТЗ предельного значения напряжения сигнал предельного кода РК с выхода, дешиф0 ратора 10 предельного кода переводит блок 2 управления в третье состояние.

В третьем состоянии испытательное напряжение перестает повышаться и вырабатывается в течение одного такта только

5 один управляющий сигнал WR записи кода с выхода реверсивного счетчика 6 в блок 16 фиксации результата через преобразователь 9 кодов. Этот преобразователь представляет из себя постоянную память, в

0 которой в соответствии с классификационными группами хранятся коды номеров этих классификационных групп. В частности при кодах, соответствующих напряжению до U1 (фиг.4), в этой памяти по всем адресам хра5 нится код блока, при кодах напряжений от U1 до U2 хранится код первой группы с наименьшей прочностью изоляции, при кодах напряжений от U2 до U3 - код второй группы и т.д. По адресам свыше предельно0 го кода РК хранится код наивысшей группы по прочности изоляции. Поэтому к моменту времени Т4 в блок 16 фиксации результатов записывается код наивысшей группы (например, 9).

5 В момент Т4 блок управления переходит в четвертое состояние, в котором вырабатывается сигнал DN понижения испытательного напряжения. Этот сигнал разрешает прохождение импульсов через

0 элемент И 5 на декрементный вход. Частота на втором выходе делителя 3 частоты выбирается, исходя из наибольшей допустимой скорости снижения испытательного напряжения. На фиг. 4 показано, что скорость

5 снижения испытательного напряжения значительно превышает скорость его повышения.

Уменьшение испытательного напряжения происходит до тех пор, пока дешифратор 11 кода отключения не выявит код,

соответствующий испытательному напряжению, при котором возможно полное его отключение без риска повредить изделие даже самой низшей классификационной группы. В момент Т5 выявления такого кода сигнал КО с дешифратора 11 переводит блок управления в последнее пятое состояние, где испытательное напряжение полностью отключается и вырабатывается сигнал Е1, разрешающий работу исполнительного органа 17. Если исполнительный орган представляет из себя индикатор, то он высвечивает номер группы по величине пробивного напряжения, код которого хранится в блоке 16. Однако исполнительным органом может быть принтер, печатающий номер группы, или разбраковочный механизм.

Описанный цикл испытаний начинался при нулевом состоянии блока управления, однако запуск очередного исследования может производиться без сброса блока управления, Например,в момент времени Т6 очередной запускающий импульс поступает при пятом состоянии блока управления и переводит его сразу в первое состояние. Далее работа продолжается точно так же, как при запуске из исходного состояния. Сначала устанавливается начальное испытательное напряжение, а при переходе в момент времени Т7 во второе состояние начинается увеличение испытательного напряжения. На фиг. 4 показано, что в момент времени Т8, в отличие от момента ТЗ, достигает предельного значения ток через изделие при напряжении, меньшем нижней границы первой группы U1. Это свидетельствует о браке. За время Т8-Т9 в третьем состоянии код этого пониженного напряжения преобразуется в код брака, который сохраняется в блоке 16 фиксации результатов. После снижения напряжения в момент Т10 код брака поступает в исполнительный орган 17 для отбраковки изделия в пятом состоянии блока управления.

Последний цикл исследований на фиг. 4 показывает, что предельный ток достигает предельного значения при испытательном напряжении в диапазоне U2-U3. Поэтому такое изделие отнесено к второй классификационной группе по величине электрической прочности изоляции,

Таким образом, устройство позволяет классифицировать качественные изделия по электрической прочности изоляции без их порчи во всем диапазоне напряжений, а также отбраковывать изделия с пониженной электрической прочностью изоляции.

Формула изобретения 1. Устройство для определения качества изделий по электрической прочности изоляции, содержащее первую и вторую клеммы

для подключения контролируемого изделия и соединенные соответственно с первым выходом упоавляемого источника испытательного напряжения непосредственно и с вторым его выходом через датчик предель0 ного тока, генератор тактовых импульсов, первый элемент И, блок фиксации результатов, блок управления, первый вход которого соединен с выходом датчика предельного кода, счетчик, вход которого соединен с вы5 ходом первого элемента И, первый вход которого соединен с первым выходом блока управления, отличающееся тем, что, с целью повышения надежности достоверности, в устройство введены преобразователь

0 кодов, дешифратор предельного кода, дешифратор кода отключения, задатчик начального кода, исполнительный орган, элемент ИЛИ, инвертор, делитель частоты, второй элемент И,в качестве счетчика ис5 пользован реверсивный счетчик, при этом выход первого элемента И соединен с икре- ментирующим входом реверсивного счетчика, второй выход блока управления соединен с первым входом второго элеетен0 та И, выходом подключенного к декремен- тирующему входу реверсивного счетчика, третий выход блока управления соединен с входом разрешения записи кода реверсивного счетчика, информационным входом

5 подключенного к выходу задатчика начального кода, выход генератора тактовых импульсов подключен к входу делителя частоты, первый и второй выходы которого соединены с вторыми входами соответст0 венно первого и второго элементов И, выход реверсивного счетчика подключен к входам управляемого источника испытательного напряжения, дешифратора предельного кода, дешифратора кода

5 отключения и входу преобразователя кодов, выходом подключенного к информационному входу блока фиксации результатов, вход разрешения которого соединен с четвертым выходом блока управления, а выход

0 - с информационным входом исполнительного органа, разрешающий вход которого подключен к пятому выходу блока управления, выход дешифратора предельного кода соединен с вторым входом блока управле5 ния и первым входом элемента ИЛИ, вторым входом подключенного к выходу датчика предельного тока, а выходом через инвертор соединенного с третьим входом первого элемента И, выход дешифратора кода отключения соединен с входом сброса

реверсивного счетчика с третьим входом блока управления, четвертый вход которого соединен с шиной Пуск, пятый вход блока управления соединен с шиной Останов и входом сброса реверсивного счетчика.

SUAgf

ElDN

ФигЗ

0

5

тым входом шифратора состояний и входом программируемой логической матрицы, первый-пятый выходы которой соединены с соответствующими выходами блока управления, пятый выход и вход синхронизации которого соединены соответственно с вторым и третьим входом блока памяти переменных состояний.

т

Фиг А

| Устройство для плавного регулирования испытательного напряжения | 1980 |

|

SU894612A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения пробивногоНАпРяжЕНия диэлЕКТРиКОВ | 1978 |

|

SU800909A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-07-07—Публикация

1990-10-08—Подача