Изобретение относится к электросвязи, может найти применение в системах связи для передачи дискретной информации и является усовершенствованием устройства по авт. св. 1 1149427.

Целью изобретения является расширение класса передаваемых сигналов.

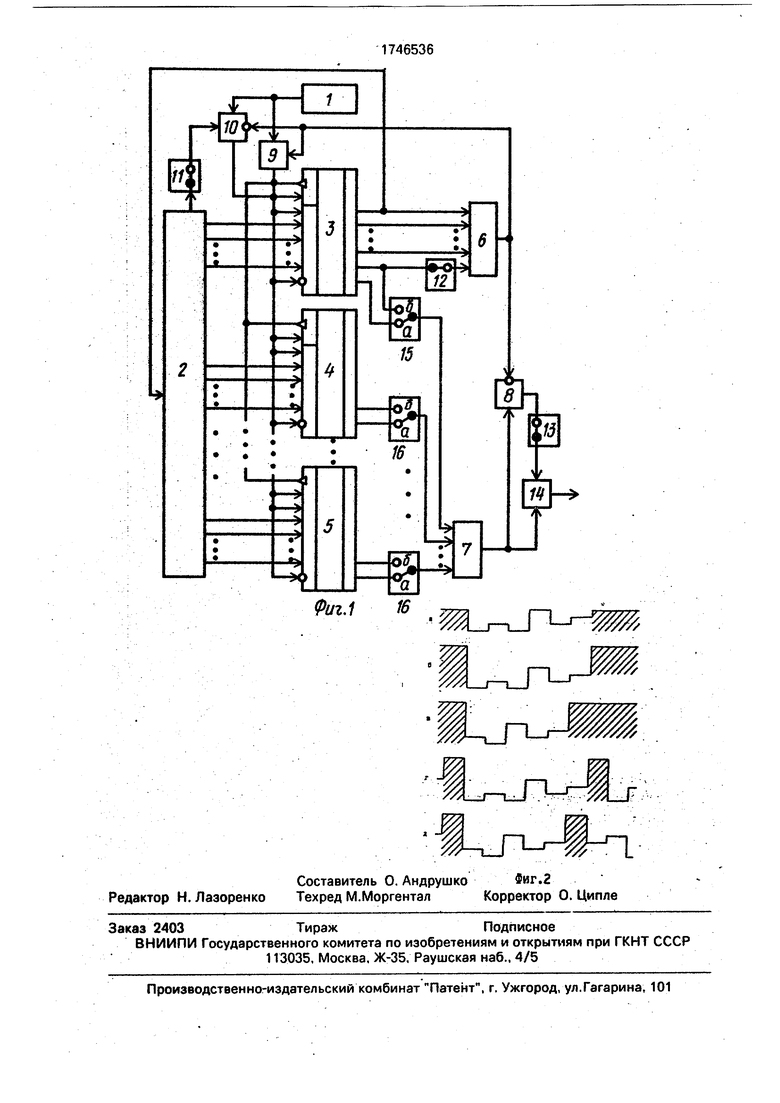

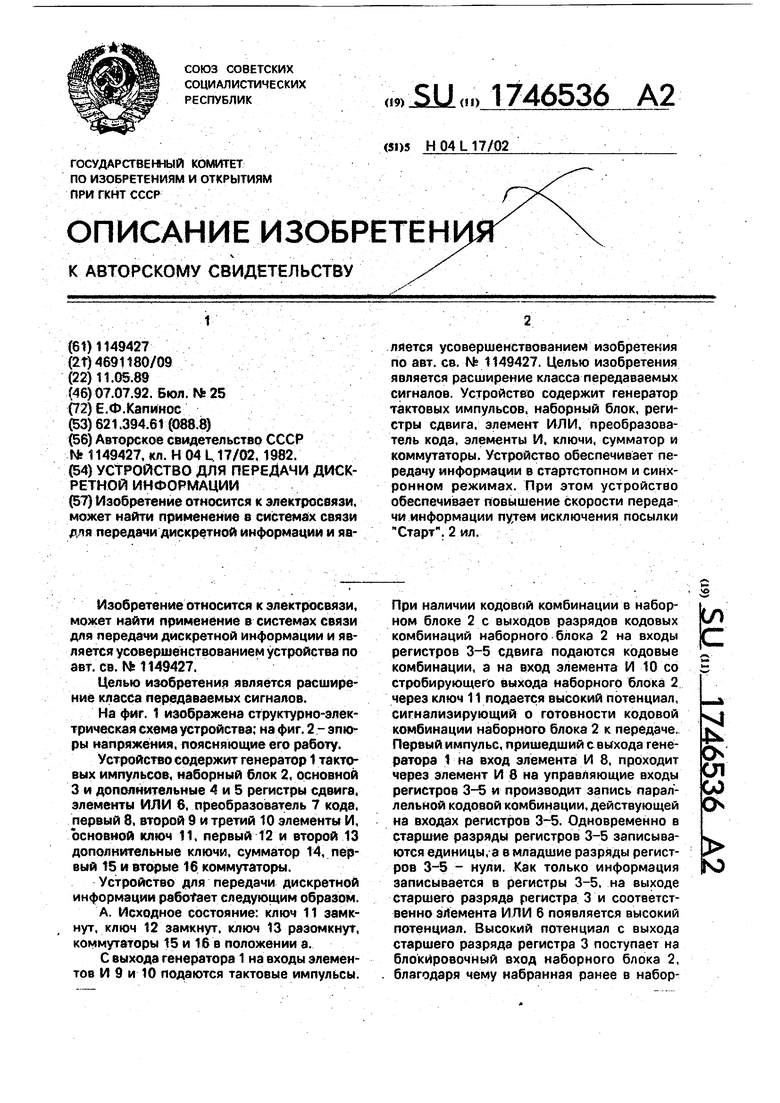

На фиг. 1 изображена структурно-электрическая схема устройства; на фиг. 2 - эпюры напряжения, поясняющие его работу.

Устройство содержит генератор 1 тактовых импульсов, наборный блок 2, основной 3 и дополнительные 4 и 5 регистры сдвига, элементы ИЛИ 6, преобразователь 7 кода, первый 8. второй 9 и третий 10 элементы И, основной ключ 11, первый 12 и второй 13 дополнительные ключи, сумматор 14, первый 15 и вторые 16 коммутаторы.

Устройство для передачи дискретной информации работает следующим образом.

А. Исходное состояние: ключ 11 замкнут, ключ 12 замкнут, ключ 13 разомкнут, коммутаторы 15 и 16 в положении а.

С выхода генератора 1 на входы элементов И 9 и 10 подаются тактовые импульсы.

При наличии кодовой комбинации в наборном блоке 2 с выходов разрядов кодовых комбинаций наборного блока 2 на входы регистров 3-5 сдвига подаются кодовые комбинации, а на вход элемента И 10 со стробирующего выхода наборного блока 2 через ключ 11 подается высокий потенциал, сигнализирующий о готовности кодовой комбинации наборного блока 2 к передаче. Первый импульс, пришедший с выхода генератора 1 на вход элемента И 8, проходит через элемент И 8 на управляющие входы регистров 3-5 и производит запись параллельной кодовой комбинации, действующей на входах регистров 3-5. Одновременно в старшие разряды регистров 3-5 записываются единицы, а в младшие разряды регистров 3-5 - нули. Как только информация записывается в регистры 3-5, на выходе старшего разряда регистра 3 и соответственно элемента И ПИ 6 появляется высокий потенциал. Высокий потенциал с выхода старшего разряда регистра 3 поступает на блокировочный вход наборного блока 2, благодаря чему набранная ранее в наборном блоке 2 кодовая комбинация сбрасывается и дается разрешение на набор новой комбинации. Высокий потенциал с выхода элемента ИЛИ 6 поступает на входы элементов И 9 и 10, благодаря чему запрещается прохождение тактовых импульсов через элемент И 10 и разрешается их прохождение через элемент И 9. С выходов младших разрядов регистров 3-5 сдвига кодовые посылки кодовой комбинации, записанной в младшие разряды регистров 3-5. поступают на входы преобразователя 7 двухпозицион- нсго кода в 2П позиционный (где п - число регистров 3-5). Так как в младшие разряды регистров 3-5 были записаны нули, то и на выходе преобразователя 7 кода устанавливается нулевой уровень сигнала, который через сумматор 14 поступает на выход устройства. Таким образом, формируется посылка Старт. С приходом импульсов с выхода элемента И 9 на синхронизирующие входы регистров 3-5 сдвига в последних производится сдвиг записанных кодовых комбинаций. Так как на управляющих входах регистров 3-5 действует низкий потенциал, запись по параллельным входам запрещается и в регистры 3-5 по мере сдвига кодовых комбинаций записываются нули за счет подключенных входов приема последовательной информации к шине нулевого потенциала.

Благодаря тому, что сдвиг информации (кодовых комбинаций) в регистрах 3-5 сдвига происходит одновременно с каждым тактом сдвига, на входы преобразователя 7 кода поступают несколько одноименных разрядов двухпозиционного кода. Преобразователь 7 кода преобразует входные разряды двухпозиционного кода в один разряд 2-поэиционного кода. С выхода преобразователя 7 2-позиционный код через сумматор 14 поступает на выход устройства.

При записи в младший разряд регистров 3-5 сдвига последней единицы, записанной в начале цикла работы устройства в старший разряд регистров 3-5, на выходе элемента ИЛИ 6 появляется низкий потенциал, который запрещает прохождениетак- товых импульсов через элемент И 9. При этом на выходе преобразователя 7 устанавливается высокий потенциал, который в качестве стоповой посылки поступает на выход устройства.

При наличии в наборном блоке 2 новой кодовой комбинации цикл работы устройства повторяется.

Структура кадра сообщения для описанного режима работы устройства приведена на фиг. 2а. Устройство в данном случае

обеспечивает передачу информации в стар- тстопном режиме 2-позиционным кодом.

Б. Исходное состояние: ключ 11 замкнут, ключ 12 замкнут, ключ 13 замкнут, коммутаторы 15 и 16 в положении а.

Работа устройства аналогична вышеописанному, за исключением формирования уровня стоповой посылки после выдачи устройством последней значимой посылки

передаваемой кодовой комбинации.

При записи в младший разряд регистров 3-5 сдвига последней единицы, записанной в начале цикла работы устройства в старший разряд регистров 3-5 сдвига, на

выходе элемента ИЛИ 6 появляется низкий потенциал, который запрещает прохождение тактовых импульсов через элемент И 9. При этом на выходе преобразователя 7 устанавливается высокий потенциал, который

поступает на второй вход сумматора 14. На выходе элемента И 8 также устанавливается высокий потенциал, который через замкнутый ключ 13 поступает на первый вход сумматора 14. Высокие потенциалы.

действующие на входах сумматора 14, суммируются в сумматор 14 и с его выхода поступают на выход устройства.

Структура кадра сообщения для данного режима работы устройства приведены на

фиг. 26. Устройство в данном случае обеспечивает передачу информации в стартстоп- ном режиме (2П + 1)-позиционным кодом.

В. Исходное состояние: ключ 11 замкнут, ключ 12 разомкнут, ключ 13 замкнут,

коммутаторы 15 и 16 в положении б.

С выхода генератора 1 на входы элементов И 9 и 10 подаются тактовые импульсы. При наличии кодовой комбинации в наборном блоке 2 с выходов разрядов кодовых

комбинаций наборного блока 2 на входы регистров 3-5 подаются кодовые комбинации, а на вход элемента И 10 со стробирую- щего выхода наборного блока 2 через ключ 11 подается высокий потенциал, сигнализирующий о готовности кодовой комбинации наборного блока 2 к передаче. Первый импульс, пришедший с выхода генератора 1 на вход элемента И10. проходит через элемент И 10 на управляющие входы регистров 3-5

и производит запись параллельной кодовой комбинации, действующей на входах регистров 3-5. в регистры 3-5. Одновременно в старшие разряды регистров 3-5 записываются единицы, а в младшие разряды регистров нули.

Как только инфоомация записывается в регистры 3-5. на выходе старшего разряда регистра 3 и соответственно элемента ИЛИ 6 появляется высокий потенциал. Высокий

потенциал с выхода старшего разряда регистра 3 поступает на блокировочный вход наборного блока 2, благодаря чему набранная ранее в наборном блоке 2 кодовая комбинация сбрасывается и дается разрешение на набор новой комбинации. Высокий потенциал с выхода элемента ИЛИ 6 поступает на входы элементов И 9 и 10, благодаря чему запрещается прохождение тактовых импульсов через элемент И 10 и разрешает их прохождение через элемент И 9. С выхода вторых разрядов регистров 3-5 кодовые посылки младших разрядов кодовых комбинаций, записанных в регистры 3- 5 сдвига, поступают через коммутаторы 15 и 16 на входы преобразователя 7 двухпози- ционного кода в 2-позиционный. Сигнал с выхода преобразователя 7 кода через сумматор 14 поступает на выход устройства.

С приходом импульсов с выхода элемента И 9 на синхронизирующие входы регистров сдвига в последних производится сдвиг записанных кодовых комбинаций. Так как на управляющих входах регистров 3-5 действует низкий потенциал, запись по параллельным входам запрещается, и в регистры 3-5 по мере сдвига кодовых комбинаций записываются нули за счет подключенных входов приема последовательной информации к шине нулевого потенциала.

Благодаря тому, что сдвиг информации (кодовых комбинаций) в регистрах 3-5 сдвига происходит одновременно с каждым тактом сдвига, на входы преобразователя 7 кода поступают п одноименных разрядов двухпозиционногокода. Преобразователь преобразует входные разряды двухпозиционного кода в один разряд 2п-позиционного кода. С выхода преобразователя 7 сигнал 2-позиционного кода через сумматор 14 поступает на выход устройства.

При записи во второй разряд регистров 3-5 сдвига последней единицы, записанной в начале цикла работы устройства в старший разряд регистров 3-5, на выходе элемента ИЛИ 6 появляется низкий потенциал, который запрещает прохождение тактовых импульсов через элемент И 9. При этом на выходе преобразователя 7 устанавливается высокий потенциал, который поступает на второй вход сумматора 14. На выходе элемента И 8 также устанавливается высокий потенциал, который через замкнутый ключ 13 поступает на первый вход сумматора 14. Высокие потенциалы, действующие на входах сумматора 14, суммируются в сумматоре 14 и с его выхода поступают на выход устройства.

Структура кадра сообщения для данного режима работы устройства приведена на

фиг. 2в. Устройство в данном случае обеспе- чивает передачу информации в стартстоп- ном режиме (2п+1)-позиционным кодом. Г. Исходное состояние: ключ 11 разомкнут, ключ 12 замкнут, ключ 13 замкнут, коммутаторы 15 и 16 в положении а.

При наличии низкого потенциала на выходе элемента ИЛИ 6 на выходе устройства действует высокий потенциал, соответству0 ющий символу синхронизации, при этом запрещается прохождение тактовых импульсов через элемент И 9 и разрешается прохождение тактовых импульсов через элемент И 10. Прошедший через элемент И

5 10 тактовый импульс поступает на управляющие входы регистров 3-5 сдвига и производит запись параллельной кодовой комбинации, действующей на входах регистров 3-5. Одновременно в старшие разря0 ды регистров 3-5 записываются единицы, а в младшие разряды регистров 3-5 - нули.

Как только информация записывается в регистры 3-5, на выходе старшего разряда регистра 3 и соответственно элемента ИЛИ

5 6 появляется высокий потенциал. Высокий потенциал с выхода старшего разряда регистра 3 поступает на блокировочный вход наборного блока 2. благодаря чему набранная ранее в наборном блоке 2 кодовая ком0 бинация сбрасывается и дается разрешение на набор новой комбинации. Высокий потенциал с выхода элемента ИЛИ 6 поступает на входы элементов И 9 и 10, благодаря чему запрещается прохождение тактовых им5 пульсов через элемент И 10 и разрешается прохождение тактовых импульсов через элемент И 10. С выхода младших разрядов регистров 3-5 сдвига через коммутаторы 15 и 16, кодовые посылки кодовых комбина0 ций. записанных в младшие разряды регистров 3-5, поступают на входы преобразователя 7 кода. Так как в младшие разряды регистров 3 -5 были записаны нули, то и на выходе преобразователя 7 кода ус5 танавливается нулевой уровень сигнала, который через сумматор 14 поступает на выход устройства. С приходом импульсов с выхода элемента И 9 на синхронизирующие входы регистров 3-5 сдвига в последних

0 производится сдвиг записанных кодовых комбинаций. Так как на управляющих входах регистров 3-5 действует низкий потенциал, запись по параллельным входам запрещается и в регистры 3-5 по мере сдви5 га кодовых комбинаций записываются нули за счет подключенных входов приема последовательной информации регистров 3-5 к шине нулевого потенциала.

Благодаря тому, что сдвиг информации (кодовых комбинаций) в регистрах 3-5 сдвига происходит одновременно с каждым тактом сдвига, на входы преобразователя 7 кода поступают п одноименных разрядов двухпоэиционного кода. Преобразователь 7 кода преобразует п входных разрядов двух- позиционного кода в один разряд 2п-пози- ционного кода. С выхода преобразователя 7 сигналы 2п-позиционного кода через сумматор 14 поступают на выход устройства.

При записи в младший разряд регистров 3-5 сдвига последней единицы, записанной в начале цикла работы устройства старший разряд регистров 3-5 сдвига, на выходе элемента ИЛИ 6 появляется низкий потенциал, который запрещает прохождение тактовых импульсов через элемент И 9 и разрешает прохождение тактовых импульсов через элемент И 10. При этом на выходах преобразователя 7 и элемента И 8 устанавливаются высокие потенциалы, которые подаются на входы сумматора 14. Сумматор 14 на выход устройства выдает сигнал высокого уровня, соответствующий символу синхронизации. При прохождении через элемент И 8 тактового импульса цикл работы устройства повторяется.

Структура кадра сообщения для данного режима работы устройства приведена на фиг. 2г. Устройство в данном случае обеспечивает передачу информации в синхронном режиме (2п+1)-позиционным кодом.

Д. Исходное состояние: ключ 11 разомкнут, ключ 12 разомкнут, ключ 13 замкнут, коммутаторы 15 и 16 в положении б.

Работа устройства аналогична вышеописанному в п. Г, за исключением того, что сразу после символа синхронизации на выход устройства выдается информационная посылка, соответствующая кодовым посылкам, записанным во вторые разряды регистров 3-5 сдвига.

Структура кадра сообщения для данного режима работы устройства приведена на фиг. 2д. Устройство в данном случае обеспечивает передачу информации в синхронном режиме (2п+1}-позиционным кодом.

Устройство обладает широкими функциональными возможностями, так как обеспечивает передачу информации в стартстопном режиме тремя структурами сигналов (фиг 2а-в) и в синхронном режиме двумя структурами сигналов (фиг. 2г. д). При

этом устройство обеспечивает повышение скорости передачи информации за счет исключения посылки Старт (фиг. 2в, д). Это стало возможным благодаря принятому в

устройстве (2п+1)-позиционному коду. Высокий уровень сигнала обеспечивает передачу посылки Стоп (фиг. 2в) или Символ синхронизации (фиг. 2д). а снятие высокого уровня сигнала соответствует стопстартовому переходу. Минимальная длительность стоповой посылки равна длительности кодовой посылки, т.е. периоду следования тактовых импульсов генератора 1 тактовых импульсов. Длительность посылки символа

синхронизации равна длительности кодовой посылки.

При равенстве скоростей передачи выходные сигналы устройства (фиг. 2в, д) обладают более высокой помехоустойчивостью

за счет большей длительности элементарных посылок кадра сообщения. Формула изобретения Устройство для передачи дискретной информации по авт. св. Мг 1149427, о т л ичающееся тем, что, с целью расширения класса передаваемых сигналов, введены дополнительные регистры сдвига, первый и вторые коммутаторы, первый и второй дополнительные ключи и преобразователь кода, при этом выход младшего разряда основного регистра сдвига подключен к первому входу первого элемента И через последовательно соединенные первый коммутатор и преобразователь кода, соответствующий дополнительный выход основного регистра сдвига подключен к соответствующему входу элемента ИЛИ через первый дополнительный ключ и к второму входу первого коммутатора непосредственно, выход первого элемента И подключен к второму входу сумматора через второй дополнительный ключ, соответствующие дополнительные выходы наборного блока подключены к соответствующим разрядным

входам дополнительных регистров сдвига, синхронизирующие, управляющие входы и входы старшего и младшего разрядов которых соединены с одноименными входами основного регистра сдвига, а выходы дополнительных регистров сдвига через соответствующие вторые коммутаторы подключены к другим входам преобразователя кода.

п Г

7 -1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи дискретной информации | 1989 |

|

SU1709548A1 |

| Устройство для передачи дискретной информации | 1982 |

|

SU1149427A1 |

| Устройство для передачи сообщений | 1991 |

|

SU1785023A1 |

| Стартстопный передатчик | 1980 |

|

SU1135013A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2108680C1 |

| СТАРТСТОПНЫЙ ПЕРЕДАТЧИК | 1992 |

|

RU2042275C1 |

| Устройство для передачи сообщений | 1988 |

|

SU1520572A1 |

| Стартстопный приемник | 1980 |

|

SU1322491A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ | 1992 |

|

RU2037968C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2029988C1 |

Изобретение относится к электросвязи, может найти применение в системах связи дня передачи дискретной информации и является усовершенствованием изобретения по авт. св. № 1149427. Целью изобретения является расширение класса передаваемых сигналов. Устройство содержит генератор тактовых импульсов, наборный блок, регистры сдвига, элемент ИЛИ, преобразователь кода, элементы И, ключи, сумматор и коммутаторы. Устройство обеспечивает передачу информации в стартстопном и синхронном режимах. При этом устройство обеспечивает повышение скорости передачи информации путем исключения посылки Старт. 2 ил.

Риг.1

16

Щ-г-п-П-г-Ж

| Устройство для передачи дискретной информации | 1982 |

|

SU1149427A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1992-07-07—Публикация

1989-05-11—Подача