Изобретение относится к цифровым электронным схемам, а именно к схемам линий задержки, широко применяемым для синхронизации электронных устройств различного назначения.

Известна схема генератора задержанных импульсов, содержащая два переключа- теля тока, каждый из которых имеет свою времязадающую цепь, соединенную с входом схемы через первый и второй входуые транзисторы. Выходы переключ ателей тока соединены с входом вентильной схемы, выход которой подключен к выходу схемы. При поступлении входного импульса времязада- ющие цепи формируют экспоненциальные сигналы на входах переключателей тока, а с выходов переключателей тока снимаются задержанные по отношению к входному импульсы разной длительности. На выходе вентильной схемы формируется сигнал, равный разности задержанных импульсов и который подавляется в период действия входного импульса.

Таким образом, генератор работает по принципу получения разности задержанных импульсов, имеющих различную величину задержки, и осуществляет задержку входного импульса на величину, большую длительности импульса.

Так как в известном генераторе длительность задержанного импульса не.связа- на с длительностью входного импульса, а равна разности двух фиксированных задержек, в нем невозможно получение неискаженных по отношению к входному задержанных импульсов при поступлении на вход схемы импульсов разной длительности. Целью изобретения является повышение точности длительности задержанных импульсов путем одинаковой задержки фронта и среза.

Цель достигается том, что в генераторе задержанных импульсов, содержащем входную-и выходную шину, переключатель тока, две времязадающих цепи, пятый и второй транзисторы резистор, соединенные

у

Ј

ч| СП

Сл СО

так. что вход переключателя тока подключен к выходу первой времязадающей цепи, эмиттер первого транзистора соединен с общей шиной, первая времязадающая цепь выполнена интегрирующей, а вторая - дифференцирующей, введены первый инвертор, входная цепь второго инвертора и выходной инвертирующий буфер „Вход первого инвертора подключен к входной шине, а его выход соединен с входом входной цепи второго инвертора, выход которой подключен к базе первого транзистора, который образует выходной транзистор второго инвертора. Коллектор первого транзистора соединен с входом первой времязадающей цепи и через резистор с шиной питания. Инверсный выход переключателя тока подключен по входу выходного инвертирующего буфера, выход которого соединен с выходной шиной. Вход второй времязздающей цепи подключен к выходу первого инвертора, выход второй времязадающей цепи соединен с базой второго транзистора, эмиттер которого подключен к общей шине, а коллектор - к базе первого транзистора.Ј

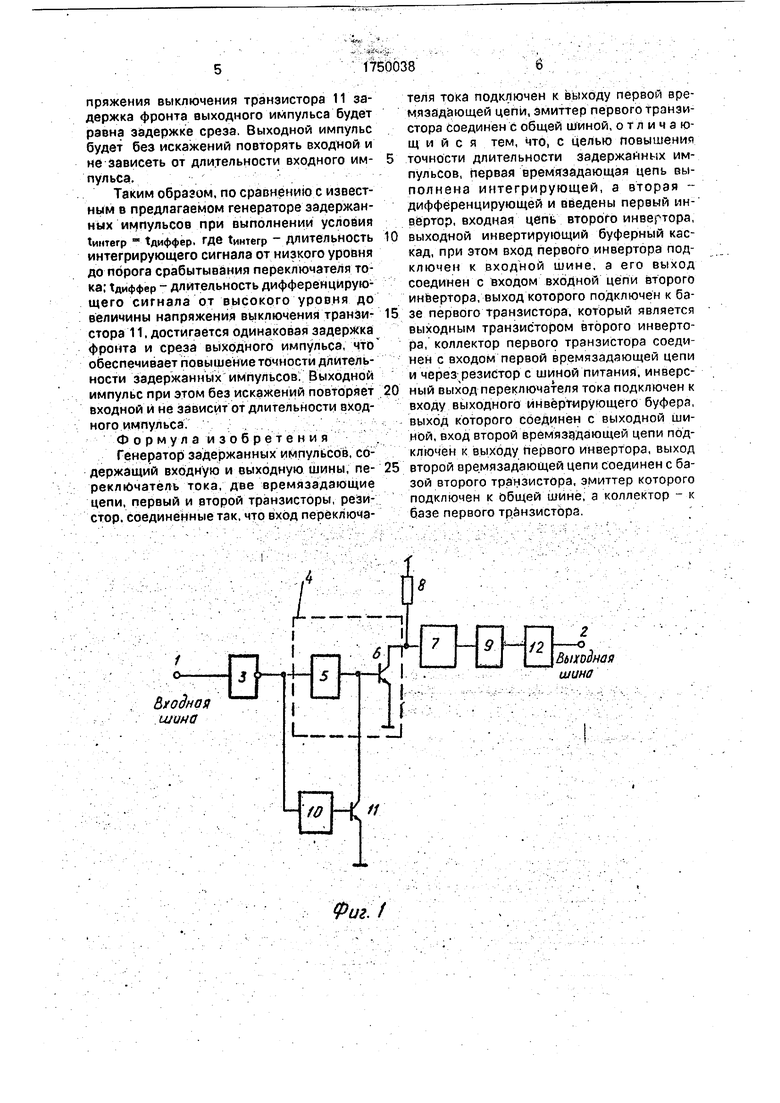

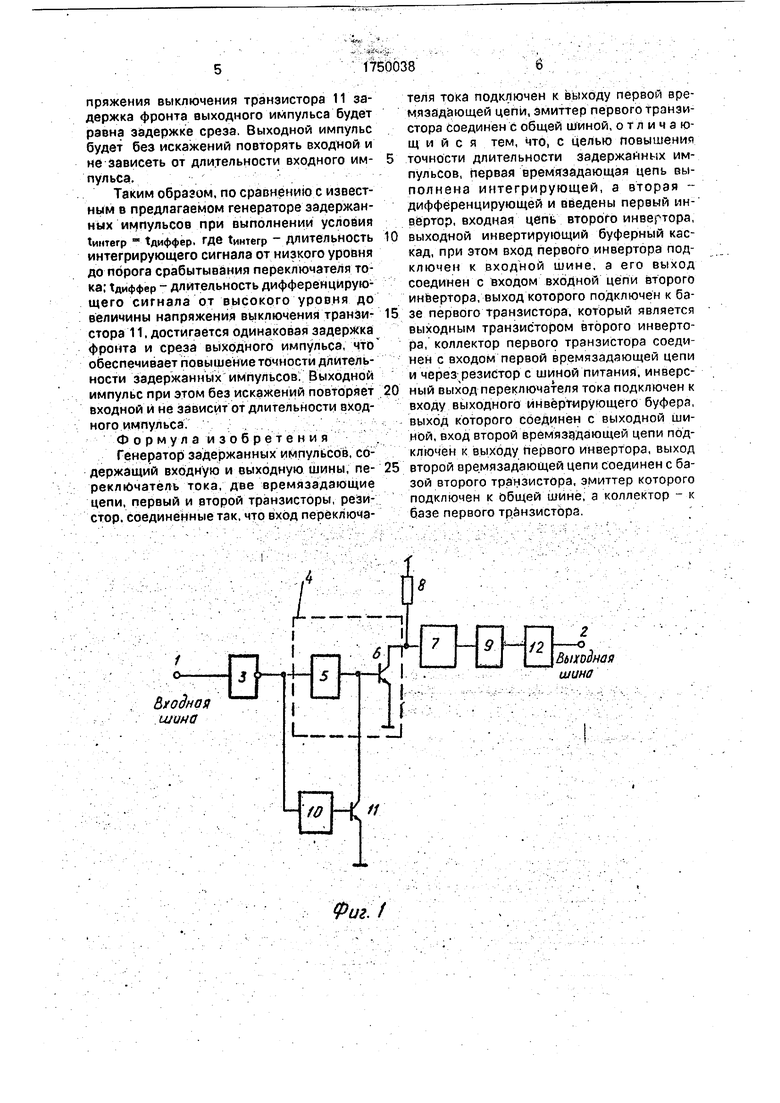

На фиг. 1 представлена схема генератора задержанных импульсов; на фиг 2 - временная диаграмма ее работы

Генератор задержанных импульсов включает в себя входную 1 и выходную 2 шины, первый инвертор 3. второй инвертор 4. содержащий входную цепь 5 и выходной транзистор 6, интегрирующую цепь 7, резистор 8, переключатель 9 тока. Дифференцирующую цепь 10, транзистор 11, выходной инвертирующий буфер 12. Входная шина 1 соединена с входом первого инвертора 3, выход которого подключен к входной цепи 5 второго инвертора А, выход входной цепи

5соединен с базой выходного транзистора

6второго Инвертора 4, эмиттер которого соединен с общей шиной, а коллектор соединён с входом интегрирующей цепи 7 и через резистор 8 с шиной питания. Выход интегрирующей цепи 7 соединен с входом переключателя 9 тока, инверсный выход ко торого через выходной инвертирующий буфер 12 соединен с выходной шиной 2 Вход дифференцирующей цепи 10 соединен с выходом первого инвертора 3, а ее выход - с базой транзистора 11. эмиттер которого подключен к общей шине, а коллектор - к базе выходного транзистора $ второго инвертора 4.

Генератор задержанных импульсов работает следующим образом.

При низком уровне сигнала на входной шине 1 на выходе первого инвертора 3 высокий уровень, на выходе второго инвертора 4 низкий уровень, на выходе пере люча- теля 9 тока высокий уровень и на выходе инвертирующего буфера и, соответственно, на выходной шине 2 низкий уровень При

поступлении входного импульса на выходе второго инвертора 4 появляется высокий уровень сигнала, задаваемый через резистор 8, соединенный с шиной питания, который поступает на вход интегрирующей цепи

0 7 Выходной транзистор 6 второго инвертора 4 при этом выключен через входную цепь 5. На выходе дифференцирующей цепи 10 появляется отрицательный пик и транзистор 11 остается в выключенном состоянии.

5 На выходе интегрирующей цепи 7 формируется экспоненциальный сигнал, поступающий на вход переключателя 9 тока (фиг. 2). По окончании действия входного импульса величина экспоненциального сигнала на вы0 ходе переключателя 9 тока еще не достаточна для срабатывания переключателя 9 тока, поскольку не достигает пороговой величины (фиг 2) Первый инвертор 3 по окончании действия входного импульса и соответст5 венного переключения сигнала на входной шине 1 из высокого уровня в низкий формирует на входе дифференцирующей цепи 10 высокий уровень сигнала На выходе дифференцирующей цепи 10 появляется положи0 тельный пик, открывающий транзистор 11, который продолжает удерживать выходной транзистор 6 второго инвертора 4 в выключенном состоянии несмотря на то, что входная цепь 5 второго инвертора 4 теперь

5 формирует сигнал для включения транзистора б (фиг 2). Экспоненциальный сигнал на выходе интегрирующей цепи 7 продолжает увеличиваться и при достижении пороговой величины приводит к срабатыванию

0 переключателя 9 тока, и инвертирующий буфер 12 формирует на выходной шине 2 фронт задержанного импульса (фиг. 2). По окончании положительного пика на выходе дифференцирующей цепи 10 транзистор 11

5 выключается, а выходной транзистор 6 включается, управляемый входной цепью 5 второго инвертора 4 (фиг. 2).

На выходе интегрирующей цепи 7 устанавливается низкий уровень сигна/ta, кото0 рый передается на вход переключателя 9 тока и приводит к его срабатыванию. Инвертирующий буфер 12 при этом формирует на выходной шине 2 срез задержанного сигнала (фиг. 2). При равенстве длительности экс5 поненциального сигнала, формируемого интегрирующей цепью 7, от низкого уровня до величины порога срабатывания переключателя 9 тока и длительности положительного пика, формируемого дифференцирующей цепью, от высокого уровня до величины напряжения выключения транзистора 11 задержка фронта выходного импульса будет равна задержке среза. Выходной импульс будет без искажений повторять входной и не зависеть от длительности входного им- пульса.

Таким образом, по сравнению с известным в предлагаемом генераторе задержанных импульсов при выполнении условия Химтегр 1диффер, где 1цнтегр - Длительность

интегрирующего сигнала от низкого уровня до порога срабытывания переключателя тока; Хдиффер - длительность дифференцирующего сигнала от высокого уровня до величины напряжения выключения транзи- стора 11. достигается одинаковая задержка фронта и среза выходного импульса, что обеспечивает повышение точности длительности задержанных импульсов. Выходной импульс при этом без искажений повторяет входной и не зависит от длительности входного импульса.

Ф о р м у л а и з о б р е т е н и я Генератор задержанных импульсов, содержащий входную и выходную шины, пе- реключателъ тока, две времязадающие цепи, первый и второй транзисторы, резистор, соединенные так, что вход переключателя тока подключен к выходу первой вре- мязадающей цепи, эмиттер первого транзистора соединен с общей шиной, отличающийся тем, что, с целью повышения точности длительности задержанных импульсов, первая времяэадающэя цепь выполнена интегрирующей, а вторая - дифференцирующей и введены первый инвертор, входная цепь второго инвертора, выходной инвертирующий буферный каскад, при этом вход первого инвертора подключен к входной шине, а его выход соединен с входом входной цепи второго инвертора, выход которого подключен к базе первого транзистора, который является выходным транзистором второго инвертора, коллектор первого транзистора соединен с входом первой времязадающей цепи и через резистор с шиной питания, инверсный выход переключателя тока подключен к входу выходного инвертирующего буфера, выход которого соединен с выходной шиной, вход второй времязддающей цепи подключен к выходу первого инвертора, выход второй времязадающей цепи соединен с базой второго транзистора, эмиттер которого подключен к общей шине, а коллектор - к базе первого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор задержанных импульсов | 1990 |

|

SU1750037A1 |

| Устройство емкостной гальванической развязки | 1986 |

|

SU1370767A1 |

| Устройство задержки | 1989 |

|

SU1793535A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

| ЭЛЕКТРОННЫЙ ТЕРМОРЕГУЛЯТОР ДЛЯ ЭЛЕКТРОУТЮГА | 1992 |

|

RU2078371C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛА ВКЛЮЧЕНИЯ ПОМЕХ | 1993 |

|

RU2122281C1 |

| Устройство контроля импульсных сигналов | 1981 |

|

SU1003323A1 |

| Заторможенный релаксационный генератор | 1976 |

|

SU661724A1 |

| Импульсный источник питания с бестрансформаторным входом | 1986 |

|

SU1543392A1 |

| Генератор напряжения специальной формы | 1984 |

|

SU1202040A1 |

Изобретение относится к цифровым электронным схемам а именно к схемам линий задержки, широко применяемым для синхронизации электронных устройств различного назначения. Цель изобретения - повышение точности сохранения длительности задержанных импульсов путем одина- ковой задержки фронта и среза для задержек больших длительности импульса. Генератор задержанных импульсов содержит входную и выходную шины, первый инвертор, второй инвертор, включающий входную цепь и выходной транзистор, интегрирующую цепь (И Ц), резистор, переключатель тока (ПТ), дифференцирующую цепь (ДЦ). транзистор, выходнбй буфер. 2 ил.

Входная шина

Фиг.1

8

и и,

О,

и

ц, О -А

МММ - Г. (Ш-Г

V,

и„ и:

uftt

и а,

t t

Фиг. 2

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-07-23—Публикация

1990-10-01—Подача