Изобретение относится к микроэлектронике и вычислительной технике, а именно к схемам линий задержки, и может быть использовано для замедления скорости передачи данных и обеспечения синхронизации при обмене между подсистемами памяти и процессорными логическими схемами ЭВМ.

Наиболее близким техническим решением к заявляемому устройству задержки является генератор задержанных импульсов, схема которого содержит два элемента задержки, каждый из которых имеет свою времязадающую цепь, образованную конденсатором и резистором, причем общая точка соединения конденсатора и резистора соединена с входом элемента задержки, второй вывод конденсатора соединен с общей шиной, а второй вывод резистора - с шиной питания. Выходы первого и второго элементов задержки.соединены с входами вентильной схемы, выход которой подключен к выходу схемы. При работе известной

схемы на входы элементов задержки подаются запускающие импульсы, а с выходов элементов задержки снимаются задержанные импульсы разной длительности. На выходе вентильной схемы формируется сигнал, равный разности задержанных импульсов, который подавляется в период действия запускающего импульса.

Реализация известной схемы в интегральном исполнении связана с рядом трудностей, а именно наличие двух времязадающих конденсаторов требует значительной площади кристалла в монолитной схеме, а в случае гибридной схемы требует дополнительного навесного монтажа, снижающего надежность схемы. Для достижения высокой точности длительности задержанного импульса в известной схеме необходим точный подбор или .изготовление пары времязадающих конденсаторов, что связано с дополнительной трудоемкость. В известной схеме также ограничен диапазон задержки, что связано с конструкXI

Ю СО

ел со ел

цией времязадающей цепи, в которой ток заряда времязадающего конденсатора ограничивается только резистором.

Целью изобретения является упрощение схемы, повышение точности длительности задержанного импульса, увеличение диапазона задержки путём применения нового включения одной времязадающей цепи.

С этой целью в устройство задержки, содержащее входную и выходную шину, два элемента задержки, времязадающий конденсатор, первый и второй транзисторы, третий и четвертый транзисторы, эмиттеры которых соединены между собой, причем коллектор третьего транзистора соединен с шиной питания, а его база соединена с коллектором первого транзистора, эмиттер первого транзистора соединен с общей шиной, а его база соединена с эмиттером второго транзистора, эмиттеры пятого и шестого транзисторов соединены между собой, первый вывод времязадающего конденсатора соединен с общей шиной, согласно изобретению введены первый, второй и третий инверторы, вентильная схема 2И-2ИЛИ, первый и второй р-п-р-транзи- сторы, первый.и второй генераторы тока, первый, второй, третий, четвертый резисторы, шина опорного напряжения. Введенные элементы соединены таким образом, что база первого p-n-p-транзистора подключена к коллектору четвертого транзистора, эмиттер первого p-n-p-транзистора соединен с шиной питания, а его коллектор соединен с первым йходом схемы 2И, входящей в состав вентильной схемы 2И-2ИЛ1/1, и через первый резистор соединен с общей шиной, при этом второй вход схемы 2И соединен с выходом третьего инвертора, вход которого подключен к входной шине. База второго p-n-p-транзистора соединена с коллектором пятого транзистора, эмиттер второго р-п-р- транзистора соединен с шиной питания, а его коллектор соединен с вторым входом схемы 2ИЛИ, входящей в состав вентильной схемы 2И-ИЛИ, и через второй резистор с общей шиной. Выход вентильной схемы 2И- 2ИЛИ подключен к выходной шине, коллектор шестого транзистора подключен к шине питания, базы четвертого и шестого транзисторов соединены между собой и подключены к шине опорного напряжения, первый генератор тока включен между эмиттерами третьего и четвертого транзисторов и общей шиной, второй генератор тока включен между эмиттерами пятого и шестого транзисторов и общей, шиной, База первого транзистора через пятый резистор соединена с общей шиной, база третьего транзистора соединена с катодом первого диода и через третий резистор с общей шиной, анод первого диода соединен с эмиттером седьмого транзистора, база которого соединена

с коллектором второго транзистора и через шестой резистор с шиной питания, коллектор седьмого транзистора соединен с вторым выводом времязадающего конденсатора и коллектором восьмого транзистора. Эмиттер восьмого транзистора соединен с анодом второго диода, катод которого подключен к коллектору девятого транзистора, базе пятого транзистора и через четвертый резистор к общей шине,

5 эмиттер девятого транзистора соединен с общей шиной, а его база соединена с эмиттером десятого транзистора и через седьмой резистор соединена с общей шиной, коллектор десятого транзистора соединен с

0 базой восьмого транзистора и через восьмой резистор соединен с шиной питания, база десятого транзистора соединена с эмиттером одиннадцатого транзистора и через девятый резистор соединена с общей

5 шиной, коллектор одиннадцатого транзистора через десятый резистор соединен с шиной питания, а его база соединена с коллектором двенадцатого транзистора и через одиннадцатый резистор соединена с шиной

0 питания. Эмиттер двенадцатого транзистора соединен с эмиттером тринадцатого транзистора, базой второго транзистора и через двенадцатый резистор с общей шиной, коллектор тринадцатого транзистора

5 через тринадцатый резистор соединен с шиной питания, а его база соединена с базой двенадцатого транзистора, анодом третьего диода и через четырнадцатый резистор с шиной питания, катод третьего диода соеди0 цен с входной шиной.

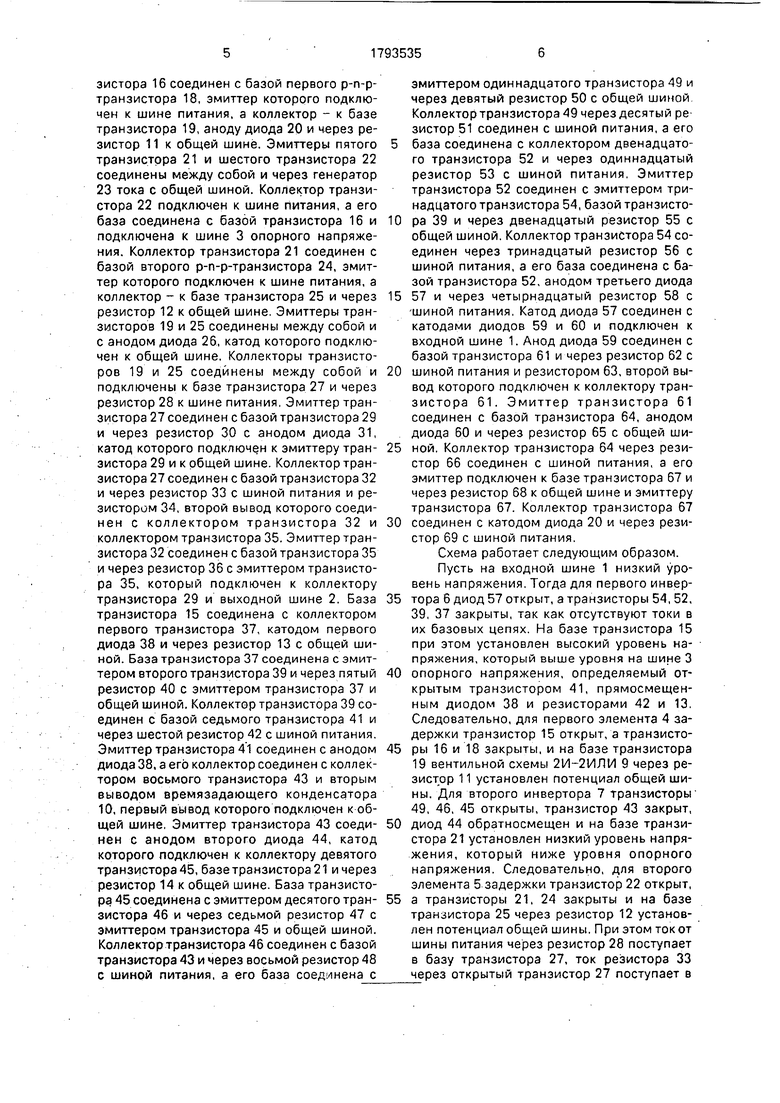

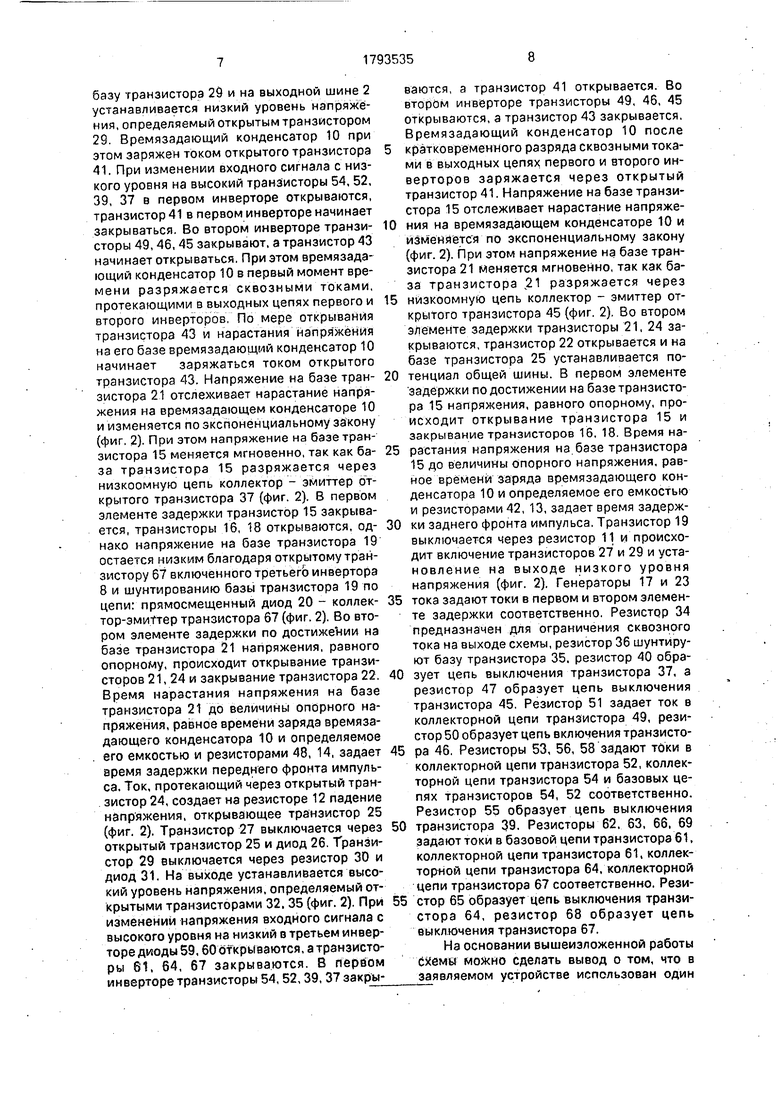

На фиг. 1 представлена электрическая принципиальная схема заявляемого устройства задержки; на фиг. 2 изображены эпюры напряжений, поясняющие работу устройст5 Ва задержки.

Устройство задержки содержит входную шину 1, выходную шину 2, шину 3 опорного напряжения, первый элемент 4 задержки и второй элемент 5 задержки, пер0 вый инвертор 6, второй инвертор 7 и третий инвертор 8, вентильную схему 2И-2ИЛИ 9, времязадающий конденсатор 10, первый резистор 11, второй резистор 12, третий резистор 13, четвертый резистор 14. Первый

5 элемент 4 задержки включает в себя третий транзистор 15 и четвертый транзистор 16, эмиттеры которых соединены между собой и через первый генератор 17 тока подключены к общей шине, коллектор транзистора 15 подключен к шине питания, коллектор транзистора 16 соединен с базой первого р-п-р- транзистора 18, эмиттер которого подключен к шине питания, а коллектор - к базе транзистора 19, аноду диода 20 и через резистор 11 к общей шине. Эмиттеры пятого транзистора 21 и шестого транзистора 22 соединены между собой и через генератор 23 тока с общей шиной. Коллектор транзистора 22 подключен к шине питания, а его база соединена с базой транзистора 16 и подключена к шине 3 опорного напряжения. Коллектор транзистора 21 соединен с базой второго р-п-р-транзистора 24, эмиттер которого подключен к шине питания, а коллектор - к базе транзистора 25 и через резистор 12 к общей шине. Эмиттеры транзисторов 19 и 25 соединены между собой и с анодом диода 26, катод которого подключен к общей шине, Коллекторы транзисторов 19 и 25 соединены между собой и подключены к базе транзистора 27 и через резистор 28 к шине питания, Эмиттер транзистора 27 соединен с базой транзистора 29 и через резистор 30 с анодом диода 31, катод которого подключен к эмиттеру тран- зистора 29 и к общей шине. Коллектор транзистора 27 соединен с базой транзистора 32 и через резистор 33 с шиной питания и резистором 34, второй вывод которого соединен с коллектором транзистора 32 и коллектором транзистора 35. Эмиттер транзистора 32 соединен с базой транзистора 35 и через резистор 36 с эмиттером транзистора 35, который подключен к коллектору транзистора 29 и выходной шине 2. База транзистора 15 соединена с коллектором первого транзистора 37, катодом первого диода 38 и через резистор 13 с общей шиной. База транзистора 37 соединена с эмиттером второго транзистора 39 и через пятый резистор 40 с эмиттером транзистора 37 и общей шиной. Коллектор транзистора 39 соединен с базой седьмого транзистора 41 и через шестой резистор 42 с шиной питания. Эмиттер транзистора 41 соединен с анодом диода 38, а его коллектор соединен с коллектором восьмого транзистора 43 и вторым выводом времязадающего конденсатора 10, первый вывод которого подключен к общей шине, Эмиттер транзистора 43 соеди- нен с анодом второго диода 44, катод которого подключен к коллектору девятого транзистора 45, базе транзистора 21 и через резистор 14 к общей шине. База транзистора 45 соединена с эмиттером десятого тран- зистора 46 и через седьмой резистор 47 с эмиттером транзистора 45 и общей шиной. Коллектортранзистора 46 соединен с базой транзистора 43 и через восьмой резистор 48 с шиной питания, а его база соединена с

эмиттером одиннадцатого транзистора 49 и через девятый резистор 50 с общей шиной, Коллектор транзистора 49 через десятый ре зистор 51 соединен с шиной питания, а его база соединена с коллектором двенадцатого транзистора 52 и через одиннадцатый резистор 53 с шиной питания. Эмиттер транзистора 52 соединен с эмиттером тринадцатого транзистора 54, базой транзистора 39 и через двенадцатый резистор 55 с общей шиной. Коллектор транзистора 54 соединен через тринадцатый резистор 56 с шиной питания, а его база соединена с базой транзистора 52, анодом третьего диода 57 и через четырнадцатый резистор 58 с -шиной питания. Катод диода 57 соединен с катодами диодов 59 и 60 и подключен к входной шине 1. Анод диода 59 соединен с базой транзистора 61 и через резистор 62 с шиной питания и резистором 63, второй вывод которого подключен к коллектору транзистора 61. Эмиттер транзистора 61 соединен с базой транзистора 64, анодом диода 60 и через резистор 65 с общей шиной. Коллектор транзистора 64 через резистор 66 соединен с шиной питания, а его эмиттер подключен к базе транзистора 67 и через резистор 68 к общей шине и эмиттеру транзистора 67. Коллектор транзистора 67 соединен с катодом диода 20 и через резистор 69 с шиной питания.

Схема работает следующим образом.

Пусть на входной шине 1 низкий уровень напряжения. Тогда для первого инвертора 6 диод 57 открыт, а транзисторы 54, 52, 39, 37 закрыты, так как отсутствуют токи в их базовых цепях. На базе транзистора 15 при этом установлен высокий уровень напряжения, который выше уровня на шине 3 опорного напряжения, определяемый открытым транзистором 41, прямосмещен- ным диодом 38 и резисторами 42 и 13. Следовательно, для первого элемента 4 задержки транзистор 15 открыт, а транзисторы 16 и 18 закрыты, и на базе транзистора 19 вентильной схемы 2И-2ИЛИ 9 через резистор 11 установлен потенциал общей шины. Для второго инвертора 7 транзисторы 49, 46, 45 открыты, транзистор 43 закрыт, диод 44 обратносмещен и на базе транзистора 21 установлен низкий уровень напряжения, который ниже уровня опорного напряжения. Следовательно, для второго элемента 5 задержки транзистор 22 открыт, а транзисторы 21, 24 закрыты и на базе транзистора 25 через резистор 12 установлен потенциал общей шины. При этом ток от шины питания через резистор 28 поступает в базу транзистора 27, ток резистора 33 через открытый транзистор 27 поступает в

базу транзистора 29 и на выходной шине 2 устанавливается низкий уровень напряжения, определяемый открытым транзистором 29. Времязадающий конденсатор 10 при этом заряжен током открытого транзистора 41. При изменении входного сигнала с низкого уровня на высокий транзисторы 54, 52, 39, 37 в первом инверторе открываются, транзистор 41 в первом инверторе начинает закрываться. Во втором инверторе транзисторы 49,46,45 закрывают, а транзистор 43 начинает открываться. При этом времязада- ющий конденсатор 10 в первый момент времени разряжается сквозными токами, протекающими в выходных цепях первого и второго инверторов. По мере открывания транзистора 43 и нарастания напряжения на его базе еремязадающий конденсатор 10 начинает заряжаться током открытого транзистора 43. Напряжение на базе транзистора 2.1 отслеживает нарастание напряжения на времязадающем конденсаторе 10 и изменяется по экспоненциальному закону (фиг. 2). При этом напряжение на базе транзистора 15 меняется мгновенно, так как база транзистора 15 разряжается через низкоомную цепь коллектор - эмиттер открытого транзистора 37 (фиг. 2). В первом элементе задержки транзистор 15 закрывается, транзисторы 16, 18 открываются, однако напряжение на базе транзистора 19 остается низким благодаря открытому транзистору 67 включённого третьего инвертора 8 и шунтированию базы транзистора 19 по цепи: прямосмещенный диод 20 - коллектор-эмиттер транзистора 67 (фиг. 2). Во втором элементе задержки по достижении на базе транзистора 21 напряжения, равного опорному, происходит открывание транзисторов 21, 24 и закрывание транзистора 22. Время нарастания напряжения на базе транзистора 21 до величины опорного напряжения, равное времени заряда времяза- дающего конденсатора 10 и определяемое его емкостью и резисторами 48, 14, задает время задержки переднего фронта импульса. Ток, протекающий через открытый транзистор 24, создает на резисторе 12 падение напряжения, открывающее транзистор 25 (фиг. 2). Транзистор 27 выключается через открытый транзистор 25 и диод 26. Транзистор 29 выключается через резистор 30 и диод 31, На выходе устанавливается высокий уровень напряжения, определяемый открытыми транзисторами 32. 35 (фиг. 2). При изменений напряжения входного сигнала с высокого уровня на низкий в третьем инверторе диоды 59,60 открываются, а транзисторы 61, 64, 67 закрываются. В первом инверторе транзисторы 54, 52, 39, 37 закрываются, а транзистор 41 открывается. Во вторим инверторе транзисторы 49, 46, 45 открываются, а транзистор 43 закрывается. Времязадающий конденсатор 10 после

кратковременного разряда сквозными токами в выходных цепях первого и второго инверторов заряжается через открытый транзистор 41. Напряжение на базе транзистора 15 отслеживает нарастание напряже0 ния на времязадающем конденсаторе 10 и изменяется по экспоненциальному закону (фиг. 2). При этом напряжение на базе транзистора 21 меняется мгновенно, так как база транзистора 21 разряжается через

5 низкоомную цепь коллектор - эмиттер открытого транзистора 45 (фиг. 2), Во втором элементе задержки транзисторы 21, 24 закрываются, транзистор 22 открывается и на базе транзистора 25 устанавливается по0 тенциал общей шины. В первом элементе задержки по достижении на базе транзистора 15 напряжения, равного опорному, происходит открывание транзистора 15 и закрывание транзисторов 16, 18. Время на5 растания напряжения на базе транзистора 15 до величины опорного напряжения, равное времени заряда времязадающего конденсатора 10 и определяемое его емкостью и резисторами 42, 13, задает время задерж0 ки заднего фронта импульса. Транзистор 19 выключается через резистор 11 и происходит включение транзисторов 27 и 29 и установление на выходе низкого уровня напряжения (фиг. 2). Генераторы 17 и 23

5 тока задают токи в первом и втором элементе задержки соответственно. Резистор 34 предназначен для ограничения сквозного тока на выходе схемы, резистор 36 шунтируют базу транзистора 35. резистор 40 обра0 зует цепь выключения транзистора 37, а резистор 47 образует цепь выключения транзистора 45. Резистор 51 задает ток в коллекторной цепи транзистора 49, резистор 50 образует цепь включения транзисто5 ра 46. Резисторы 53, 56, 58 задают токи в коллекторной цепи транзистора 52, коллекторной цепи транзистора 54 и базовых цепях транзисторов 54, 52 соответственно. Резистор 55 образует цепь выключения

0 транзистора 39. Резисторы 62, 63, 66. 69 задают токи в базовой цепи транзистора 61, коллекторной цепи транзистора 61, коллекторной цепи транзистора 64, коллекторной цепи транзистора 67 соответственно. Рези- 5 стор 65 образует цепь выключения транзистора 64, резистор 68 образует цепь выключения транзистора 67.

На основании вышеизложенной работы Схемы можно сделать вывод о том, что в заявляемом устройстве использован один

времязадающий конденсатор, определяющий время задержки переднего и заднего фронтов импульса, а значит, по сравнению с прототипом достигнуто упрощение схемы и повышение точности задания длительности задержанного импульса. Кроме того, в заявляемом устройстве ток заряда времяза- дающего конденсатора равен току резистора, подключенного к шине питания, минус коллекторный ток открытого транзистора, поступающий в коллектор транзистора через контакт Шоттки. Например, при заряде времязадающего конденсатора 10 через транзистор 41 ток заряда

ic10 1Я42-1кт 11; IR42 1кшт41,

где iR42 - ток, протекающий через резистор 42;

1Кт41 - коллекторный ток транзистора 41; 1Кшт41-ток, протекающий через контакт Шоттки транзистора 41.

Следовательно, по сравнению с прототипом заряд конденсатора одной и той же емкости в заявляемом устройстве происхо- дит медленнее, значит, достигнуто большее время задержки, а значит, и увеличивается диапазон задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линия задержки | 1990 |

|

SU1757091A1 |

| Линия задержки | 1990 |

|

SU1750039A1 |

| Универсальная тиристорная система зажигания | 1990 |

|

SU1781447A1 |

| ЭЛЕКТРОННЫЙ КОРРЕКТОР СИСТЕМЫ ЗАЖИГАНИЯ | 1991 |

|

RU2029883C1 |

| ЭЛЕКТРОННЫЙ ОКТАН-КОРРЕКТОР | 1995 |

|

RU2117818C1 |

| Электронная приставка к транзисторной системе зажигания | 1991 |

|

SU1800086A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| БИПОЛЯРНЫЙ ГЕНЕРАТОР ИОНОВ | 2005 |

|

RU2287744C1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ПЕРЕГРУЗКИ ПО ТОКУ | 1999 |

|

RU2179775C2 |

Использование: в микроэлектронике и вычислительной технике, для замедления скорости передачи данных и обеспечения синхронизации при обмене между подсистемами памяти и процессорными логическими схемами. Целью изобретения является упрощение устройства задержки, повышение точности длительности задержания импульса, увеличение диапазона задержки, Сущность: в устройство, содержащее два элемента задержки и вре- мязадающий конденсатор, введены первый, второй и третий инверторы, вентильная схема 2И-2ИЛИ, первый и второй генераторы тока, первый, второй, третий, четвертый резисторы, шина опорного напряжения. Подключение времязадающего конденсатора к первому и второму инверторам позволяет коммутировать времязадающий конденсатор на каждый фронт импульса поочередно к первому и второму элементам задержки устройства.2 ил.

Формула изобретения

Устройство задержки, содержащее входную и выходную шины, два элемента задержки, времязадающий конденсатор, первый и второй транзисторы, третий, четвертый транзисторы, эмиттеры которых соединены между собой, коллектор третьего транзистора соединен с шиной питания, а его база соединена с коллектором первого транзистора, эмиттер первого транзистора соединен с общей шиной, а его база соединена с эмиттером второго транзистора, эмиттеры пятого и шестого транзисторов соединены между собой, первый вывод времязадающего конденсатора соединен с общей шиной, отличающееся тем, что, с целью упрощения, повышения точности длительности задержанного импульса, увеличения диапазона задержки, введены первый, второй и третий .инверторы, вентильная схема 2И-2ИЛИ, первый и второй p-n-p-транзисторы, первый и второй генераторы тока, первый, второй, третий и четвертый резисторы, шина опорного напряжения, при этом база первого р-п-р- транзистора подключена к коллектору четвертого транзистора, эмиттер первого р- n-p-транзистора соединен с шиной питания, а его коллектор соединен с первым входом схемы 2И, входящей в состав вентильной схемы 2И-2ИЛИ и через первый резистор соединен с общей шиной, второй вход схемы 2И соединен с выходом третьего инвертора, вход которого подключен к входной шине, база второго p-n-p-транзистора соединена с коллектором пятого транзистора, эмиттер второго транзистора соединен с шиной питания, а его коллектор соединен с вторым входом схемы 2ИЛИ, входящей в состав вентильной схемы 2И-2ИЛИ, и через второй резистор соединен с общей шиной, выход вентильной схемы 2И-2ИЛИ подключен к выходной шине, коллектор шестого

транзистора подключен к шине питания, базы четвертого и шестого транзисторов соединены между собой и подключены к шине опорного напряжения, первый генератор тока включен между эмиттерами третьего и четвертого транзисторов и общей шиной, второй генератор тока включен между эмиттерами пятого и шестого транзисторов и общей шиной, база первого транзистора через пятый резистор соединена с общей шиной, база третьего транзистора соединена с катодом первого диода и через третий резистор соединена с общей шиной, анод первого диода соединен с эмиттером седьмого транзистора, база которого соединена с коллектором второго транзистора и через шестой резистор - с шиной питания , коллектор седьмого транзистора соединен с вторым выводом времязадающего конденсатора и коллектором восьмого транзистора, эмиттер восьмого транзистора соединен с анодом второго диода, катод которого подключен к коллектору девятого транзистора, базе пятого транзистора и через четвертый резистор к общей шине, эмиттер девятого транзистора соединен с общей шиной, а его база соединена с эмиттером десятого транзистора и через седьмой резистор соединена с общей шиной, коллектор десятого транзистора соединен с базой восьмого транзистора и через восьмой резистор соединен с шиной питания, база десятого транзистора соединена с эмиттером одиннадцатого транзистора и через девятый резистор соединена с общей шиной, коллектор одиннадцатого транзистора через десятый резистор соединен с шиной питания, а его база соединена с коллектором двенадцатого транзистора и через одиннадцатый резистор соединена с шиной питания, эмиттер двенадцатого резистора соединен с эмиттером тринадцатого транзистора, базой второго транзистора и через двенадцатый резистор - с общей шиной,

коллектор тринадцатого транзистора через тринадцатый резистор соединен с шиной питания, а его база соединена с базой двенадцатого транзистора, анодом третьего

с

.ЈЈЈ

Редактор Б.Федотов

Составитель Н.Мелентьев

Техред М.Моргентал Корректор А.Обручар

диода и через четырнадцатый резистор соединена с шиной питания, катод третьего диода соединен с входной шиной.

А

Вм.2

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1993-02-07—Публикация

1989-02-22—Подача