СО

с

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1993 |

|

RU2065207C1 |

| Ячейка ассоциативной памяти | 1990 |

|

SU1718275A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1805499A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1793475A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| Ассоциативное запоминающее устройство | 1991 |

|

SU1837362A1 |

| ИЕРАРХИЧЕСКАЯ СИСТЕМА АССОЦИАТИВНОЙ ПАМЯТИ | 1992 |

|

RU2025795C1 |

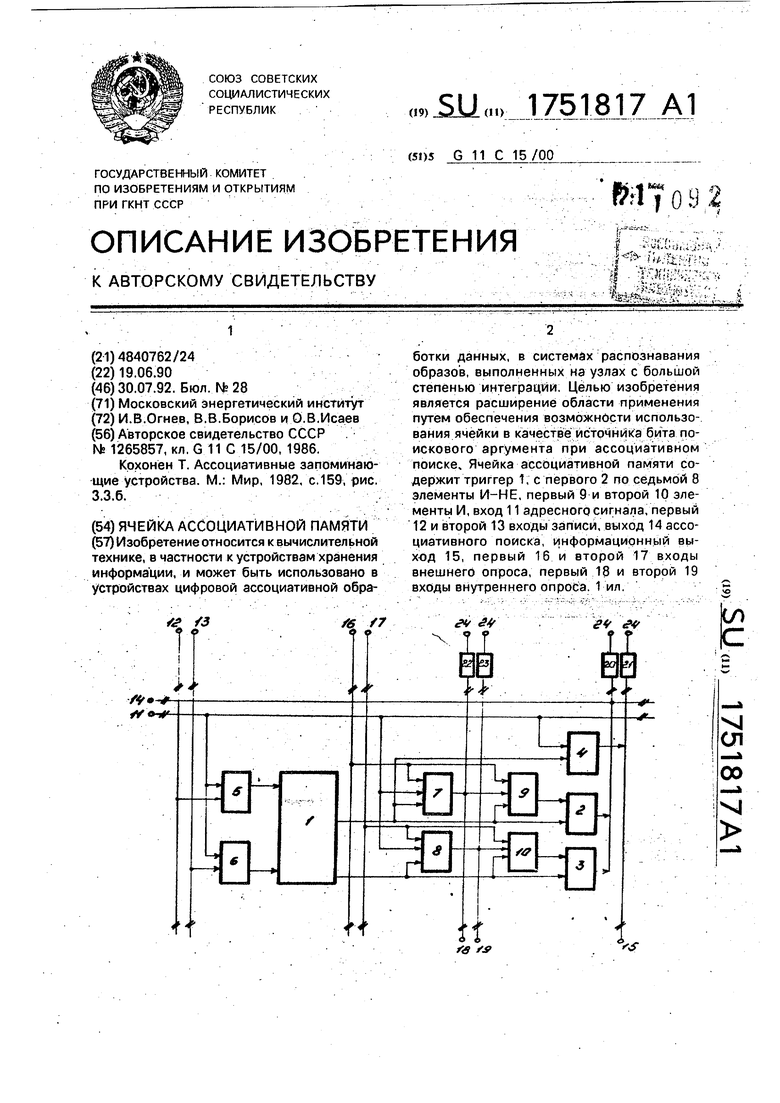

Изобретение относится к вычислительной технике, в частности к устройствам хранения информации, и может быть использовано в устройствах цифровой ассоциативной обработки данных, в системах распознавания образов, выполненных на узлах с большой степенью интеграции Целью изобретения является расширение области применения путем обеспечения возможности использования ячейки в качестве источника бита поискового аргумента при ассоциативном поиске. Ячейка ассоциативной памяти содержит триггер 1, с первого 2 по седьмой 8 элементы И-НЕ, первый 9 и второй 10 элементы И, вход 11 адресного сигнала, первый 12 и второй 13 входы записи, выход 14 ассоциативного поиска, информационный выход 15, первый 16 и второй 17 входы внешнего опроса, первый 18 и второй 19 входы внутреннего опроса 1 ил

XJ ел

00

Изобретение относится к вычислительной технике, в частности к устройствам хранения информации, и может быть использовано в устройствах цифровой ассоциативной обработки данных, в системах распознавания об- разов, выполненных на узлах с большой степенью интеграции.

Известна ячейка ассоциативной памяти, содержащая триггер с первого по пятый элеме нты И-НЕ.

Недостатками указанной ячейки являются усложнение аппаратного обрамления при реализации записи в процессе ассоциативного поиска и невозможность использования ячейки в качестве источника бита поискового аргумента при ассоциативном поиске.

Наиболее близкой по технической сущности к предлагаемой является ячейка ассоциативной памяти, содержащая триггер, с первого по пятый элементы И-НЕ, раздельные адресный вход и выход ассоциативного поиска.

Однако известная ячейка также не может быть использована в качестве источника би- та поискового аргумента при ассоциативном поиске.

Цель изобретения - расширение области применения путем обеспечения возможности использования ячейки в качестве источника бита поисковго аргумента при ассоциативном поиске.

Поставленная цель достигается тем, что в ячейку ассоциативной памяти, содержащую с первого по пятый элементы И-НЕ и триггер, прямой и инверсный выходы которого подключены соответственно к вторым входам первого и второго элементов И-НЕ, выходы которых объединены и являются выходом ассоциативного поиска ячейки ассо- циативной памяти, прямой выход триггера подключен к второму входу третьего элемента И-НЕ, выход которого является информационным выходом ячейки, первые входы третьего, четвертого и пятого элемен- тов И-НЕ объединены и являются адресным входом ячейки, вторые входы четвертого и пятого элементов И-НЕ являются соответственно первым и вторым входами записи ячейки, выходы четвертого и пятого элемен- тов И-НЕ подключены соответственно к входам установки триггера в 1 и О, введены шестой и седьмой элементы И-НЕ, первый и второй элементы И, выходы которых соединены соответственно с первыми входами первого и второго элементов И-НЕ, первые входы которых объединены соответственно с первыми входами шестого и седьмого элементов И-НЕ и являются соответственно первым и вторым входами

внешнего опроса ячейки, вторые входы первого и второго элементов И являются соответственно первым и вторым входами внутреннего опроса ячейки, третьи входы первого и второго элементов И объединены соответственно с третьими входами шестого и седьмого элементов И-НЕ и подключены соответственно, к прямому и инверсному выходам триггера,вторые входы шестого и седьмого элементов И-НЕ объединены и являются адресным входом ячейки, выходы шестого и седьмого элементов И-НЕ являются соответственно первым и вторым выходами внутреннего опроса ячейки

На чертеже представлена схема ячейки ассоциативной памяти, а также связи, позволяющие организовать эти ячейки в ассоциативную запоминающую матрицу

Ячейка ассоциативной памяти содержит RS-триггер 1 с инверсными входами установки в 1 и О, с первого по седьмой элементы И-НЕ 2-8, первый 9 и второй 10 элементы И. Входы установки триггера 1 в 1 и О подключены соответственно к выходам четвертого 5 и пятого 6 элементов И-НЕ, первые входы которых соединены с входом 11 адресного сигнала, а вторые - соответственно с первой 12 и второй 13 шинами записи. Прямой выход триггера 1 подключен к третьим входам шестого элемента И-НЕ 7 и первого элемента И 9, а также к второму входу первого элемента И-НЕ 2, выход которого соединен с выходом второго элемента И-НЕ 3 и шиной 14 ассоциативного поиска. Прямой выход триггера 1 подключен также к второму входу третьего элемента И-НЕ 4, выход которого соединен с информационной шиной 15, а первый вход - с шиной 11 адресного сигнала, подключенной также к вторым входам шестого 7 и седьмого 8 элементов И-НЕ, первые входы которых соединены соответственно с первыми входами первого 9 и второго 10 элементов И и подключены соответственно к первой 16 и второй 17 шинам внешнего опроса, а выходы соответственно подключены к первой 18 и второй 19 шинам внутреннего опроса и присоединены соответственно к вторым входам первого 9 и второго 10 элементов И, выходы которых подключены соответственно к первым входам первого 2 и второго 3 элементов И-НЕ. Второй вход второго элемента И-НЕ 3 соединен с третьими входами седьмого элемента И-НЕ 8 и второго элемента И 10 и подключены к инверсному выходу триггера 1.

Кроме того, шина 14 ассоциативного поиска, информационная шина 15, а также первая 18 и вторая 19 шины внутреннего опроса через ограничительные элементы

20-23, выполненные в виде резисторов, соответственно подключены к шине 24 потенциала логической единицы.

Ячейка ассоциативной памяти работает следующим образом.

В исходном положении триггер 1 установлен в одно из состояний в соответствии со значением бита записанной информации.

Ячейка ассоциативной памяти, кроме хранения бита, позволяет выполнять следующие операции: запись по строке, запись по столбцу, считывание по строке, считывание по столбцу, ассоциативный маскируемый поиск по внешнему поисковому аргументу, ассоциативный маскируемый поиск с использованием ячейки в качестве источника бита поискового аргумента (т.е. ассоциативный маскируемый поиск по внутреннему поисковому аргументу).

Запись по строке реализуется подачей на шину 11 сигнала единичного уровня, а на шины 12 и 13 - сочетания 10 при записи единицы, сочетания 01 при записи нуля и комбинации 00 при маскировании записи. Указанные сигналы подаются на все шины 12 и 13 записи ячеек ассоциативной запоминающей матрицы (не показана).

Запись по столбцу в ячейку памяти осуществляется за два такта. В первом такте записываются только нули,- во втором - только единицы.

Для записи по столбцу нуля в ячейку в первом такте на шины 12 и 13 подается сочетание 01, а на шину 11 этой ячейки - единичный уровень. Если запись нуля в ячейку не производится, на шине 11 этой ячейки сохраняется нулевой потенциал, маскируя запись нуля.

Для записи по столбцу единицы в ячей- ку во втором такте на шины 12 и 13 подается сочетание 10, а на шину 11 этой ячейки - единичный уровень. Если запись единицы в ячейку не производится, на шине 11 этой ячейки сохраняется нулевой потенциал, ма- скируя запись единицы.

Считывание по строке осуществляется выдачей единичного сигнала на шину 11. При этом на выходе элемента И-НЕ формируется сигнал, инверсный биту, хранимому триггером 1. Сигнал поступает на шину 15 и считывается.

Считывание по столбцу реализуется выдачей на шины 16 и 17 сигналов 01, а на шину 11 - нулевого уровня. В этом случае, если триггер 1 установлен в единичное состояние, единичный потенциал сохраняется на выходах элементов И-НЕ 2 и 3 и на шине 14. В противном случае (если триггер 1 установлен в нулевое состояние) на выходе элемента И-НЕ 3 появляется нулевой сигнал который обнуляет шину 14

Ассоциативный маскируемый поиск по внешнему поисковому аргументу осуществляется подачей на шину 11 нулевого потенциала, а на шины 16 и 17 - сочетания сигналов 01 при признаке опроса, равного единице, и сочетания 10 при признака опроса, равного нулю. При этом сигнал единичного уровня сохраняется на шине 14 в случае совпадения признака опроса с бих том, хранимым в ячейке ассоциативной па мяти, и шина 14 обнуляется в противном случае. Маскирование поиска осуществляется подачей нулевого потенциала на шины 16 и 17.

Ассоциативный маскируемый поиск с использованием предлагаемой ячейки в качестве источника бита поискового аргумента реализуется подачей на шину 11 сигнала единичного уровня, а на шины 16 и 17 - сочетания сигналов 11. При этом, если в ячейке-источнике записана единица, обнуляется шина 18, инициируя процесс сравнения с единицей содержимого всех остальных ячеек данного столбца накопителя. В этом случае, если в какой-либо ячейке указанного столбца хранится ноль, выход элемента И-НЕ 3 этой ячейки и шина 14 обнуляются, так как на обоих входах элемента И-НЕ 3 устанавливается уровень логической единицы, если же в ней хранится единица, то ка шине 14 сохраняется единичный потенциал. Если в ячейке-источнике записан ноль, то при подаче сигналов единичного уровня на шины 11, 16 и 17 обнуляется шина 19, инициируя процесс сравнения с нулем содержимого всех остальных ячеек данного столбца накопителя. При этом на шины 11 всех ячеек рассматриваемого столбца, кроме ячейки-источника, подается уровень логического нуля В этом случае, если в какой-либо ячейке указанного столбца хранится ноль, на шине 14, подключенной к выходу ассоциативного поиска этой ячейки, сохраняется сигнал единичного уровня; если же в ней хранится единица, то на выходе элемента И-НЕ 2, а следовательно, и на шине 14 появляется нулевой уровень, так как на обоих входах элемента И-НЕ 2 устанавливается уровень логической единицы. Маскирование ассоциативного поиска в этом режиме осуществляется подачей нулевого потенциала на шины 16 и 17.

Таким образом, предлагаемая ячейка ассоциативной памяти может быть использована в качестве источника бита поискового аргумента при ассоциативном поиске, что расширяет область ее применения

Формула изобретения

Ячейка ассоциативной памяти, содержащая с первого по пятый элементы И-НЕ и триггер, прямой и инверсный выходы которого подключены соответственно к вторым входам первого и второго элементов VI-HE, выходы которых объединены и являются выходом ассоциативного поиска ячейки ассоциативной памяти, прямой выход триггера подключен к второму входу третьего элемента И-НЕ, выход которого является информационным выходом ячейки, первые входы третьего, четвертого и пятого элементов Й-НЕ объединены и являются адресным входом ячейки, вторые входы четвертого и пятого элементов И-НЕ.являются соответственно первым и вторым входами записи ячейки, выходы четвертого и пятого элементов И-НЕ подключены соответственно к входам установки триггера в 1 и О, отличающаяся тем, что, с целью расширения области применения путем обеспечения возможности использования

ячейки в качестве источника бита поискового аргумента при ассоциативном поиске, в ячейку введены шестой и седьмой элементы И-НЕ, первый и второй элементы И, выходы

которых соединены соответственно с первыми входами первого и второго элементов И-НЕ, первые входы которых объединены соответственно с первыми входами шестого и седьмого элементов И-НЕ и являются соответственно первым и вторым входами внешнего опроса ячейки, вторые входы первого и второго элементов И являются соответственно первым и вторым входами внутреннего опроса ячейки, третьи входы

первого и второго элементов И объединены соответственно с третьими входами шестого и седьмого элементов И-НЕ и подключены соответственно к прямому и инверсному выходам триггера, вторые входы шестого и

седьмого элементов И-НЕ объединены и являются адресным входом ячейки, выходы шестого и седьмого элементов И-НЕ являются соответственно первым и вторым входами внутреннего опроса ячейки.

| Элемент памяти ассоциативной запоминающей матрицы | 1985 |

|

SU1265857A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Кохонен Т | |||

| Ассоциативные запоминающие устройства | |||

| М.: Мир, 1982, с | |||

| Катодное реле | 1918 |

|

SU159A1 |

Авторы

Даты

1992-07-30—Публикация

1990-06-19—Подача