Изобретение относится к микроэлектронике и вычислительной технике а именно к схемам линий задержки, широко применяемым для обеспечения синхронизации между электронными системами различного назначения.

Известны линии задержки содержащие входной и выходной буферы а также конденсаторы, индуктивности, резисторы, имитирующие характеристики длинных кабельных линий.

К их недостаткам следует отнести отсутствие возможности регулирования времени задержки, что существенно снижает функциональные возможности данного класса электронных схем.

Наиболее близкой к изобретению является линия задержки, содержащая КМОП- транзисторную схему, времязадающие конденсаторы, компаратор и перемычкРГиз поликристаллического кремния посредством которых времязадающие конденсаторы

подключаются к инвертирующему входу компаратора Для получения требуемого времени задержки осуществляют пережигание лазером перемычек, в результате чего от схемы отсоединяют неиспользуемые времязадающие конденсаторы; а подключенные к схеме времязадающие конденсаторы определяют время задержки

Недостатком данной схемы является отсутствие возможности регулирования времени задержки, так как в результате пережигания лазером перемычек из поликристаллического кремния линия задержки оказывается настроенной на определенное время задержки.

Цель изобретения - расширение функциональных возможностей за счет регулирования времени задержки.

Для этого в линию задержки, содержащую вход, выход, компаратор, времязадаю- щий конденсатор, один вывод которого соединен с инвертирующим входом компаУ

ё

VI ел

„мД

00

со

ю

ратора, а второй с общей шиной, выход компаратора соединен с выходом линии задер жки, введены транзистор,коллектор которого соединен с инвертирующим входом компаратора, эмиттер соединен с общей шиной, база соединена с входом линии задержки, первый резистор, первый вывод которого 5odflnVeH с инвертирующим входом компаратора, а второй с шиной питания, второй резистор, первый вывод которого соединен с шиной питания, диод, анод которого соединен с вторым выводом второго резистора и неинвертирующим входом компаратора, третий перестраиваемый резистор, выполненный из поликристаллического кремния с концентрацией легирующей примеси порядка 101 - 10 см , первый вывод которого соединен с катодом диода и клеммой для подключения источника тока, а второй с общей шиной

Известно использование низкоомных резисторов из поликристаллического кремния с концентрацией легирующей примеси выше 1x10 в электронных схемах, при котором, пропуская через эти резисторы токи плотностью порядка 106 А/см2, получают изменение сопротивления резистора.

Однако в заявляемой линии задержки применяют резисторы из поликристаллического кремния с концентрацией легирующей примеси порядка 10 - 1020 см и токи, изменяющие сопротивление резисторов

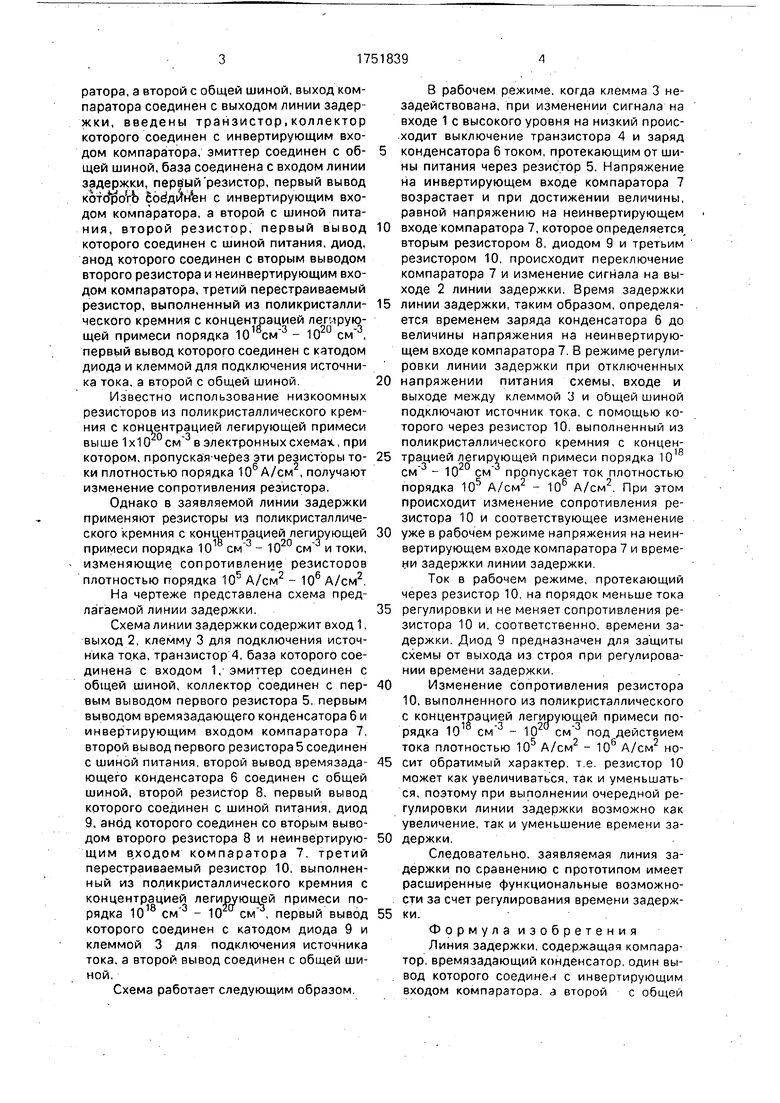

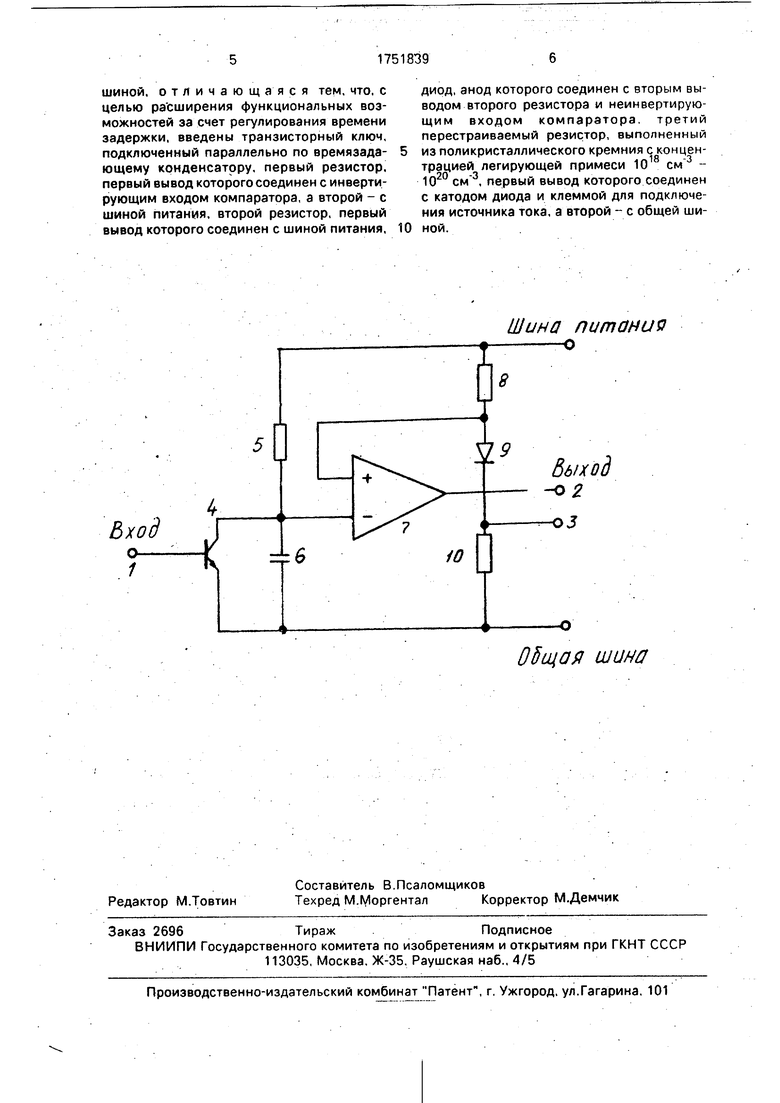

плотностью порядка 105 А/см2 - 10е А/см2 На чертеже представлена схема предлагаемой линии задержки.

Схема линии задержки содержит вход 1, выход 2, клемму 3 для подключения источника тока, транзистор 4, база которого соединена с входом 1, эмиттер соединен с общей шиной, коллектор соединен с первым выводом первого резистора 5, первым выводом времязадающего конденсатора 6 и инвертирующим входом компаратора 7, второй вывод первого резистора 5 соединен с шиной питания, второй вывод времязадающего конденсатора 6 соединен с общей шиной, второй резистор 8, первый вывод которого соединен с шиной питания, диод 9, анод которого соединен со вторым выводом второго резистора 8 и неинвертирующим входом компаратора 7. третий перестраиваемый резистор 10, выполненный из поликристаллического кремния с концентрацией легирующей примеси порядка 1018 - 10 см , первый вывод которого соединен с катодом диода 9 и клеммой 3 для подключения источника тока, а второй вывод соединен с общей шиной.

Схема работает следующим образом

В рабочем режиме, когда клемма 3 незадействована, при изменении сигнала на входе 1 с высокого уровня на низкий происходит выключение транзистора 4 и заряд

конденсатора 6 током, протекающим от шины питания через резистор 5. Напряжение на инвертирующем входе компаратора 7 возрастает и при достижении величины, равной напряжению на неинвертирующем

0 входе компаратора 7, которое определяется, вторым резистором 8, диодом 9 и третьим резистором 10, происходит переключение компаратора 7 и изменение сигнала на выходе 2 линии задержки. Время задержки

5 линии задержки, таким образом, определяется временем заряда конденсатора 6 до величины напряжения на неинвертирующем входе компаратора 7. В режиме регулировки линии задержки при отключенных

0 напряжении питания схемы, входе и выходе между клеммой 3 и общей шиной подключают источник тока, с помощью которого через резистор 10. выполненный из поликристаллического кремния с концен5 трацией легирующей примеси порядка 1018 - 1020 см пропускает ток плотностью порядка 105 А/см2 - 106 А/см2 При этом происходит изменение сопротивления резистора 10 и соответствующее изменение

0 уже в рабочем режиме напряжения на неинвертирующем входе компаратора 7 и времени задержки линии задержки

Ток в рабочем режиме, протекающий через резистор 10, на порядок меньше тока

5 регулировки и не меняет сопротивления резистора 10 и. соответственно, времени задержки. Диод 9 предназначен для защиты схемы от выхода из строя при регулировании времени задержки

0 Изменение сопротивления резистора 10, выполненного из поликристаллического с концентрацией легирующей примеси node -з

рядка 10 см - 10 под действием тока плотностью 105 А/см2 - 106 А/см2 но5 сит обратимый характер, т е резистор 10 может как увеличиваться, так и уменьшаться, поэтому при выполнении очередной регулировки линии задержки возможно как увеличение, так и уменьшение времени за0 держки.

Следовательно, заявляемая линия задержки по сравнению с прототипом имеет расширенные функциональные возможности за счет регулирования времени задерж5 ки.

Формула изобретения Линия задержки, содержащая компаратор, времязадающий конденсатор, один вывод которого соединен с инвертирующим входом компаратора а второй с общей

шиной, отличающаяся тем, что, с целью расширения функциональных возможностей за счет регулирования времени задержки, введены транзисторный ключ, подключенный параллельно по времязада- ющему конденсатору, первый резистор, первый вывод которого соединен с инвертирующим входом компаратора, а второй - с шиной питания, второй резистор, первый вывод которого соединен с шиной питания,

0

диод, анод которого соединен с вторым выводом второго резистора и неинвертирующим входом компаратора, третий перестраиваемый резистор, выполненный из поликристаллического кремния с концентрацией легирующей примеси 1018 - 1020 , первый вывод которого соединен с катодом диода и клеммой для подключения источника тока, а второй - с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНИЯ ЗАДЕРЖКИ | 1991 |

|

RU2019903C1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ПЕРЕГРУЗКИ ПО ТОКУ | 1999 |

|

RU2179775C2 |

| Устройство для управления двухтактным транзисторным преобразователем | 1988 |

|

SU1642563A1 |

| Устройство для установки логических элементов в исходное состояние | 1986 |

|

SU1338047A1 |

| Устройство для управления электромагнитным механизмом | 1982 |

|

SU1081698A1 |

| Импульсный стабилизатор напряжения с защитой от перегрузок по току | 2019 |

|

RU2711138C1 |

| УСТРОЙСТВО ЗАЩИТНОГО ОТКЛЮЧЕНИЯ КОМБИНИРОВАННОЕ | 2000 |

|

RU2214664C2 |

| Устройство для управления двухтактным транзисторным преобразователем | 1988 |

|

SU1713056A1 |

| Устройство для защиты преобразователя | 1983 |

|

SU1127038A2 |

| Стабилизированный преобразователь постоянного напряжения с защитой | 1986 |

|

SU1317597A2 |

Сущность изобретения в линию задержки, содержащую компаратор, времязадаю- щий конденсатор подключенный к 1987-1988, 535-535 инвертирующему входу компаратора, наряду с другими элементами вводят перестраиваемый резистор, выполненный из полмкристаллического кремния с концентрацией легирующей примеси порядка 10 -1020 и задающий напряжение на неинвертирующем входе компаратора В режиме регулировки через резистор из поликристаллического кремния с помощью источника тока пропускают ток плотностью порядка 10S-106 А/см2, что приводит к изменению сопротивления резистора из поликристаллического кремния и в рабочем режиме к изменению напряжения на неинвертирующем входе компаратора. 1 ил.

Шина питания

О

05щая шина

| Data Book Digital Integrated Circuits, 1987, edition 22, p 432 | |||

| Способ приготовления пластического взрывчатого состава | 1913 |

|

SU439A1 |

Авторы

Даты

1992-07-30—Публикация

1990-02-01—Подача