Изобретение относится к полупроводниковой электронике, а более-конкретно к полупроводниковым интегральным схемам на основе комплементарных МОП-транзисторов.

Известна интегральная схема, выполненная на полупроводниковой подложке и содержащая ячейки, включающие р- и п-ка- нальиые МОП-транзисторы, сформированные в полупроводниковых областях п- и р-типов, имеющих геометрию колонок и образующих матрицу.

Недостатком известного устройства является повышение быстродействия при работе на большую нагрузку, связанное с невысокими выходными токами, обуславливающими резкую зависимость быстродействия комплементарных МОП-ячеек от емкости нагрузки.

Указанный недостаток устраняется в интегральной схеме, содержащей ячейки на основе комплементарных МОП-транзисторов с двухтактным выходом на биполярных n-p-п транзисторах, которые позволяют увеличить выходные токи перезаряда емкости нагрузки ячейки, уменьшить зависимость быстродействия от емкости нагрузки и увеличить быстродействие интегральной схемы.

Недостатком известного устройства является пониженная степень интеграции, связанная с необходимостью введения в ячейку дополнительн х биполярных п-р-п- транзисторов, увеличивающих ее площадь.

Наиболее близкой к предлагаемой является интегральная схема, включающая ячейки, содержащие по меньшей мере два п-кэнальных МОП-транзистора, один р-ка- нальный МОП-транзистор, два биполярных n-p-n-транзистора, коллектор одного из которых соединен с шиной питания, один резистор, шины питания, общие шины. Интегральная схема выполнена на полупроводниковой подложке первого типа прово

сл

димости в изолированных диэлектриком полупроводниковых областях со скрытыми слоями первого типа проводимости, в которых сформированы n-канальные МОП-транзисторы, и второго типа проводимости, в которых сформированы р-канальный МОП- трачзистор, резистор и биполярные п-р-п- транзисторы. На Планерной поверхности интегральной схемы сформированы также металлизированные шины питания и общие

ШИНЫ.„ -.

Недостатком этой с5семы является пониженная степень интеграции, связанная с увеличением площади ячейки из-за введения в нее дополнительных элементов (п-р- n-транзисторов, резистора), а также пониженная устойчивость к защелкиванию, связанная с увеличением бросков тока в шинах питания и общих шинах, вызванным увеличением выходных токов ячейки.

Целью изобретения является повышение степени интеграции известной интегральной схемы путем уменьшения площади, занимаемой ячейкой, и повышение устойчивости известной интегральной схемы к защелкиванию.

Указанная цель достигается тем, что в известной интегральной схеме полупроводниковые области с р-канальным МОП-транзистором, резистором и первым n-p-n-транзистором сформированы над общим скрытым слоем второго типа проводимости, выведенном на пленарную поверхность интегральной схемы посредством дополнительной области второго типа проводимости, выполненной под шиной питания и соединен ной с ней, а сопротивление области удовлетворяет соотношению

R

U

прск

lcP / N

(D

1C

..р где Unp.cKp - прямое падение напряжения p-n-перехода сток-карман р-канального МОП-транзистора;

1СР - ток стока р-канального МОП-транзистора;

- коэффициент усиления тока базы первого п-р-п-транзистора.

Полупроводниковые области с п-ка- нальными МОП-транзисторами сформированы под общим скрытым слоем первого типа проводимости, выведенном на планар- иую поверхность интегральной тиристор- ной структуры КМОП элемента, тем самым повышается устойчивость интегральной схемы к защелкиванию.

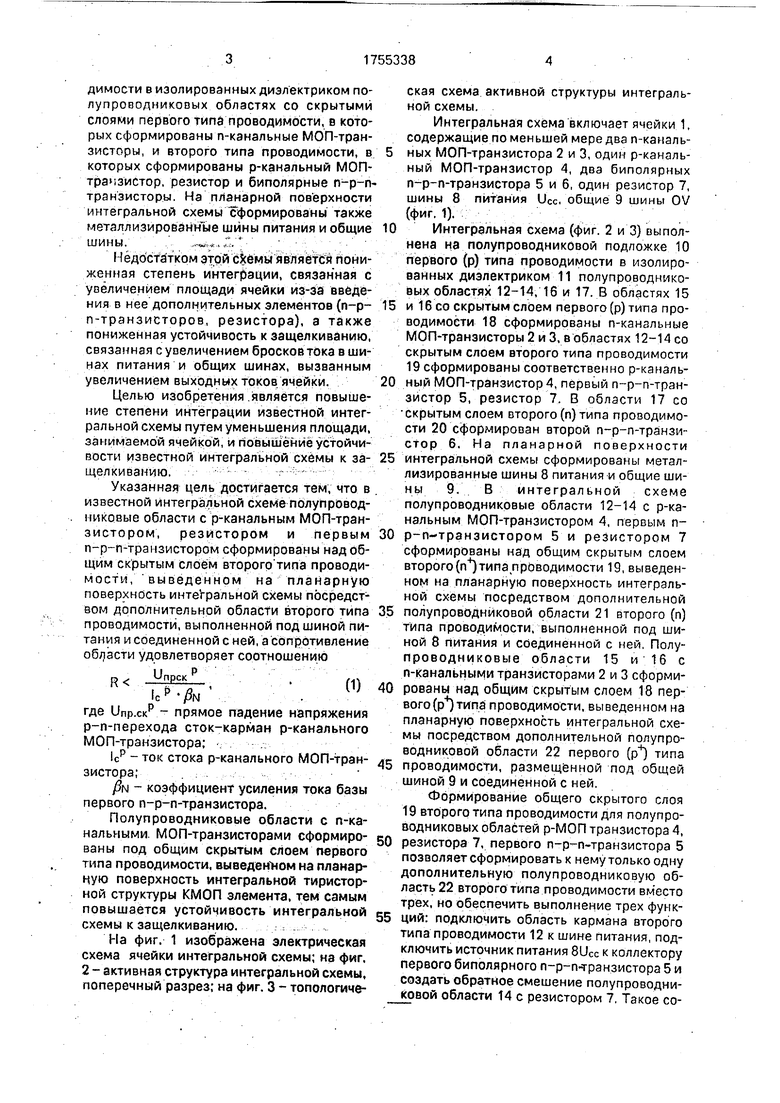

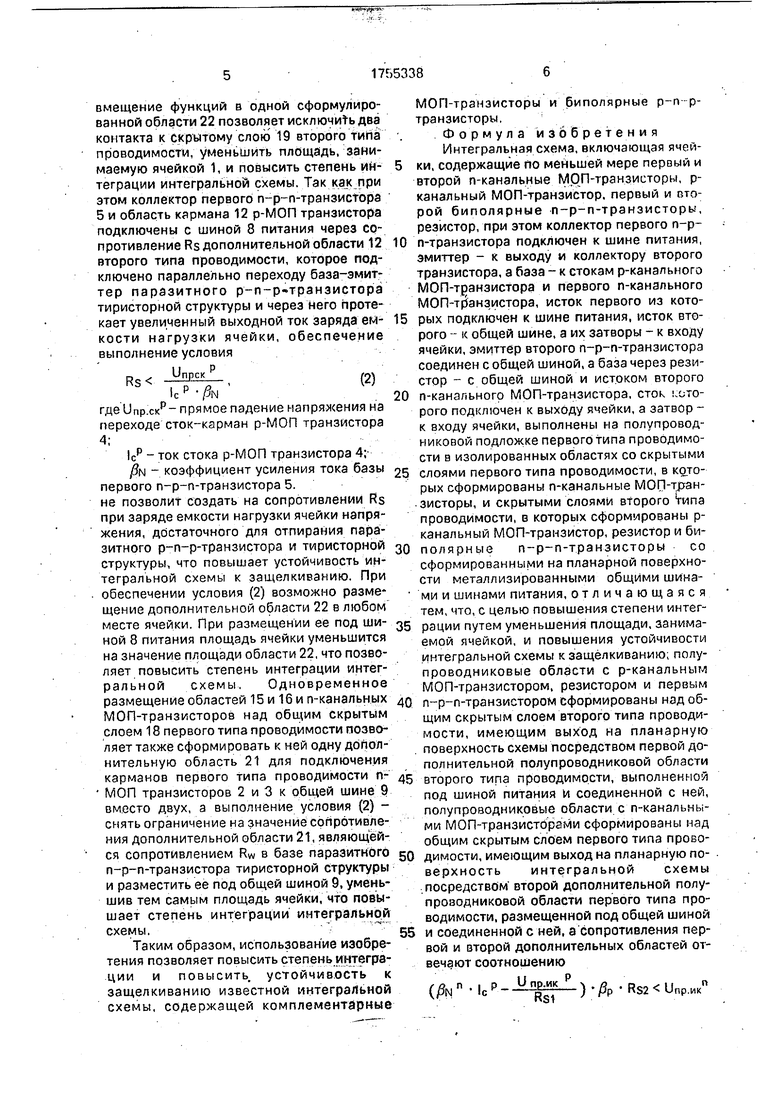

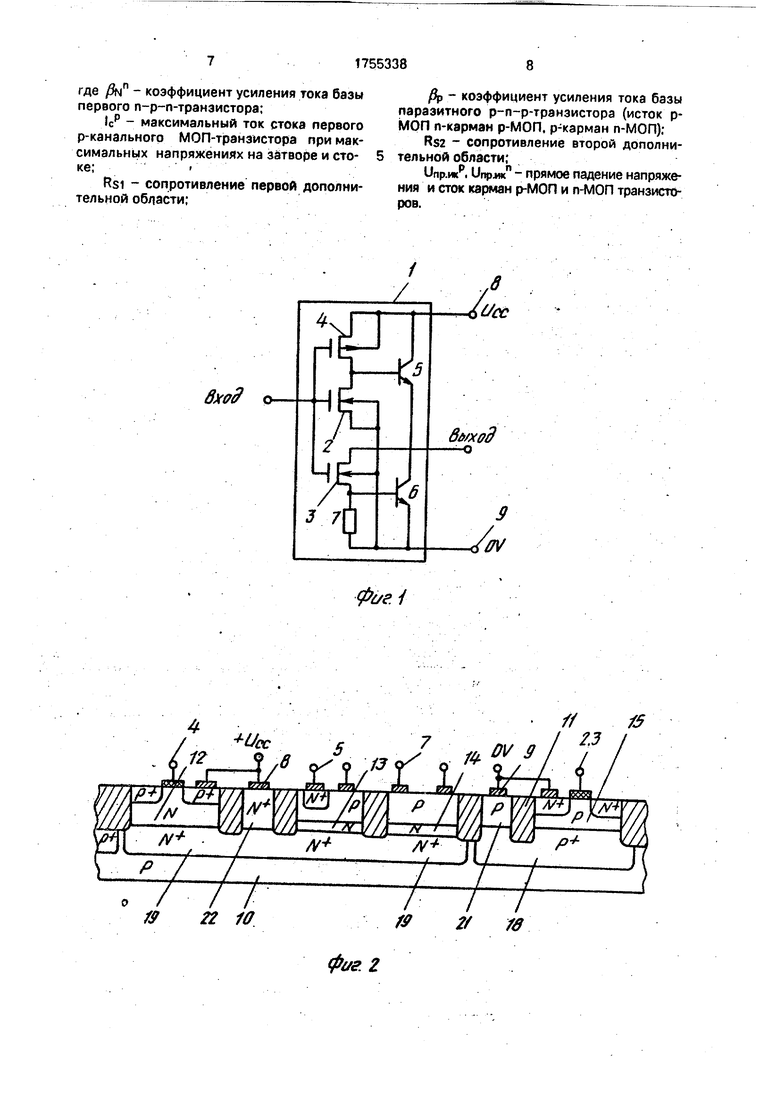

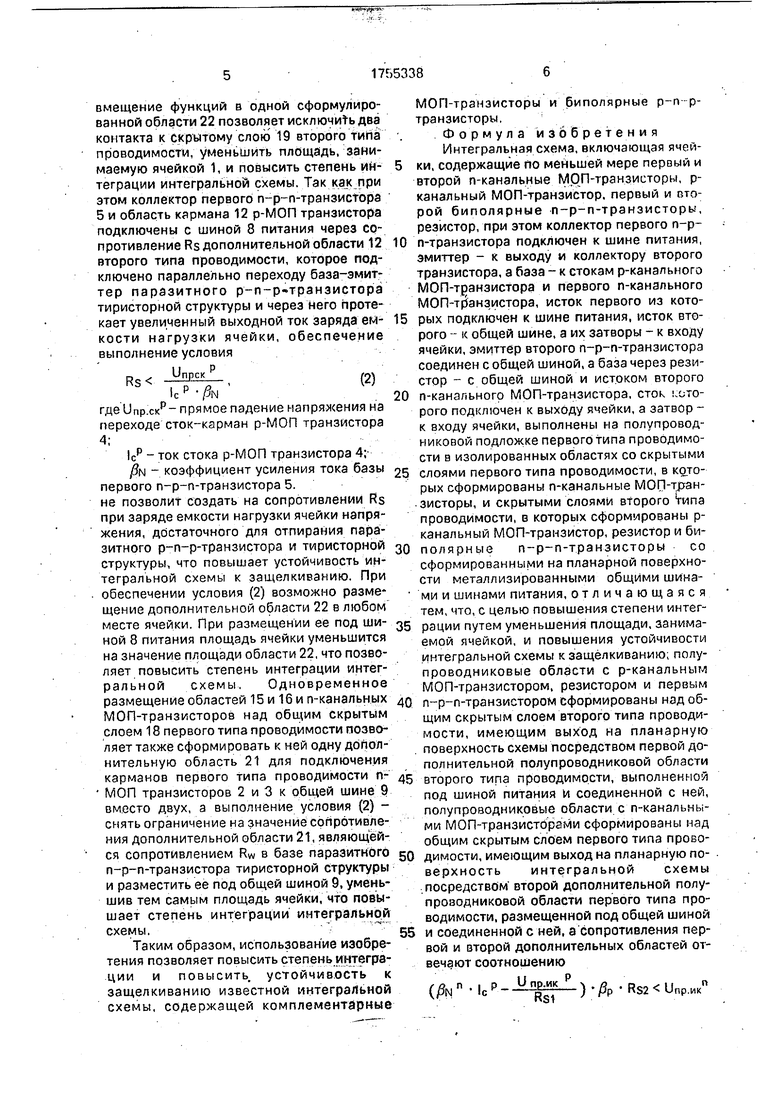

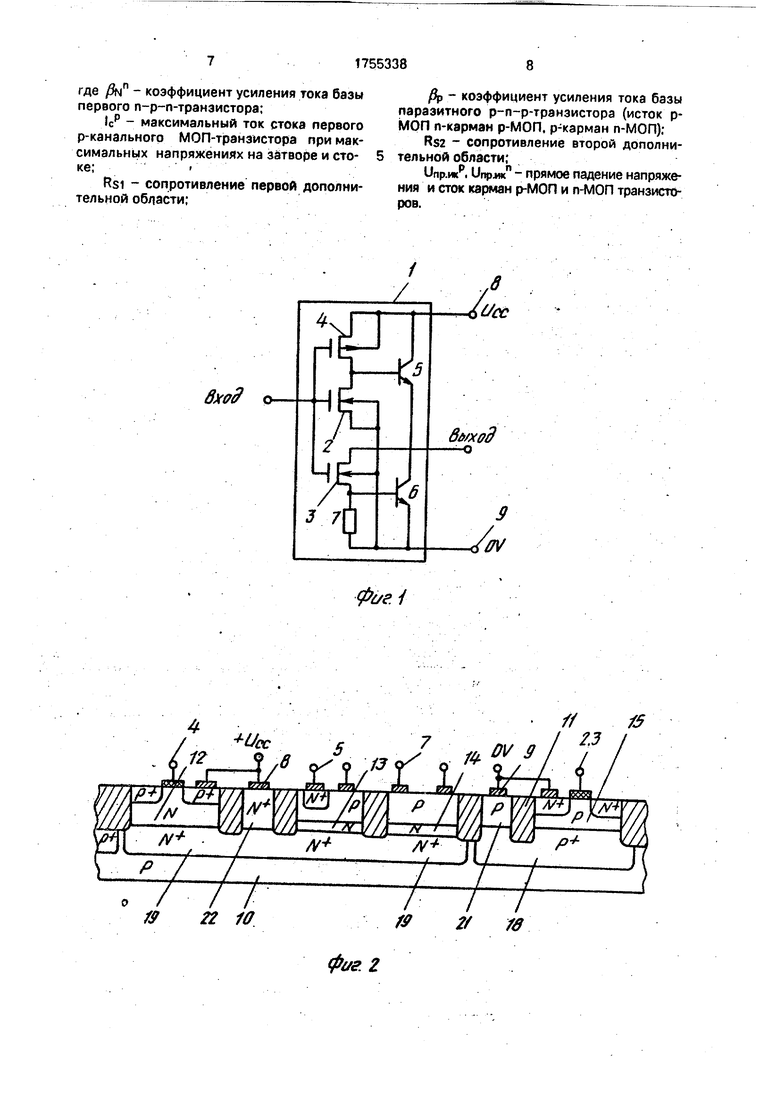

1-1 а фиг. 1 изображена электрическая схема ячейки интегральной схемы; на фиг, 2 - активная структура интегральной схемы, поперечный разрез; на фиг. 3 - топологиче

ская схема активной структуры интегральной схемы.

Интегральная схема включает ячейки 1, содержащие по меньшей мере два п-каналь5 ных МОП-транзистора 2 и 3, один р-канальный МОП-транзистор 4, два биполярных п-р-п-транзистора 5 и б, один резистор 7, шины 8 питания Ucc, общие 9 шины OV (фиг. 1).

10 Интегральная схема (фиг. 2 и 3) выполнена на полупроводниковой подложке 10 первого (р) типа проводимости в изолированных диэлектриком 11 полупроводниковых областях 12-14, 16 и 17. В областях 15

15 и 16 со скрытым слоем первого (р) типа проводимости 18 сформированы п-канальные МОП-транзисторы 2 и 3, в областях 12-14 со скрытым слоем второго типа проводимости 19 сформированы соответственно р-каналь20 ный МОП-транзистор 4, первый п-р-п-тран- зистор 5, резистор 7. В области 17 со скрытым слоем второго (п) типа проводимости 20 сформирован второй п-р-л-транзи- стор 6, На планарной поверхности

25 интегральной схемы сформированы металлизированные шины 8 питания и общие шины 9. В интегральной схеме полупроводниковые области 12-14 с р-канальным МОП-транзистором 4, первым п30 р-п-транзистором 5 и резистором 7 сформированы над общим скрытым слоем второго( .проводимости 19, выведенном на планарную поверхность интегральной схемы посредством дополнительной

35 полупроводниковой области 21 второго (п) типа проводимости, выполненной под шиной 8 питания и соединенной с ней, Полупроводниковые области 15 и 16 с n-канальными транзисторами 2 и 3 сформи40 рованы над общим скрытым слоем 18 первого (р4) типа проводимости, выведенном на планарную поверхность интегральной схемы посредством дополнительной полупроводниковой области 22 первого (р) типа

45 проводимости, размещенной под общей шиной 9 и соединенной с ней.

Формирование общего скрытого слоя 19 второго типа проводимости для полупроводниковых областей р-МОП транзистора 4,

50 резистора 7, первого п-р-п-транзистора 5 позволяет сформировать к нему только одну дополнительную полупроводниковую область 22 второго типа проводимости вместо трех, но обеспечить выполнение трех функ55 ций: подключить область кармана второго типа проводимости 12 к шине питания, подключить источник питания 8UCC к коллектору первого биполярного п-р-п-транзистора 5 и создать обратное смешение полупроводни- крвой области 14 с резистором 7. Такое совмещение функций в одной сформулированной области 22 позволяет исключить два контакта к скрытому слою 19 второго типа проводимости, уменьшить площадь, занимаемую ячейкой 1, и повысить степень интеграции интегральной схемы. Так как при этом коллектор первого п-р-п-транзистора 5 и область кармана 12 р-МОП транзистора подключены с шиной 8 питания через сопротивление RS дополнитепьной области 12 второго типа проводимости, которое подключено параллельно переходу база-эмиттер паразитного р-п-р«транзистора тиристорной структуры и через него протекает увеличенный выходной ток заряда емкости нагрузки ячейки, обеспечение выполнение условия

Rs

U

прск

(2)

Ic P N

где Unp скр- прямое падение напряжения на переходе сток-карман р-МОП транзистора 4;

1СР - ток стока р-МОП транзистора 4;

Дм - коэффициент усиления тока базы первого п-р-п-транзистора 5. не позволит создать на сопротивлении RS при заряде емкости нагрузки ячейки напряжения, достаточного для отпирания паразитного p-n-p-транзистора и тиристорной структуры, что повышает устойчивость интегральной схемы к заи(елкиванию. При обеспечении условия (2) возможно размещение дополнительной области 22 в любом месте ячейки. При размещении ее под шиной 8 питания площадь ячейки уменьшится на значение площади области 22, что позволяет повысить степень интеграции интегральной схемы. Одновременное размещение областей 15 и 16 и п-канальных МОП-транзисторов над общим скрытым слоем 18 первого типа проводимости позволяет также сформировать к ней одну дополнительную область 21 для подключения карманов первого типа проводимости п- МОП транзисторов 2 и 3 к общей шине 9 вместо двух, а выполнение условия (2) - снять ограничение на значение сопротивления дополнительной области 21, являющейся сопротивлением Rw в базе паразитного n-p-n-транзистора тиристорной структуры и разместить ее под общей шиной 9, уменьшив тем самым площадь ячейки, что повышает степень интеграции интегральной схемы.

Таким образом, использование изобретения позволяет повысить степень интеграции и повысить, устойчивость к защелкиванию известной интегральной схемы, содержащей комплементарные

МОП-транзисторы и биполярные р-n р- транзисторы.

Формула изобретения Интегральная схема, включающая ячей5 ки, содержащие по меньшей мере первый и второй n-канэльные МОП-транзисторы, р- канальный МОП-транзистор, первый и второй биполярные п-р-п-транзисторы, резистор, при этом коллектор первого п-р10 n-транзистора подключен к шине питания, эмиттер - к выходу и коллектору второго транзистора, а база - к стокам р-канального МОП-транзистора и первого п-канального МОП-транзистора, исток первого из кото15 рых подключен к шине питания, исток второго - к общей шине, а их затворы - к входу ячейки, эмиттер второго п-р-п-транзистора соединен с общей шиной, а база через резистор - с общей шиной и истоком второго

20 п-канального МОП-транзистора, сток второго подключен к выходу ячейки, а затвор - к входу ячейки, выполнены на полупроводниковой подложке первого типа проводимости в изолированных областях со скрытыми

25 слоями первого типа проводимости, в которых сформированы n-канальные МОП-транзисторы, и скрытыми слоями второго типа проводимости, в которых сформированы р- канальный МОП-транзистор, резистор и би30 полярные n-p-n-транзисторы со сформированными на планэрной поверхности металлизированными общими шинами и шинами питания, отличающаяся тем, что, с целью повышения степени интег35 рации путем уменьшения площади, занимаемой ячейкой, и повышения устойчивости интегральной схемы к защелкиванию, полупроводниковые области с р-канальным МОП-транзистором, резистором и первым

40 n-p-n-транзистором сформированы над общим скрытым слоем второго типа проводимости, имеющим выход на пленарную поверхность схемы посредством первой дополнительной полупроводниковой области

45 второго типа проводимости, выполненной под шиной питания и соединенной с ней, полупроводниковые области с п-канальны- ми МОП-транзисторами сформированы над общим скрытым слоем первого типа прово50 димости, имеющим выход на пленарную поверхность интегральной схемы посредством второй дополнительной полупроводниковой области первого типа проводимости, размещенной под общей шиной

55 и соединенной с ней. а сопротивления первой и второй дополнительных областей oi- вечают соотношению

(/ Nn4cP--)-/VRS2 UnPHKn

где /3№ - коэффициент усиления тока базы первого п-р-п-транэистора;

1СР - максимальный ток стока первого р-канального МОП-транзистора при максимальных напряжениях на затворе и стоке;

RSI - сопротивление первой дополнительной области;

/Зр - коэффициент усиления тока базы паразитного p-n-p-транзистора (исток р- МОП n-карман р-МОП. р-карман п-МОП);

Rsa - сопротивление второй дополни- тельной области;

Unp.ncp, Unp.wcn - прямое падение напряжения и сток карман р-МОП и n-МОП транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральная схема | 1988 |

|

SU1589957A1 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ ПИТАНИЯ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КРЕМНИЕВЫХ ПЛАСТИНАХ С ПРОВОДИМОСТЬЮ N-ТИПА | 2013 |

|

RU2585882C2 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| ИНТЕГРАЛЬНАЯ СТРУКТУРА ДЛЯ БИС | 1992 |

|

RU2084989C1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| ЕМКОСТНАЯ МОП ДИОДНАЯ ЯЧЕЙКА ФОТОПРИЕМНИКА-ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2014 |

|

RU2583955C1 |

| БИКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1996 |

|

RU2106719C1 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

Изобретение относится к цифровым интегральным схемам на основе комплементарных МОП-транзисторов. Изобретение позволяет повысить степень интеграции и устойчивость к -защелкиванию интегральных схем, содержащих комплементарные МОП-транзисторы и биполярные п-р-п- транзисторы. В предложенной интегральной схеме повышение степени интеграции и устойчивости к защелкиванию достигается формированием общего скрытого слоя второго типа проводимости, соединенного с шиной питания с помощью одной дополнительной области второго типа проводимости, для р-канального МОП-транзистора, первого n-p-n-транзистора, резистора, и формированием общего скрытого слоя первого типа проводимости, соединенного с общей шиной с помощью дополнительной области первого типа проводимости для р- канальных МОП -транзисторов и за счет мзо- ляции элементов диэлектрическими областями. 3 ил. .

вХ90

/ / I ff 22 1О

фиг. 2

five.i

2/ в

в Я

ФигЭ

| Патент США № 4651190, кл.Н01 L 27/10, 1987, Авторское свидетельство СССР № 1347181,кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1992-08-15—Публикация

1989-07-26—Подача