Изобретение относится к наноэлектронике и может быть использована при изготовлении оперативного запоминающего устройства с произвольной выборкой информации (ДОЗУ ПВ) с повышенной надежностью и быстродействием.

Известные ячейки памяти для ДОЗУ ПВ представляют собой функционально-интегрированные структуры, в которые совмещены ключевой МОП транзистор, запоминающий конденсатор, адресная и разрядная шины (1, 2, 3). Такие ячейки памяти содержат весьма малый информационный заряд в запоминающем конденсаторе, что приводит к малой величине информационного сигнала на разрядной шине из-за большой паразитной емкости, которую она содержит, а также большому времени установления информационного сигнала на разрядной шине.

Наиболее близкими по технической сущности является ячейка памяти ДОЗУ ПВ, содержащая ключевой n(p) - канальный МОП транзистор, исток которого подключен к первому выводу запоминающего конденсатора, сток МОП транзистора подключен к разрядной шине, а затвор к адресной шине, второй вывод запоминающего конденсатора подключен к общей шине (Z) питания.

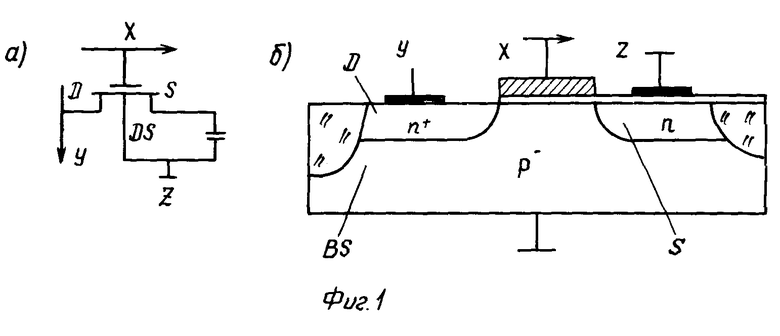

Техническим эффектом данного изобретения является повышение надежности и быстродействия ДОЗУ ПВ. Указанные эффекты достигаются тем, что ячейка памяти ДОЗУ ПВ содержит дополнительные n-р-n (р-n-р) и биполярный n-р-n (р-n-р)-транзистор и резистор, при этом коллектор биполярного транзистора совмещен с подзатворной областью канала МОП транзистора, база с областью стока МОП транзистора, эмиттер соединен с разрядной шиной и первым выводом нелинейного резистора, второй вывод которого соединен с базой биполярного транзистора и стоком МОП транзистора.

Основным обстоятельством является то, что биполярный n-р-n (р-n-р)-транзистор и резистор функционально-интегрированны с МОП транзистором (см. фиг. 2б), т.е. область коллектора n-(р-) типа биполярного транзистора одновременно является подзатворной областью МОП транзистора, а его область базы является областью стока МОП транзистора, область активной базы р-(n-) транзистора, заключенная между n+(р+) областью эмиттера и n-(р-) областью коллектора биполярного транзистора, является нелинейным резистором, область пассивной p+(n+) базы n+(p+) эмиттера соединены с разрядной шиной.

Эквивалентная схема ячеек памяти ДОЗУ ПВ

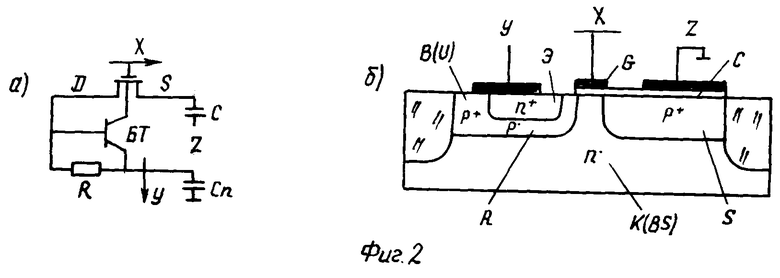

На фиг. 1а показана эквивалентная схема простейшей ячейки памяти ДОЗУ ПВ, которая содержит МОП транзистор, исток (S) которого соединен с первым выводом конденсатора (С), второй вывод которого соединен с общей шиной (Z), сток (D) соединен с разрядной шиной (У), подзатворная область (BS) с общей шиной (Z), а затвор с адресной шиной (X).

На фиг. 1б, показана структура простейшей ячейки памяти ДОЗУ ПВ, в которой барьерная емкость истокового р-n перехода (S) образует запоминающий конденсатор (С) с подзатворной емкостью (BS) и общей шиной (Z), область стока (D) соединена с разрядной шиной (У), а затвор (G) соединен с адресной шиной (X).

На фиг. 2а показана эквивалентная схема предлагаемой ячейки памяти ДОЗУ ПВ, которая содержит МОП транзистор, исток (S) которого соединен с первым выводом конденсатора (С), второй вывод которого соединен с общей шиной (Z), коллектор (К) биполярного транзистора, исток (D) МОП транзистора соединен с базой (Б) биполярного транзистора и первым выводом регистора (R), второй вывод резистора (R) соединен с эмиттером биполярного транзистора и разрядной шиной (У).

На фиг. 2б показана структура предлагаемой ячейки памяти ДОЗУ ПВ, в которой барьерная емкость истокового р-n перехода (S) образует запоминающий конденсатор (С) с подзатворной областью (BS), которая одновременно является областью коллектора (К) биполярного n-р-n транзистора, область базы (Б) которого одновременно является областью стока (D) МОП транзистора, при этом область активной базы (р-) n-р-n транзистора образует нелинейный резистор (R), область пассивной базы (р+) и область эмиттера (n+) биполярного транзистора, находящаяся в области базы (Б), соединены с разрядной шиной (У). Подзатворная область (BS) образована подложкой.

Динамическая ячейка ДОЗУ ПВ работает следующим образом:

В режиме записи информации в ячейку ДОЗУ ПВ на адресную шину (X) и соответственно затвор (G) подается отрицательный потенциал относительно подзатворной области (BS) и передвигающее пороговое напряжение (Vo) - МОП-транзистора. При этом на разрядную шину (Y) подается потенциал, соответствующий состоянию логикой "0" (низкий потенциал относительно шины Z), или потенциал, соответствующий состоянию логической "1" (нулевой потенциал относительно шины Z). В результате этого МОП транзистор открывается и запоминающий конденсатор (С) заряжается через сопротивление (R) потенциалом, имеющимися в данный момент времени на разрядной шине (У).

В режиме считывания информации на разрядную шину Z подается отрицательный (низкий) потенциал и в случае наличия в конденсаторе высокого (нулевого) потенциала относительно общей линии (2), соответствующего состоянию логикой "1", через инверсионный канал МОП транзистора и через базу биполярного р-n-р транзистора пропускает ток зарядки запоминающего конденсатора. Этот ток усиливается биполярным транзистором на величину, равную его коэффициенту усиления тока базы (h12э ~ 100). Таким образом увеличивается токовый информационный сигнал на разрешенной шине, что увеличивает надежность работы ДОЗУ ПВ. Важно, что при этом время зарядки паразитной емкости (Сn) информационной шины также уменьшается в h12э раз, что повышает в соответствующее число раз быстродействие ДОЗУ ПВ. В случае отрицательного потенциала на конденсаторе (С) ток базы через n-р-n транзистор не проходит и потенциал разрядной шины определяется паразитной емкостью (Сn). В режиме хранения информации на затвор (G) МОП транзистора подается нулевой потенциал, что соответствует его закрытому состоянию.

Предлагаемая ячейка памяти и ДОЗУ ПВ на его основе, как это видно из фиг.2б, могут быть легко реализованы по стандартной КМОП технологии, которую применяют при производстве ДОЗУ ПВ. Следует отметить, что повышение надежности и быстродействия ДОЗУ ПВ в ~ h12э раз достигается почти без увеличения площади ячейки памяти ДОЗУ ПВ.

Источники информации

1. Matsue S, Vamamoto H, Kobayski К, еt al. A 256 Кбит dymamia RAM IEEE. J. 1980.V sc-15. N5, p.872-874.

2. Rideout V. L. One-device alls for dynamic random-access memories; a tutorial-IEEE, 1979, v. ED-26, N6, p.839-862.

3. US Patent 3387286, Dennard R. H., Field-effect transistor memory application filed July 14, 1967, granted June 4, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| ДИНАМИЧЕСКОЕ ПОСЛЕДОВАТЕЛЬНОЕ ФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО | 2005 |

|

RU2392672C2 |

| КООРДИНАТНЫЙ ДЕТЕКТОР РЕЛЯТИВИСТСКИХ ЧАСТИЦ | 2000 |

|

RU2197036C2 |

| ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ | 1997 |

|

RU2147772C1 |

| Ячейка памяти статического оперативного запоминающего устройства с радиоактивным источником питания | 2021 |

|

RU2777553C1 |

| ГАЗОЧУВСТВИТЕЛЬНЫЙ ДАТЧИК | 2000 |

|

RU2196981C2 |

| ЕМКОСТНАЯ МОП ДИОДНАЯ ЯЧЕЙКА ФОТОПРИЕМНИКА-ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2014 |

|

RU2583955C1 |

Изобретение относится к наноэлектронике. Его использование при создании динамического оперативного запоминающего устройства с произвольной выборкой информации (ДОЗУ ПВ) позволяет получить технический результат в виде повышения надежности работы и быстродействия ячейки памяти за счет введения в ее схему биполярного транзистора (БТ) и нелинейного резистора (R), что позволяет усиливать информационный сигнал и, тем самым, позволяет быстрее перезаряжать паразитную емкость Сп разрядной шины Y. Ячейка памяти является функционально-интегрированным элементом, в котором область коллектора биполярного транзистора (БТ) одновременно является подзатворной областью MOSFET транзистора, область стока (D) MOSFET транзистора образует область базы (В) биполярного транзистора, а резистор (R) образуется за счет квазинейтральной части активной области базы р- биполярного транзистора. В результате функциональной интеграции в единую конструкцию MOSFET и БТ транзисторов и резистора реализуется конструкция ячейки памяти по топологическому размеру и технологии изготовления, аналогичная однотранзисторной ячейке памяти ДОЗУ ПВ. 2 с.п.ф-лы, 2 ил.

| US 3387286 А, 04.06.1968 | |||

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2032944C1 |

| US 4309716 А, 05.01.1982 | |||

| Стенд для исследований зубчатых и шлицевых соединений | 1975 |

|

SU601590A1 |

| Жидкостной огнетушитель | 1981 |

|

SU971360A1 |

| Роторная мельница | 1982 |

|

SU1049101A1 |

| Ячейка памяти | 1973 |

|

SU483710A1 |

| Ячейка памяти | 1981 |

|

SU1275545A1 |

Авторы

Даты

2003-11-20—Публикация

2001-02-27—Подача