Изобретение относится к измерительной технике и может быть использовано для проверки преобразователей фаза-код.

Известно устройство для поверки цифровых приборов, которое также можно использовать и для поверки преобразователей фаза-код, содержащее источник эталонного сигнала, модулятор, клеммы для подключения поверяемого прибора, блок вычитания кодов, блок регистрации, генератор тактовых импульсов, реверсивный счетчик импульсов, дешифратор, триггер реверса, первый и второй элементы И, управляемый делитель частоты, синхронный делитель частоты,источник логического сигнала и три переключателя.

Однако известное устройство не обеспечивает достоверной поверки преобразователей фаза-код во всех реальных режимах их работы, а использование в данном устройстве в качестве модулятора дискретных или цифровых кодоуправляемых фазовращателей приводит в первом случае к затруднению получения воспроизводимого фазового сдвига с высокой точностью и стабильностью, а во втором случае к нарушению работоспособности поверяемого преобразователя фаза-код при переходе значения воспроизводимого фазового сдвига через 0°. Кроме того, известное устройство обеспечивает или вычисление погрешности измерения фазового сдвига поверяемого преобразователя в статическом режиме, или вычисление погрешности измерения скорости изменения фазы при поверке преобразователей фаза-код, дополнительно измеряющих этот параметр, в динамическом режиме. Вычисление же погрешности измерения фазового сдвига в динамическом режиме известное устройство не обеспечивает.

Наиболее близким по технической сущности к изобретению является устройство для поверки цифровых приборов, которое содержит преобразователь частоты, модулятор, клеммы для подключения поверяемого прибора, блок вычитания кодов, блок регистрации, генератор тактовых импульсов, реверсивный счетчик импульсов, дешифратор, триггер реверса, первый и второй элементы И, управляемый делитель частоты, синхронный делитель частоты, источник логического сигнала, три переключателя, блок коммутации и два формирователя коротких импульсов. В этом устройстве вход блока регистрации соединен с выходом блока вычитания кодов, первый вход которого соединен с клеммами для подключения выхода поверяемого прибора, клемма для подключения входа которого соединена с

выходом модулятора, вход которого подключен к выходу преобразователя частоты, к клемме для подключения опорного входа поверяемого прибора и через первый формирователь коротких импульсов к входу управления блока коммутации. Выход реверсивного счетчика импульсов соединен с входом блока коммутации, входом дешифратора и через первый переключатель - с

0 первым входом триггера реверса, второй вход которого соединен с выходом дешифратора и через второй формирователь коротких импульсов с установочными входами преобразователя частоты, управляемого де5 лителя частоты и синхронного делителя частоты, прямой выход - с первым входом первого элемента И, а инверсный выход - с первым входом второго элемента И. Вторые входы элементов И через второй переклю0 чатель, синхронный делтель частоты и управляемый делитель частоты подключены к выходу генератора тактовых импульсов и входу преобразователя частоты, а выходы - к входам суммирования и вычитания ревер5 сивного счетчика импульсов соответственно. Выход источника логического сигнала через третий переключатель подключен к второму входу блока вычитания кодов. Выход блока коммутации подключен к управля0 ющему входу модулятора.

Однако это устройство также не обеспечивает достоверную поверку преобразователя фаза-код во всех реальных режимах их работы в составе фазовых преобразовате5 лей угла, нарушает работу поверяемых преобразователей при переходе убывающей фазы сигнала через нулевое значение в динамическом режиме работы и не обеспечивает вычисление погрешности измерения

0 фазового сдвига в динамическом режиме работы устройства.

Целью изобретения является расширение функциональных возможностей и повышение достоверности поверки за счет

5 имитации двухтактного (калибровка - измерение) режима работы преобразователя фаза-код, входящего в состав фазового преобразователя угла, определения погрешности в динамическом режиме работы

0 и устранения нарушения работоспособности поверяемого преобразователя фаза-код при переходе значения воспроизводимого убывающего фазового сдвига в динамическом режиме через 0°.

5 Поставленная цель достигается тем, что в известное устройство для проверки преобразователей фаза-код, содержащее генератор тактовых импульсов, управляемый делитель частоты, вход которого подключен к выходу генератора тактовых импульсов,

дешифратор, первый управляемый фазовращатель, счетчик, первый блок коммутации, блок вычитания, блок регистрации, вход которого подключен к выходу блока вычитания, первый, второй и третий переключатели, источник логического сигнала, выход которого подключен к входу второго переключателя, формирователь коротких импульсов, вход и выход которого подключены соответственно к выходу дешифратора и установочному входу управляемого делителя частоты, выход которого через первый переключатель соединен с тактовым входом счетчика, выход счетчика подключен к входу дешифратора и входу первого блока коммутации, первый выход которого подключен к управляющему входу первого управляемого фазовращателя, преобразователь частоты, выход которого соединен с первой клеммой для подключения поверяемого преобразователя, а тактовый и установочный входы подключены соответственно к выходу генератора тактовых импульсов и выходу форми- рователя коротких импульсов, вторые клеммы для подключения поверяемого преобразователя, поразрядно соединенные с первым входом блока вычитания, третью клемму для подключения поверяемого преобразователя, введены второй и третий управляемые фазовращатели, строоируемый формирователь импульсов, второй блок коммутации, четвертая и пятая клеммы для подключения поверяемого преобразователя, импульсный коммутатор, управляющий вход и выход которого соединены соответственно с четвертой и третьей клеммами для подключения поверяемого преобразователя, пятая клемма для подключения поверяемого преобразователя соединена со стробирующим входом второго блока коммутации, первый вход которого подключен к выходу счетчика, второй вход второго блока коммутации соединен с выходами второго переключателя, а выход подключен к второму входу блока вычитания, выход второго управляемого фазовращателя подключен к входу управления первого блока коммутации, входам первого и третьего управляемых фазовращателей и стробирую- щему входу стробируемого формирователя импульсов, кодовый вход которого соединен с входом дешифратора, а тактовый вход и выход подключены соответственно к выходу генератора тактовых импульсов и третьему входу импульсного коммутатора, тактовые входы первого, второго, третьего управляемого фазовращателя и преобразователя частоты объединены, выходы первого и третьего управляемого фазовращателей соединены соответственно с вторым и первым входами импульсного коммутатора, управляющий вход третьего управляемого фазовращателя соединен с вторым выходом первого блока коммутации, выход источника логического сигнала соединен через четвертый переключатель с установочным входом счетчика и через третий переключатель с управляющим входом второго управляемого фазовращателя, вход ко0 торого подключен к выходу преобразователя частоты.

Второй блок коммутации содержит N D-триггеров, D-входы которых подключены к первому входу второго блока коммутации,

5 а С-входы - к стробирующему входу второго блока коммутации, N элементов И-ИЛИ, у которых выходы соединены с выходом второго блока коммутации, первые входы - с выходами D-триггеров, вторые входы - с

0 вторым входом второго блока коммутации, третьи входы объединены и подключены к нормально змакнутому контакту переключателя, а четвертые входы объединены и подключены к нормально разомкнутому

5 контакту переключателя, подвижный контакт которого соединен с источником логического нуля.

Импульсный коммутатор содержит элемент И-ИЛИ, первый, второй и третий вхо0 ды которого соединены соответственно с первым, вторым и третьим входами импульсного коммутатора и элемент НЕ, выход которого подключен к четвертому входу элемента И-ИЛИ, а вход- к управляющему

5 входу ипульсного коммутатора и к пятому и шестому входам элемента И-ИЛИ, выход которого соединен с выходом импульсного коммутатора.

Оробируемый формирователь импуль0 сов содержит элемент И, входы которого подключены к кодовому входу сгробируемо- го формирователя импульсов, а выход - к Овходу первого триггера, второй триггер, С-эход которого связан со стробирующим

5 чходом стробируемого формирователя импульсов, D-вход - с выходом первого триггера, счетчик, С-вход которого подключен к тактовому входу стробируемого формирователя импульсов, R-вход - к выходу

0 второго триггера и выходу стробируемого формирователя импульсов, а выход объединен с R-входами первого и второго триггеров.

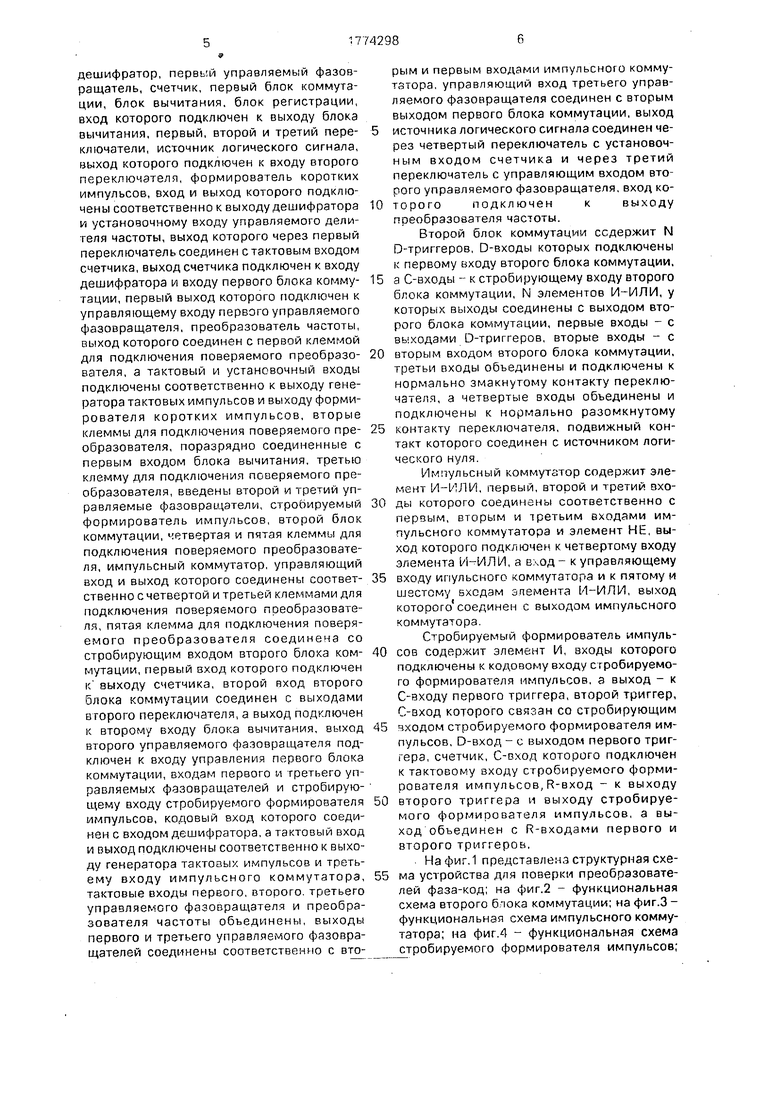

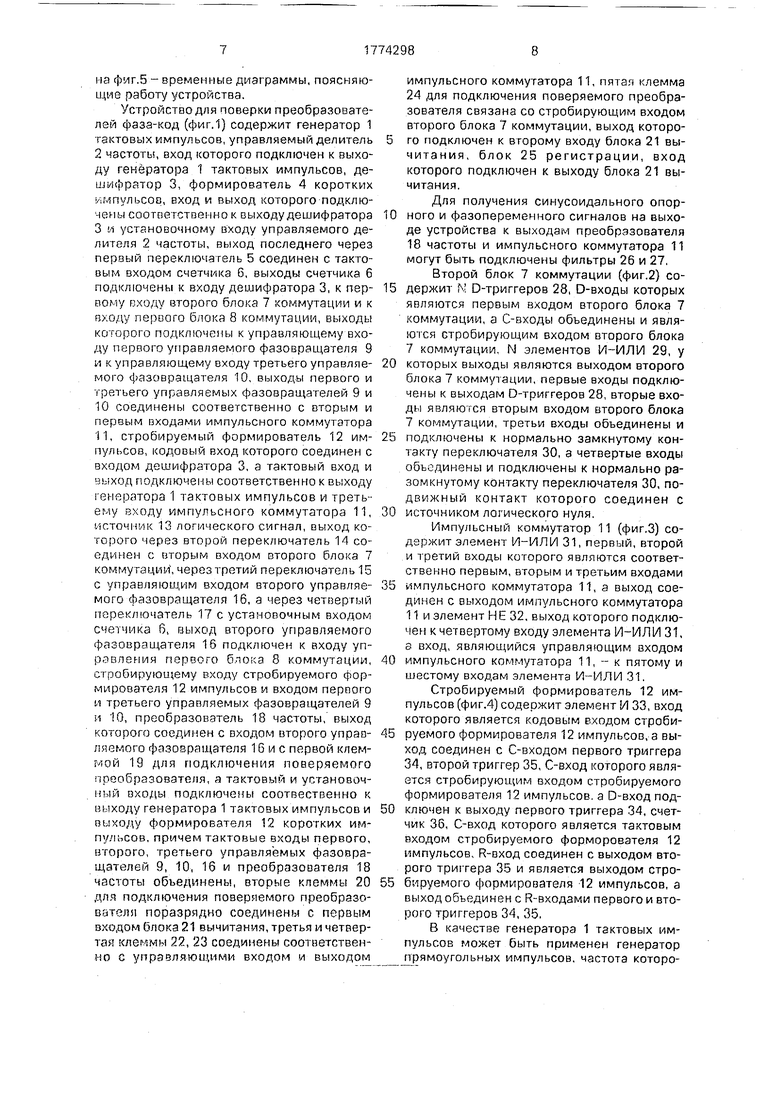

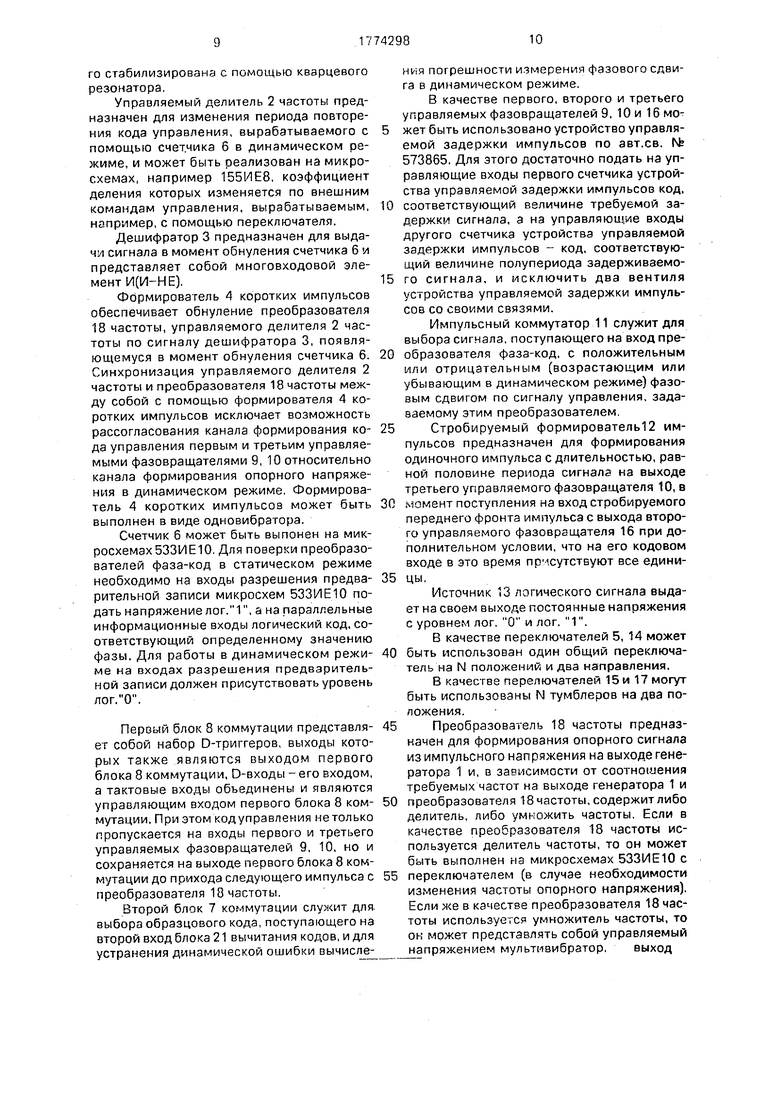

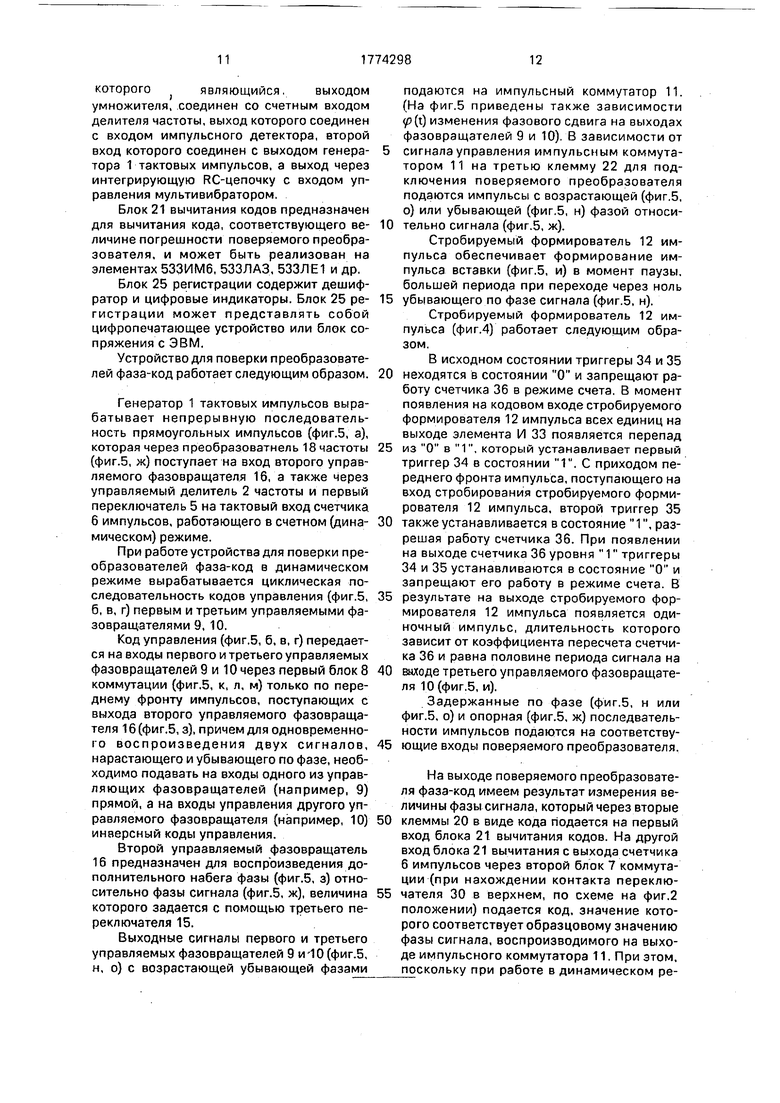

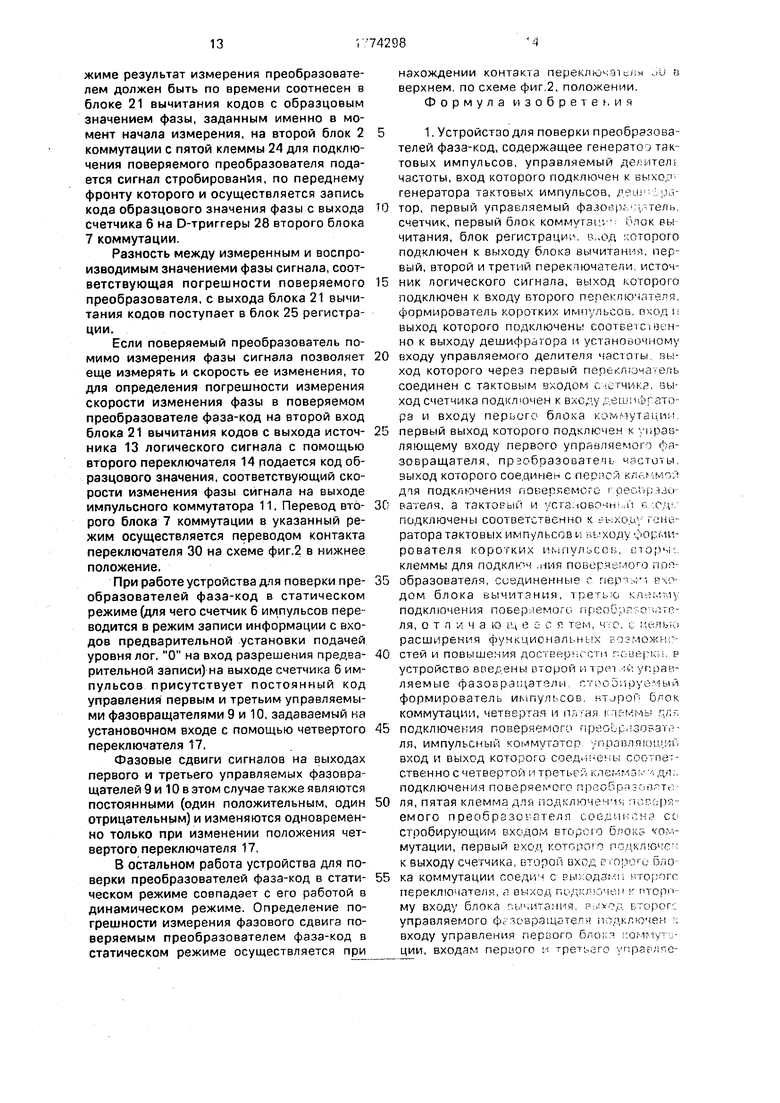

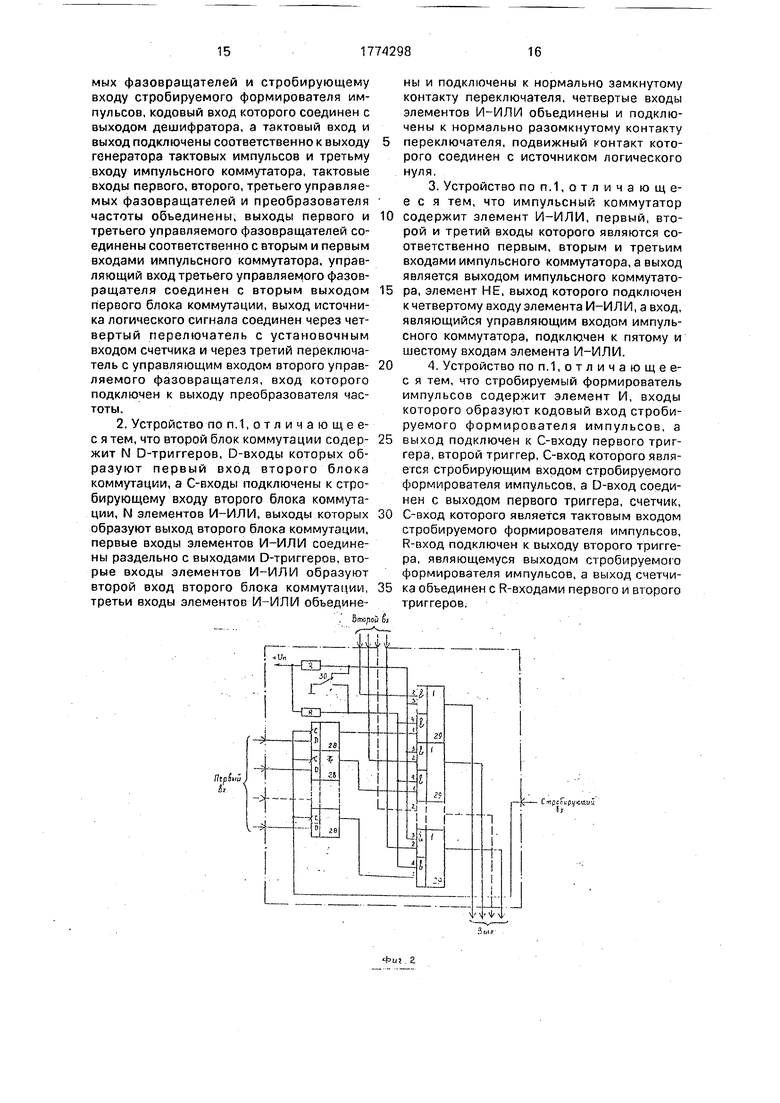

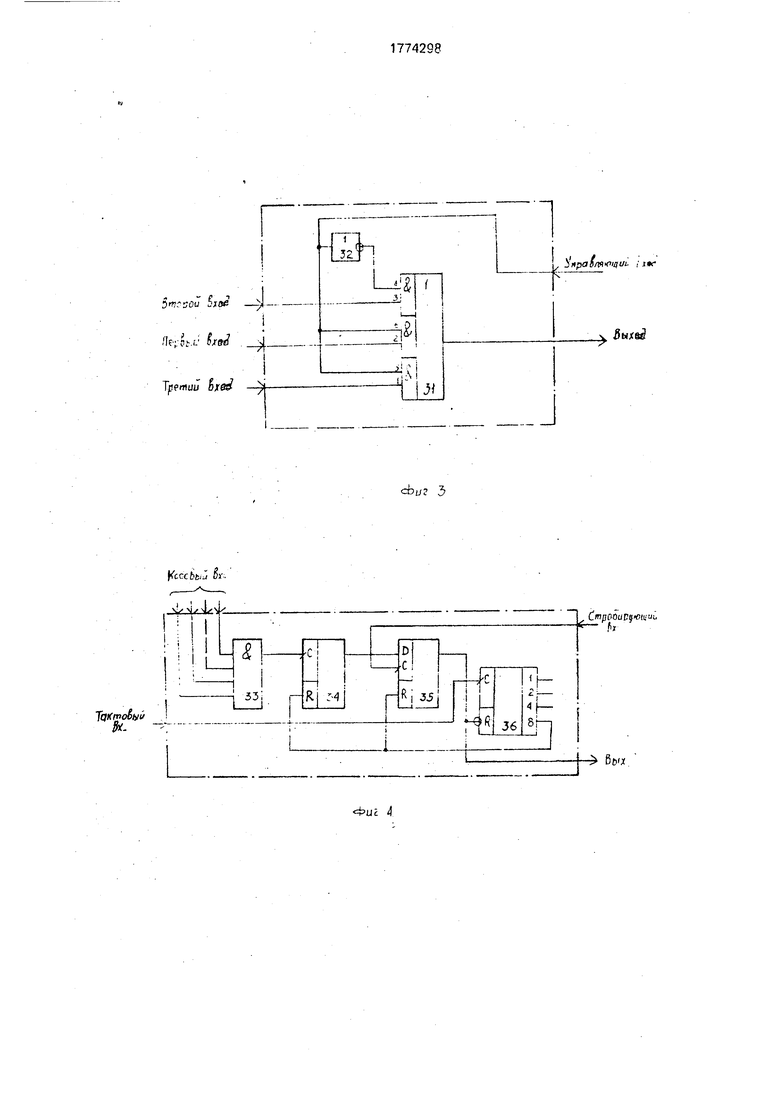

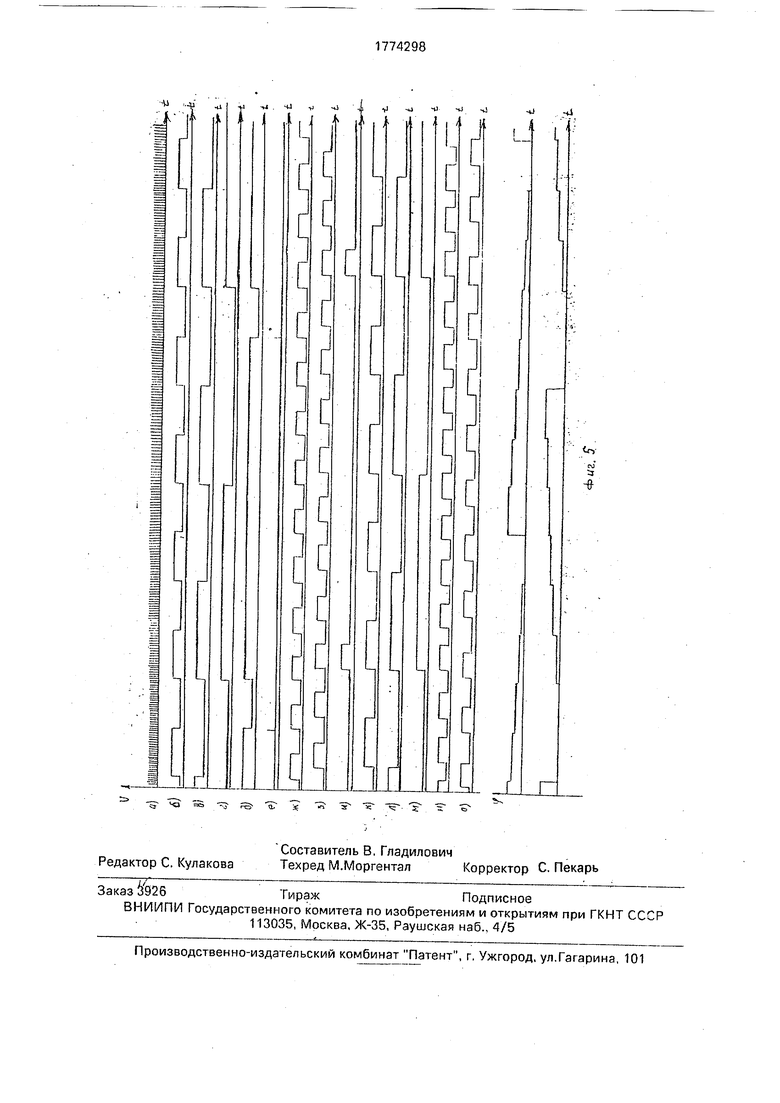

На фиг. 1 представлена структурная схе5 ма устройства для поверки преобразователей фаза-код; на фиг.2 - функциональная схема второго б тока коммутации; на фиг.З - функциональная схема импульсного коммутатора; на фиг.4 - функциональная схема стробируемого формирователя импульсов;

на фмг.5 - временные диаграммы, поясняющие работу устройства.

Устройство для поверки преобразователей фаза-код (фиг.1) содержит генератор 1 тактовых импульсов, управляемый делитель

2частоты, вход которого подключен к выходу генератора 1 тактовых импульсов, дешифратор 3, формирователь 4 коротких импульсов, вход и выход которого подключены соответственно к вы ходу дешифратора

3и установочному входу управляемого делителя 2 частоты, выход последнего через первый переключатель 5 соединен с тактовым входом счетчика 6, выходы счетчика б подключены к входу дешифратора 3, к пер- вому входу второго блока 7 коммутации и к входу первого блока 8 коммутации, выходы которого подключены к управляющему входу первого управляемого фазовращателя 9

и к управляющему входу третьего управляв- мого фазовращателя 10, выходы первого и третьего управляемых фазовращателей 9 и 10 соединены соответственно с вторым и первым сходами импульсного коммутатора 11, стробируемый формирователь 12 им- пульсов, кодовый вход которого соединен с входом дешифратора 3, а тактовый вход и чыход подключены соответственно к выходу генератора 1 тактовых импульсов и третьему входу импульсного коммутатора 11, источник: 13 логического сигнал, выход которого через второй переключатель 14 соединен с вторым входом второго блока 7 коммутации , через третий переключатель 15 с управляющим входом второго управляв- мого Фазовращателя 16, а через четвертый переключатель 17 с установочным входом счетчика б, выход второго управляемого фазовращателя 16 подключен к входу управления первого блока 8 коммутации, стробирующему входу стробируемого формирователя 12 импульсов и входом первого и третьего управляемых фазовращателей 9 и 10, преобразователь 18 частоты, выход которого соединен с входом второго управ- ляемого фазовращателя 16 и с первой клеммой 19 для подключения поверяемого преобразователя, а тактовый и установочный входы подключены соотвественно к выходу генератора 1 тактовых импульсов и выходу формирователя 12 коротких импульсов, причем тактовые входы первого, второго, третьего управляемых фазовращателей 9, 10, 16 и преобразователя 18 частоты объединены, вторые клеммы 20 для подключения поверяемого преобразователи поразрядно соединены с первым входом блока 21 вычитания, третья и четвертая клеммы 22, 23 соединены соответственно с управляющими входом и выходом

импульсного коммутатора 11, пятая клемма 24 для подключения поверяемого преобразователя связана со стробирующим входом второго блока 7 коммутации, выход которого подключен к второму входу блока 21 вычитания, блок 25 регистрации, вход которого подключен к выходу блока 21 вычитания.

Для получения синусоидального опорного и фазопеременчого сигналов на выходе устройства к выходам преобразователя 18 частоты и импульсного коммутатора 11 могут быть подключены фильтры 26 и 27,

Второй блок 7 коммутации (фиг.2) содержит N D-триггеров 28, D-входы которых являются первым входом второго блока 7 коммутации, а С-входы объединены и являются стробирующим входом второго блока 7 коммутации, N элементов И-ИЛИ 29, у которых выходы являются выходом второго блока 7 коммутации, первые входы подключены к выходам D-триггеров 28, вторые входы являются вторым входом второго блока 7 коммутации, третьи входы объединены и подключены к нормально замкнутому контакту переключателя 30, а четвертые входы объединены и подключены к нормально разомкнутому контакту переключателя 30, подвижный контакт которого соединен с источником логического нуля.

Импульсный коммутатор 11 (фиг.З) содержит элемент И-ИЛИ 31, первый, второй и третий входы которого являются соответственно первым, вторым и третьим входами импульсного коммутатора 11, а выход соединен с выходом импульсного коммутатора 11 и элемент НЕ 32, выход которого подключен к четвертому входу элемента И-ИЛИ 31, з вход, являющийся управляющим входом импульсного коммутатора 11, - к пятому и шестому входам элемента И-ИЛИ 31.

Стробируемый формирователь 12 импульсов (фиг.4) содержит элемент И 33, вход которого является кодовым входом стробируемого формирователя 12 импульсов, а выход соединен с С-входом первого триггера 34, второй триггер 35, С-вход которого является стробирующим входом стробируемого формирователя 12 импульсов, а D-вход подключен к выходу первого триггера 34, счетчик 36, С-вход которого является тактовым входом стробируемого форморователя 12 импульсов, R-вход соединен с выходом второго триггера 35 и является выходом стробируемого формирователя 12 импульсов, а выход объединен с R-входами первого и второго триггеров 34, 35,

В качестве генератора 1 тактовых импульсов может быть применен генератор прямоугольных импульсов, частота которого стабилизирована с помощью кварцевого резонатора.

Управляемый делитель 2 частоты предназначен для изменения периода повторения кода управления, вырабатываемого с помощью счет.чика 6 в динамическом режиме, и может быть реализован на микросхемах, например 155ИЕ8, коэффициент деления которых изменяется по внешним командам управления, вырабатываемым, например, с помощью переключателя.

Дешифратор 3 предназначен для выдача сигнала в момент обнуления счетчика 6 и представляет собой многовходовой элемент И(И-НЕ).

Формирователь 4 коротких импульсов обеспечивает обнуление преобразователя 18 частоты, управляемого делителя 2 частоты по сигналу дешифратора 3, появляющемуся в момент обнуления счетчика 6. Синхронизация управляемого делителя 2 частоты и преобразователя 18 частоты между собой с помощью формирователя 4 коротких импульсов исключает возможность рассогласования канала формирования ко- да управления первым и третьим управляемыми фазовращателями 9, 10 относительно канала формирования опорного напряжения в динамическом режиме. Формирователь 4 коротких импульсов может быть выполнен в виде одновибратора.

Счетчик 6 может быть выпонен на микросхемах 533ИЕ10. Для поверки преобразователей фаза-код в статическом режиме необходимо на входы разрешения предва- рительной записи микросхем 533ИЕ10 подать напряжение лог.1, а на параллельные информационные входы логический код, соответствующий определенному значению фазы. Для работы в динамическом режи- ме на входах разрешения предварительной записи должен присутствовать уровень лог.0.

Первый блок 8 коммутации представля- ет собой набор D-триггеров, выходы которых также являются выходом первого блока 8 коммутации, D-входы - его входом, а тактовые входы объединены и являются управляющим входом первого блока 8 ком- мутации. При этом код управления не только пропускается на входы первого и третьего управляемых фазовращателей 9, 10, но и сохраняется на выходе первого блока 8 коммутации до прихода следующего импульса с преобразователя 18 частоты.

Второй блок 7 коммутации служит для. выбора образцового кода, поступающего на второй вход блока 21 вычитания кодов, и для устранения динамической ошибки вычисления погрешности измерения фазового сдвига в динамическом режиме.

В качестве первого, второго и третьего управляемых фазовращателей 9, 10 и 16 может быть использовано устройство управляемой задержки импульсов по авт.св. Мг 573865. Для этого достаточно подать на управляющие входы первого счетчика устройства управляемой задержки импульсов код, соответствующий величине требуемой задержки сигнала, а на управляющие входы другого счетчика устройства управляемой задержки импульсов - код, соответствующий величине полупериода задерживаемого сигнала, и исключить два вентиля устройства управляемой задержки импульсов со своими связями.

Импульсный коммутатор 11 служит для выбора сигнала, поступающего на вход преобразователя фаза-код, с положительным или отрицательным (возрастающим или убывающим в динамическом режиме) фазовым сдвигом по сигналу управления, задаваемому этим преобразователем.

Стробируемый формирователь12 импульсов предназначен для формирования одиночного импульса с длительностью, равной половине периода сигнала на выходе третьего управляемого фазовращателя 10, в момент поступления на вход стробируемого переднего фронта импульса с выхода второго управляемого фазовращателя 16 при дополнительном условии, что на его кодовом входе в это время присутствуют все единицы.

Источник 13 логического сигнала выдает на своем выходе постоянные напряжения с уровнем лог. О и лог. 1.

В качестве переключателей 5, 14 может быть использован один общий переключатель на N положений и два направления.

В качестве перелючателей 15 и 17 могут быть использованы N тумблеров на два положения.

Преобразователь 18 частоты предназначен для формирования опорного сигнала из импульсного напряжения на выходе генератора 1 и, в зависимости от соотношения требуемых частот на выходе генератора 1 и преобразователя 18 частоты, содержит либо делитель, либо умножить частоты. Если в качестве преобразователя 18 частоты используется делитель частоты, то он может быть выполнен на микросхемах 533ИЕ10 с переключателем (в случае необходимости изменения частоты опорного напряжения). Если же в качестве преобразователя 18 частоты используется умножитель частоты, то он может представлять собой управляемый напряжением мультивибратор, выход

которогоявляющийся, выходом

умножителя, соединен со счетным входом делителя частоты, выход которого соединен с входом импульсного детектора, второй вход которого соединен с выходом генератора 1 тактовых импульсов, а выход через интегрирующую RC-цепочку с входом управления мультивибратором.

Блок 21 вычитания кодов предназначен для вычитания кода, соответствующего величине погрешности поверяемого преобразователя, и может быть реализован на элементах 533ИМ6, 533ЛАЗ, 533ЛЕ1 и др,

Блок 25 регистрации содержит дешифратор и цифровые индикаторы. Блок 25 регистрации может представлять собой цифропечатающее устройство или блок сопряжения с ЭВМ.

Устройство для поверки преобразователей фаза-код работает следующим образом.

Генератор 1 тактовых импульсов вырабатывает непрерывную последовательность прямоугольных импульсов (фиг.5, а), которая через преобразоватнель 18 частоты (фиг.5, ж) поступает на вход второго управляемого фазовращателя 16, а также через управляемый делитель 2 частоты и первый переключатель 5 на тактовый вход счетчика 6 импульсов, работающего в счетном (динамическом) режиме.

При работе устройства для поверки преобразователей фаза-код в динамическом режиме вырабатывается циклическая последовательность кодов управления (фиг.5, б, в, г) первым и третьим управляемыми фазовращателями 9, 10.

Код управления (фиг.5, б, в, г) передается на входы первого и третьего управляемых фазовращателей 9 и 10 через первый блок 8 коммутации (фиг.5, к, л, м) только по переднему фронту импульсов, поступающих с выхода второго управляемого фазовращателя 16 (фиг.5, з), причем для одновременного воспроизведения двух сигналов, нарастающего и убывающего по фазе, необходимо подавать на входы одного из управляющих фазовращателей (например, 9) прямой, а на входы управления другого управляемого фазовращателя (например, 10) инверсный коды управления.

Второй упраавляемый фазовращатель 16 предназначен для воспроизведения дополнительного набега фазы (фиг.5, з) относительно фазы сигнала (фиг.5, ж), величина которого задается с помощью третьего переключателя 15.

Выходные сигналы первого и третьего управляемых фазовращателей 9 и-10 (фиг.5, н, о) с возрастающей убывающей фазами

подаются на импульсный коммутатор 11. (На фиг.5 приведены также зависимости p(i) изменения фазового сдвига на выходах фазовращателей 9 и 10). В зависимости от

сигнала управления импульсным коммутатором 11 на третью клемму 22 для подключения поверяемого преобразователя подаются импульсы с возрастающей (фиг.5, о) или убывающей (фиг.5, н) фазой относительно сигнала (фиг.5, ж).

Стробируемый формирователь 12 импульса обеспечивает формирование импульса вставки (фиг.5, и) в момент паузы, большей периода при переходе через ноль

убывающего по фазе сигнала (фиг.5, н).

Стробируемый формирователь 12 импульса (фиг.4) работает следующим образом.

В исходном состоянии триггеры 34 и 35

неходятся в состоянии О и запрещают работу счетчика 36 в режиме счета. В момент появления на кодовом входе стробируемого формирователя 12 импульса всех единиц на выходе элемента И 33 появляется перепад

из О в 1, который устанавливает первый триггер 34 в состоянии 1. С приходом переднего фронта импульса, поступающего на вход стробирования стробируемого формирователя 12 импульса, второй триггер 35

также устанавливается в состояние 1, разрешая работу счетчика 36. При появлении на выходе счетчика 36 уровня 1 триггеры 34 и 35 устанавливаются в состояние О и запрещают его работу в режиме счета. В

результате на выходе стробируемого формирователя 12 импульса появляется одиночный импульс, длительность которого зависит от коэффициента пересчета счетчика 36 и равна половине периода сигнала на

выходе третьего управляемого фазовращателя 10 (фиг.5, и).

Задержанные по фазе (фиг.5, н или фиг.5, о) и опорная (фиг.5, ж) последватель- ности импульсов подаются на соответствующие входы поверяемого преобразователя.

На выходе поверяемого преобразователя фаза-код имеем результат измерения величины фазы сигнала, который через вторые

клеммы 20 в виде кода подается на первый вход блока 21 вычитания кодов. На другой вход блока 21 вычитания с выхода счетчика 6 импульсов через второй блок 7 коммутации (при нахождении контакта переключателя 30 в верхнем, по схеме на фиг.2 положении) подается код, значение которого соответствует образцовому значению фазы сигнала, воспроизводимого на выходе импульсного коммутатора 11. При этом, поскольку при работе в динамическом режиме результат измерения преобразователем должен быть по времени соотнесен в блоке 21 вычитания кодов с образцовым значением фазы, заданным именно в момент начала измерения, на второй блок 2 коммутации с пятой клеммы 24 для подключения поверяемого преобразователя подается сигнал стробирован ия, по переднему фронту которого и осуществляется запись кода образцового значения фазы с выхода счетчика б на D-триггеры 28 второго блока 7 коммутации,

Разность между измеренным и воспроизводимым значениеми фазы сигнала, соответствующая погрешности поверяемого преобразователя, с выхода блока 21 вычитания кодов поступает в блок 25 регистрации.

Если поверяемый преобразователь помимо измерения фазы сигнала позволяет еще измерять и скорость ее изменения, то для определения погрешности измерения скорости изменения фазы в поверяемом преобразователе фаза-код на второй вход блока 21 вычитания кодов с выхода источника 13 логического сигнала с помощью второго переключателя 14 подается код образцового значения, соответствующий скорости изменения фазы сигнала на выходе импульсного коммутатора 11. Перевод второго блока 7 коммутации в указанный режим осуществляется переводом контакта переключателя 30 на схеме фиг.2 в нижнее положение.

При работе устройства для поверки преобразователей фаза-код в статическом режиме (для чего счетчик 6 импульсов переводится в режим записи информации с входов предварительной установки подачей уровня лог. О на вход разрешения предварительной записи) на выходе счетчика 6 импульсов присутствует постоянный код управления первым и третьим управляемыми фазовращателями 9 и 10, задаваемый ка установочном входе с помощью четвертого переключателя 17.

Фазовые сдвиги сигналов на выходах первого и третьего управляемых фазовращателей 9 и 10 в этом случае также являются постоянными (один положительным, один отрицательным) и изменяются одновременно только при изменении положения четвертого переключателя 17.

В остальном работа устройства для поверки преобразователей фаза-код в статическом режиме совпадает с его работой в динамическом режиме. Определение погрешности измерения фазового сдвига поверяемым преобразователем фаза-код в статическом режиме осуществляется при

нахождении контакта перекл. о верхнем по схеме фиг 2, положении Формула изобретекич

1 Устройстзо для поверки преобразователей фаза-код, содержащее генерато j так товых импульсов, управляемый дег пел частоты, вход которого подключен к т генератора тактовых импульсов, р- i

тор, первый управляемый фазодр, . телг, счетчик, первый блок коммутз, РЮК вы питания, блок регистрации « од оторого подключен к выходу блока вычитания первый, второй и третий перек шчатели источник логического сигнала, выход которою подключен к входу второго nenet люч. формирователь коротких импл льсоь вхог; i

ВЫХОД КОТОРОГО ПОДКЛЮЧеНЬ1 СООТЬ81С,в.Нно к выходу дешифратора и установочному

входу управляемого делитепя частоты г,н- ход которого через первый . епь соединен с тактовым Влодом с огчиь вы ход счетчика подключен к Влс; чр ати ра и входу перьог; блока i jM -i -Tann

первый выход которого подкл(счем к ирзь- ляющему входу первого управляемом з f я- зовращателя, прэобоазоватеш. частоты выход которого соединен с пес дтя подкппченич поверяемого г oect j.i

, а ТЗКТОРЫИ и era toei-in и оч подключены соответственно i u ли ратора тактовых им пульсе в i , vot.Mi - рователя коротких и пулоссч клеммы для подклкч ния nobec ifHjro ,|рл

образовател°, соединенные о ricp v, РЧ дом блока ьычитания, чт11 i подключения повер е ю-. псооС i о :гг ля, о т п s ч а ю t v е , г тем ч о ч- ть i расширения Фучмдисчэт н - ож-

стей и повышения досiЕзео1 i in г i и в устройство впе/гены второй и трет ч ляемые фазоврэ дэт«лп осопоч мыи формиоователь игчпуч сов чт итог коммутации, четверня и IT. ня i icv.b v.

подключения поверяемог i чрео . с,пва

ЛЯ, ИМПуЛЬСНЬи КОММУ1ЭТСР 1 оаВПТ ЧИ П

вход и выхсд которого соедн -CL L ccf па ственно с четвертом итоетье .лсг-т-т ГД 1 подключения говерремсго пр обрт- ля, пятая клемма дпя кг )° емого преобразс1 г гелч LOCL II -.л ее

СТрОбИруЮЩИМ ВХОДОМ СпОчо VO мутации, первый вхоц IT к выходу счетчика ьтирой вход с i тит о ,о ка коммутации среди с РЫ одз i переключателе, л вычгд i i гчоо му входу бчока rni, илч п управляемого фь озращсте п.пгючен входу управления перзогп ого о. г Y ции, входам первого i nppt,re

мых фазовращателей и стробирующему входу стробируемого формирователя импульсов, кодовый вход которого соединен с выходом дешифратора, а тактовый вход и выход подключены соответственно к выходу генератора тактовых импульсов и третьму входу импульсного коммутатора, тактовые входы первого, второго, третьего управляемых фазовращателей и преобразователя частоты объединены, выходы первого и третьего управляемого фазовращателей соединены соответственно с вторым и первым входами импульсного коммутатора, управляющий вход третьего управляемого фазовращателя соединен с вторым выходом первого блока коммутации, выход источника логического сигнала соединен через четвертый перелючатель с установочным входом счетчика и через третий переключатель с управляющим входом второго управ- ляемого фазовращателя, вход которого подключен к выходу преобразователя частоты.

2. Устройство поп.1,отличающее- с я тем, что второй блок коммутации содер- жит N D-триггеров, D-входы которых образуют первый вход второго блока коммутации, а С-входы подключены к стробирующему входу второго блока коммутации, N элементов И-ИЛИ, выходы которых образуют выход второго блока коммутации, первые входы элементов И-ИЛИ соединены раздельно с выходами D-триггеров, вторые входы элементов И-ИЛИ образуют второй вход второго блока коммутации, третьи входы элементов И-ИЛИ объединеBmo/

ны и подключены к нормально замкнутому контакту переключателя, четвертые входы элементов И-ИЛИ объединены и подключены к нормально разомкнутому контакту переключателя, подвижный контакт которого соединен с источником логического нуля.

3.Устройство поп.1,отличающе- е с я тем, что импульсный коммутатор содержит элемент И-ИЛИ, первый, второй и третий входы которого являются соответственно первым, вторым и третьим входами импульсного коммутатора, а выход является выходом импульсного коммутатора, элемент НЕ, выход которого подключен к четвертому входу элемента И-ИЛИ, а вход, являющийся управляющим входом импульсного коммутатора, подключен к пятому и шестому входам элемента И-ИЛИ.

4.Устройство поп.1,отличающее- с я тем, что стробируемый формирователь импульсов содержит элемент И, входы которого образуют кодовый вход стробируемого формирователя импульсов, а выход подключен к С-входу первого триггера, второй триггер, С-вход которого является стробирующим входом стробируемого формирователя импульсов, а D-вход соединен с выходом первого триггера, счетчик, С-вход которого является тактовым входом стробируемого формирователя импульсов, R-вход подключен к выходу второго триггера, являющемуся выходом стробируемого формирователя импульсов, а выход счетчика объединен с R-входами первого и второго триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для проверки цифровых приборов | 1988 |

|

SU1599817A2 |

| Автоматическое устройство для поверки стрелочных электроизмерительных приборов | 1985 |

|

SU1320783A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1988 |

|

SU1679444A2 |

| УСТРОЙСТВО ДЛЯ ПОВЕРКИ ИЗМЕРИТЕЛЕЙ ЧАСТОТЫ И ПЕРИОДА | 2009 |

|

RU2392633C1 |

| Программный генератор | 1983 |

|

SU1190484A1 |

| Устройство для поверки электрических и механических секундомеров | 1982 |

|

SU1123018A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДЫ И ФАЗЫ РАДИОСИГНАЛА | 1988 |

|

SU1556370A1 |

| Устройство для автоматической поверки электроизмерительных приборов | 1985 |

|

SU1307420A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1998 |

|

RU2124221C1 |

Изобретение может быть использовано для проверки преобразователей фаза-код, работающих в составе фазовых преобразователей угла. Устройство содержит генератор 1 тактовых импульсов, делитель 2 Фиг.1 частоты, дешифратор 3, формирователь 4 импульсов, счетчик б, блоки 7 и 8 коммутации, управляемые фазовращатели 9, 10 и 16, импульсный коммутатор 11, стробируемый формирователь 12 импульсов, источник 13 логического сигнала, переключатели 5, 14, 15, 17, преобразователь 18 частоты, блок 21 вычитания, блок 25 регистрации. Введением второго и третьего управляемых фазовращателей 10 и 16, импульсного коммутатора 11, стробируемого формирователя 12 импульсов и второго блока 7 коммутации достигается расширение функциональных возможностей устройства за счет имитации двухтактного режима работы поверяемого преобразователя и определения погрешности в динамическом режиме, а также повышение достоверности проверки. 3 з.п. ф-лы, 5 ил. сл С v| vj Ю ю 00

Ј-- С-прсГьрующии tjf

KcccbfcJ &r.

foKtr ol yu

fa

сЬиг 3

t ipooui j O( fir

M -V -a

-u 4J -yJ

Г

г

vi -u

| Устройство для поверки цифровых приборов | 1985 |

|

SU1337844A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для проверки цифровых приборов | 1988 |

|

SU1599817A2 |

Авторы

Даты

1992-11-07—Публикация

1990-08-06—Подача