: Изобретение относится к технике телевидения и может быть использовано для формирования сигналов изображения,

Цель изобретения - уменьшение искажений сигнала изображения границ круп- них сегментов. . . ......

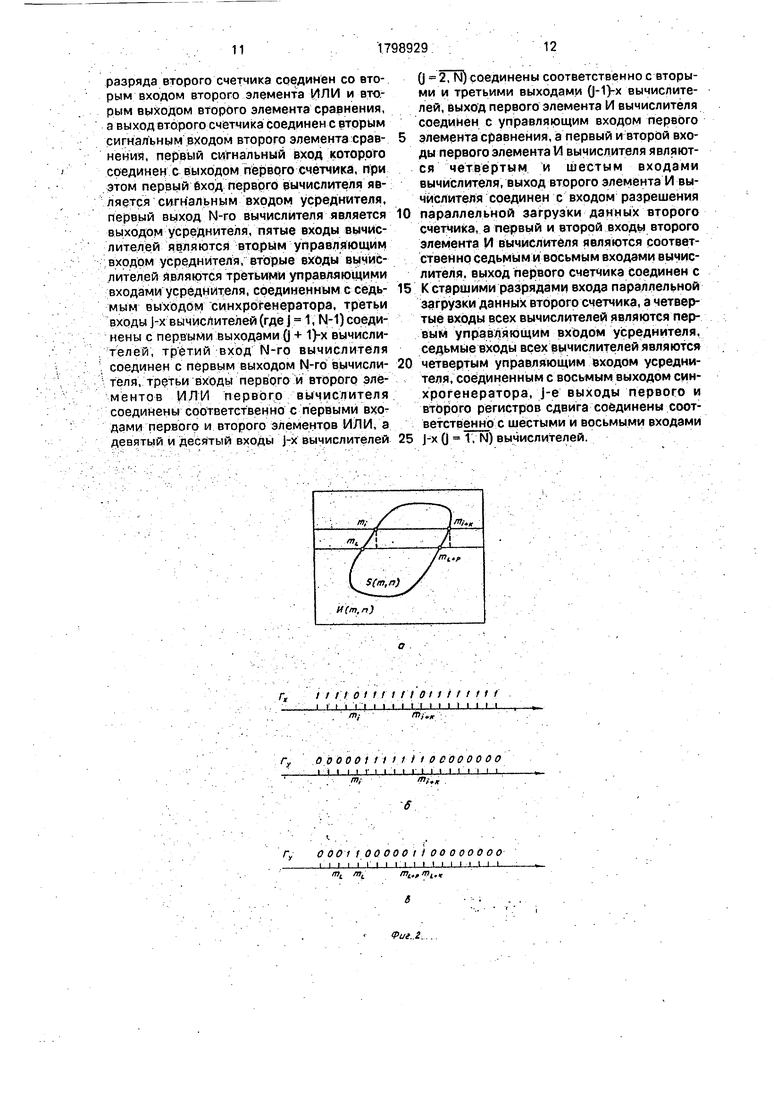

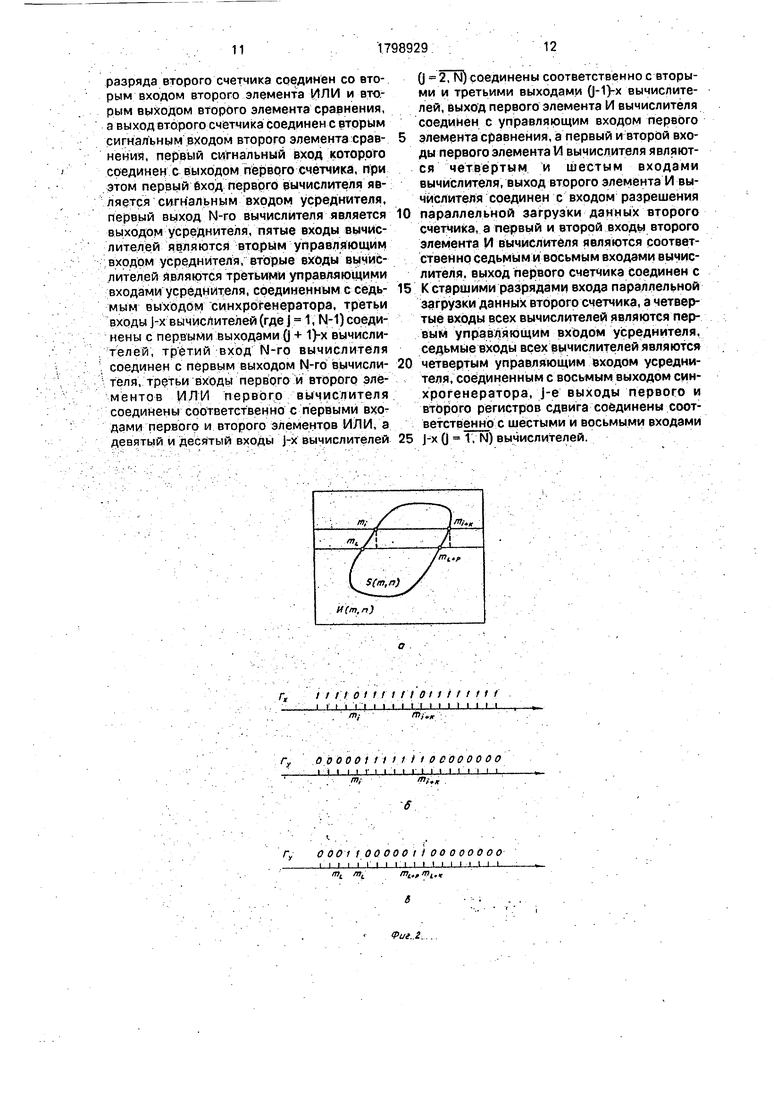

На фиг. 1 приведена структурная схема предлагаемого устройства формирования сигналов изображения; на фиг. 2 - иллюст- радия принципа посегментиой обработки сигнал изображения; ; ;. ../ ; Устройство формирЪвания сигналов изображения содержит светочувствительную матрицу П.З С 1, состоящую из секции

накопления.2, секции памяти 3 и выходного регистра 4, последовательно соединенные блок вычитания 7, первый вход которого соединен с выходом выходного регистра 4 светочувствительной матрицы ПЗС 1, и ;видеоконтрольный блок 8, генератор прямо- угольных импульсов 2.0, синхрогенератор 5, первый, второй, третий, четвертый и пятый выходы которого соединены с синхровхода- мм соответственно секции накопления 2, ., Секции памяти 3, выходного регистра 4 све- .точувствитёльной матрицы ПЗС 1, вмдео- контрольного блока 8 и генератора прямоугольных импульсов 20, а также блока усреднения 12, первый, второй управляющие входы которого соединены с выходами соответственно первого 10 и второго 11 элементов И, вторые входы которых соединены С оотв.етйт вен но с п ер в ы м и вто р ы м вы ход о м генератора прямоугольных импульсов 20, а первые входы объединены, и соединены с шестым выходом синхрогенератора 5, АЦП

6, вход которого соединен с выходом выходного регистра 4 светочувствительной матрицы ПЗС 1, 3 выход соединен с сигнальным

входом блока усреднения 12, а также ЦАП 9,

в ход которого соединен с выходом блока усреднения 12, а выход соединен со вторым входом блока вычитания 7, при этом блок усреднения 12 содержит W идентичных вычислительных блоков 13, каждый из которых

.состоит из процессорного элемента для внутристрочной обработки сигнала изобра жен.ия 14 и процессорного элемента междустрочного .накопителя 15, третий

.управляющий вход блока усреднения 12 со- единен с седьмым выходом синхрогенератора 5, двумерный полосовой фильтр 16, вход которого объединен со входом блока

измерения гистрограмм/17 и сигнальным входом первого компаратора 18 и соединен с выходом выходного регистра 4 светочувствительной матрицы ПЗС 1, а выход соеди- ;нен с сигнальным входом второго

: компаратора 19, вход опорного напряжения которого соединен с выходом источника поточного напряжения 21, выход блока измерения гистрогрэмм 17 соединен со входом блока вычисления минимума гистрограммы 22, выход которого соединен со входом опорного напряжения первого компаратора 18, выход первого компаратора 18 соединен со вторым входом третьего элемента V) 24, первый вход которого соединен с выходом Т-триггера 23, вход данных которого соединен с выходом второго компаратора 19, а установочный вход соединен с восьмым выходом синхрогенератора, выход третьего элемента И 24 соединен со входом данных D-триггера, синхровход которого соединен t седьмым выходом синхрогенератора 5, а выход соединен с объединенными входами последовательного ввода данных первого регистра сдвига 26, первым входом первого сумматора по модулю два 27, первым входом второго сумматора по модулю два 28 и входом элемента задержки 29 на период следования тактовых импульсов, причем, выход последнего разряда первого регистра сдвига 26 соединен со вторым входом первого сумматора по модулю два 27, выход которого соединен с последовательным входом данных третьего регистра сдвига 32, а выход элемента задержки 29 на период следования тактовых импульсов соединен со вторым входом второго Сумматора по модулю два 28, выход которого соединен со-входом инвертора 30, выход которого соединен с последовательным входом данных второго регистра сдвига 31, синхровходы первого 26, второго 31, третьего 32 регистров сдвига объединены и соединены с седьмым выходом синхрогеиератора 5, девятый выход синхрогенератора 5 соединен с четвертым управляющим входом блока усреднения 12, выходов второго регистра сдвига 31 соединены с входами управления сегментацией соответствующих процессорных элементов для внутристрочной обработки сигнала изображения 14, N выходов третьего регистра сдвига 32 соединены с входами управле- ния сегментацией соответствующих процессорных элементов .междустрочного накопителя 15, .

Устройство формирования сигналов изображения работает следующим образом.

Исходное состояние составных блоков и элементов устройства формирования сигналов изображения произвольное. Время окончания переходных процессов для первого 26, второго 31 и третьего 32 регистров сдвига м двумерного полосового фильтра 16 равно длительности одной строки изображения, а для блока усреднения 12 -длительности нескольких десятков строк

изображения. Максимальное время переходного процесса, равное длительности кадра имеет блок измерения гистрограмм 17. Таким образом, устройство формирования сигналов изображения готово к работе через время равное длительности кадра, что намного меньше времени установления изображения в видеоконтрольных устройствах.

Организация прсегментной обработки изображения U (m.n), (m 1, М. п. 1 ,N), содержащего один сегмент (фиг. 2,а) S (т, п), (rn.), осуществляется следующим образом. При построчном вводе изображения в устройство обработки попадает nj-я строка, являющаяся первой строкой U (m, hj), содержащей сигнал сегмента S (т, щ) U (т, пД при т б. mi, mi+k. После идентификации границы сегмента в данной строке изображения необходимо выполнить следующие действия::

1. Запретить обмен сигналами между mi-M и rni+1-м процессорными элементами для внутрйстррчной обработки сигнала изображения 14.

2. Запись к значений 0 (т, п Д, ,mi+l в процессорные элементы;меж- -дУстрочногр накопителя 15.

Вид .полученных при этом масок Гх и Гу представлен .на фиг. 2 б. По приходу следу- ющей строки изображения необходимо выполнить пункт 1 рассматриваемой процедуры, а в процессорные элементы междустрочного накопителя 15 с mt no mi и с rriL+p по тн запись значения элементов изображения текущей строки. Маска Гу примет вид, представленный на фиг. 2 в. Для идентификации границы сегмента используются признаки величины и крутизны перепада сигнала изображения, .

Во время очередной строки телевизионного изображения видеосигнал с выхода выходного регистра 4 светочувствительной матрицы ПЗС 1 поступает на вход АЦП 6, на первый вход блока вычитания 7, на вход двумерного полосового фильтра 16, на вход блока измерения гистограмм 17 и на сигнальный вход первого компаратора 18.

После аналого-цифрового преобразования строка телевизионного изображения в цифровой форме поступает на сигнальный вход блока усреднения 12. На третий у п- равляющий вход блока усреднения 12 с седьмого выхода синхрогенератора 5 подается последовательность импульсов, уп- равляющая последовательной записью строки телевизионного изображения в процессорные элементы для внутристрочной обработки сигнала изображения 14. Во время строчного гасящего импульса первоначально с выхода генератора 20 прямоугольный импульс поступает на вход первого элемента И 10. .

Тактовые импульсы с шестого выхода синхрогенератора через первый элемент И 10 поступают на первый управляющий вход блока усреднения 12 (управляющий усреднением по горизонтали). Степень усреднения гга горизЬнтали зависит от количества :импульсов, которое регулируется путем изменения длительности, импульса на выходе генератора прямоугольных импульсов 20, Усреднение по вертикали достигается подачей импульса со второго выхода генератора прямоугольных импульсов 20 на второй вход второго элемента И 11 и на второй управляющий вход блока усреднения 12 (управляющий расфокусировкой по вертикали). Степень усреднения по вертикали регулируется аналогично степени усреднения по горизонтали.

Во время записи сигнала изображения в блок усреднения видеосигнал с выхода выходного регистра 4 светочувствительной матрицы ПЗС 1 поступает также на объединенные входы двумерного полосового фильтра 16. блока измерения гистограммы 17 и сигнальный вход первого компаратора 18. С выхода двумерного полосового фильтра 16 сглаженный продифференцированный сигнал поступает на сигнальный вход второго компаратора 19.:

В первом компараторе 18 происходит сравнение видеосигнала с пороговым напряжением, вырабатываемым блоком измерения гистограмм 17 и блоком измерения минимума гистограммы 22. и выдача единичного, напряжения на выходе при превышении видеосигналом порога. Во втором компараторе 19 происходит сравнение продифференцированного видеосигнала с порогом, поступающим : от источника постоянного напряжения 21. На выходе второго компаратора 19 единичное напряжение появляется в случае превышения заданного уровня скорости нарастания фронта видеосигнала. Для получения бинарно квантованного видеосигнала служит Т-триггер 23 и третий элемент И 24. Перед поступлением очередной строки изображения, во время строчного гасящего, Т-триггер 23 устанавливается в О импульсом, поступающим с восьмого выхода синхрогенератора 5, При соблюдении двух условий: превышения видеосигналом и его производной заданных уровней на выходе третьего элемента И 24 является единичный импульс, длительность которого соответствует размеру сегмента в данной строке изображения. Для получения из этого импульса

пачки импульсов с периодом следования тактовых импульсов сигнал с выхода третьего элемента И 24 подается на вход данных синхронного D-триггера 25, на синхровход которого подаются импульсы с седьмого выхода синхрогенератора. Для преобразования последовательностей с выхода синхронного D-триггера в маску Гх, регулирующую внутристрочную обработку, служат элемент задержки на период следования тактовых импульсов 29 и второй сумматор по модулю два 28. Формирование маски Гх проиллюстрировано на. фиг. 2 а, где Ути - последовательность тактовых импульсов, поступающие с седьмого выхода синхрогенератора 5, Uzs - последовательность импульсов на выходе синхронного Р-триггера

25. Озо - маска Гх, получаемая с выхода инвертора 30, U29 - последовательность импульсов на выходе элемента задержки на период следования тактовых импульсов 29, U28 - последовательность импульсов на выходе второго сумматора по модулю два 28.

Сформированная таким образом маска записывается во второй регистр сдвига 31, с выходов которого на входы управления сегментацией процессорных элементов внутристрочной обработки.

Для получения маски Гу, регулирующей процесс междустрочной обработки сигнала изображения, сигнал с выхода синхронного D-триггера 25 подается на первый вход первого сумматора по модулю два 27, на второй вход которого подается сигнал с выхода последнего разряда первого регистра сдвига

26. соответствующий сигналу с выхода синхронного D-триггёра 25 для предыдущей строки изображения. Формирование маски ГУ иллюстрируется на фиг. 26, где Uae. последовательность импульсов с выхода последнего разряда первого регистра сдвига 26, U25 - последовательность импульсов с выхода синхронного D-триггера 25, Ua.-- маска Гу, получаемая с выхода первого сумматора по модулю два 27. Эта маска с выходов параллельного вывода данных подается на входы управления сегментацией процессорных элементов междустрочного накопителя 15, Запись текущих значений изображения в процессорные элементы междустрочного накопителя осуществляется подачей импульса с 9 выхода синхрогенератора 5 на четвертый управляющий вход блока усреднения 12.. .

Сдвиг чисел, записанных в регистры сдвига осуществляется подачей тактовых импульсов с седьмого выхода синхрогенератора 5;

Адаптация устройства формирования сигналов изображения к абсолютному значению перепада на краях сегментов осуществляется следующим образом, Гистограмма изображений, содержащих два крупных сегмента, носит двухмодовый характер. Минимальное значение гистограммы между модами. Даст оптимальный порог для разделения сегментов по признаку абсолютного значения перепада. Для этого видеосигнал с выхода выходного регистра 4 светочувст0 вительной матрицы ПЗС 1 подается на последовательно соединенные блок измерения гистограмм 17 и блок вычисления минимума гистограммы 2.2, где формируется сигнал, подаваемый на вход

5 опорного напряжения первого компаратора 18.

С приходом следующей строки видеосигнал локально усредненного изображения выводится из процессорных элементов

0 для внутристрочной обработки и на его ме сте записывается приходящий видеосигнал. В блоке вычисления 7 после цифроаналого- вого преобразования в ЦАП 9 видеосигнал локально усредненного изображения вычи.5 тается из исходного видеосигнала.

В результате достигается подавление низкочастотной составляющей сигнала изображения с регулируемым диапазоном подавления и уменьшением искажений на

0 границах сегментов с резкими перепадами яркости, а также использование устройства приводит к выделению мелкой структуры изображения и повышению его контрастности; :.

5 Ф о р м у л а и з о б р ет е н и я

1. Устройство формирования сигнала изображения, содержащее светочувствительную матрицу приборов,с зарядовой связью (ПЗС), состоящую из секции накоп0 ления,секции памяти и выходного регистра, блок вычитания,;первый вход которого соединен с выходом выходного регистра све- точувствительной матрицы ПЗС, и видеоконтрольный блок,- вход которого

5 подключен к выходу блока вычитания, генератор прямоугольных импульсов, синх- рогенератор, с первого по пятый выходы которого соединены с входами синхронизации соответственно секции накопления,

0 секции памяти и выходного регистра светочувствительной матрицы ПЗС. видеоконтрольного блока и генератора прямоугольных импульсов, а также блок усреднения, первый, второй управляющие

5 входы которого соединены с выходами соответственно первого и второго элементов И, первые входы которых соединены соответственно с первым и вторым выходами генератора прямоугольных импульсов, а первые входы соединены с шестым выходом синхрегенератора, аналого-цифровой преобра- эователь вход которого соединен с выходом выходного регистра светочувствительной матрицы ПЗС, а выход соединен с сигнальным входом усреднителя, цифроаналогрвый преобразователь, вход которого соединен с выходом усреднителя, а выход - со вторым входом блока вычитания, третий управляющий вход усреднителя соединен с седьмым выходом синхрогенератора, причем усред- нитель содержит N (где N - число отсчетов сигнала в строке) идентичных вычислите-, лей, каждый из которых содержит блок внутристрочной обработки сигнала изображения и блок междустрочного накопления, о т л и ч а ю щ .е ее я тем, что, с целью уменьшения искажений сигнала изображения границ крупных сегментов, введены двумерный полосовой фильтр, источник постоянного напряжения, блок измерения распределения амплитуд видеосигнала, блок вычисления минимума гистограммы, первый компаратор и второй компаратор, Т-триггер, третий элемент И, D-триггер, пер- вый, второй, и третий регистры сдвига, элемент задержки на период следования тактовых импульсов, первый и второй сумматеры по модулю два, и инвертор, причём вход двумерного полосового фильтра соединен с входом блока измерения распределения амплитуд видеосигнала, сигнальным входом первого компаратора и с выходом выходного регистра светочувствительной матрицы ПЗС. выход двумерного полрсово- . го фильтра соединен с сигнальным входом второго компаратора, вход опорного напряжения которого соединен с выходом источника постоянного напряжения, выход блока измерения распределения амплитуд видеосигнала соединен с входом блока вычисле-.

ния минимума гистограммы, выход которого соединен с входом опорного напряжения первого компаратора, выход первого компаратора соединен с вторым входом третьего элемента И, первый вход которого соединен выходом Т-триггера, вход данных которого соединен с выходом второго компаратора, становочный вход Т-триггера соединен с восьмым выходом синхрогенератора, выход третьего элемента И соединен с входом даных р-триггера, вход синхронизации которого соединен с седьмым выходом синхрогенератора, а выход - с входом последовательного ввода данных первого регистра сдвига, первым входом первого сумматора по модулю два, первым входом второго сумматора по модулю два и входом элемента задержки на период следования тактовых импульсов, выход последнего разряда первого регистра сдвига соединен с

вторым входом первого сумматора по модулю два, выход которого соединен с последо- вательным входом данных третьего регистра сдвига, выход элемента задержки 5 на период следования тактовых импульсов соединен с вторым входом второго сумматора но модулю два, выход которого соединен с входом инвертора, вход которого соединён с последовательным входом данных 0 второго регистра сдвига, входы синхронизации первого, второго и третьего регистров сдвига, соединены с седьмым выходом синхрогенератора, девятый выход синхрогенератора соединен с четвертым

5 управляющим входом блока усреднения, N выходов второго регистра сдвига соединены с соответствующими входами управления внутристрочной сегментацией усреднителя, N выходов третьего регистра

0 сдвига соединены с соответствующими входами управления межстрочной сегментацией усреднителя.

2. Устройство по п. 1, о т-л и ч а ю.щ е S с я тем, что блок внутристрочной обработки

5 содержит первый счетчик, первый элемент сравнения, первый элемент И вычислителя, первый и второй элементы ИЛИ, а блок междустрочного накопления - второй счетчик, второй элемент сравнения и второй элемент

0; И вычислителя, причем вход параллельной загрузки данных и вход разрешения параллельной загрузки первого счетчика являются соответственно первыми и вторыми входами вычислителя, выходы первого и

5 второго элементов ИЛ И соединены соответственно с -входом добавления единицы младшего разряда и входом вычитания единицы младшего разряда первого счетчика, первый сигнальный вход первого элемента

0. сравнения соединен с выходом первого . счетчика, являющегося первым выходом вычислителя, второй сигнальный вход первого элемента.сравнения является третьим входом вычислителя, первый выход первого

5 элемента сравнения соединен с первым входом первого элемента ИЛИ и является вторым выходом вычислителя, второй выход первого элемента сравнения соединен с первым входом второго элемента ИЛИ и

0 является третьим выходом вычислителя, третьи входы первого элемента ИЛИ и второго элемента ИЛИ являются соответственно десятым и девятым входами вычислителя, управляющий вход второго

5 элемента сравнения является пятым входом вычислителя, вход добавления единицы младшего разряда второго счетчика соединен с вторым входом первого элемента ИЛИ и первым выходом второго элемента сравнения, вход вычитания единицы младшего

разряда второго счетчика соединен со вторым входом второго элемента ИЛИ и вторым выходом второго элемента сравнения, а выход второго счетчика соединен с вторым сигнальным .входом второго элемента сравнения, первый сигнальный вход которого соединен с выходом первого счетчика, при этом первый йход первого вычислителя является сигнальным входом усреднитеяя, первый выход N-ro вычислителя является выходом усреднителя, пятые входы вычислителей являются вторым управляющим входом усреднителя, вторые входы вычислителей являются третьими управляющими входами усреднителя, соединенным с седьмым выходом синхрогенератора, третьи входы J-x вычислителей (где j 1 ,) соединены с первыми выходами G + 1)-х вычислителей, третий вход N-ro вычислителя соединен с первым выходом N-ro вычислителя, третьи входы первого и второго элементов ИДИ первого вычислителя соединены соответственно с первыми входами первого и второго элементов ИЛИ, а девятый и десятый входы J-x вычислителей

(j 2, N)-соединены соответственно с вторыми и третьими выходами (j-1)-x вычислителей,выход первого элемента И вычислителя соединен с управляющим входом первого

элемента сравнения, а первый и второй входы первого элемента И вычислителя являются четвертым и шестым входами вычислителя, выход второго элемента И вычислителя соединен с входом разрешения

параллельной загрузки данных второго счетчика, а первый и второй входы второго элемента И вычислителя являются соответственно седьмым и восьмым входами вычислителя, выход первого счетчика соединен с

К старшими разрядами входа параллельной загрузки данных второго счетчика, а четвертые входы всех вычислителей являются первым управляющим входом усреднителя, седьмые входы всех вычислителейявляются

четвертым управляющим входом усреднителя, соединенным с восьмым выходом син- хрогенератора, j-e выходы первого и второго регистров сдвига соединены соответственно с шестыми и восьмыми входами

j-x(j 1. N)вычислителей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигналов изображения | 1986 |

|

SU1332561A1 |

| Устройство формирования сигналов изображения | 1987 |

|

SU1429337A1 |

| Устройство формирования сигналов изображения | 1989 |

|

SU1727209A1 |

| ТЕЛЕВИЗИОННОЕ УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ | 2010 |

|

RU2426265C1 |

| Устройство формирования сигналов изображения | 1987 |

|

SU1483673A1 |

| УСТРОЙСТВО ПАНОРАМНОГО НАБЛЮДЕНИЯ "ДЕНЬ-НОЧЬ" И ТЕЛЕВИЗИОННАЯ КАМЕРА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2014 |

|

RU2555855C1 |

| Устройство для измерения смещения кромки непрозрачного объекта | 1989 |

|

SU1730538A1 |

| Телевизионная передающая камера | 1989 |

|

SU1716618A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ ВРЕМЕНИ НАКОПЛЕНИЯ ТЕЛЕВИЗИОННОГО СЕНСОРА, ИЗГОТОВЛЕННОГО ПО ТЕХНОЛОГИИ ПРИБОРОВ С ЗАРЯДОВОЙ СВЯЗЬЮ | 2016 |

|

RU2632574C1 |

| УСТРОЙСТВО ДАТЧИКА МОНОХРОМНОГО ВИДЕОСИГНАЛА ДЛЯ ТЕЛЕВИЗИОННО-КОМПЬЮТЕРНОЙ СИСТЕМЫ ПАНОРАМНОЙ ОХРАНЫ "ДЕНЬ - НОЧЬ" | 2016 |

|

RU2611425C1 |

Изобретение относится к технике телевидения и может быть использовано для формирования сигналов изображения. Цель изобретения - уменьшение искажений сигнала изображения границ крупных сегмбн- тов. Светочувствительная матрица 1 приборов с зарядовой связью, состоящая из секции 2 накопления, секции 3 памяти и выходного регистра 4, формирует сигнал изображения, который с помощью усредни- теля 12 подвергается внутристрочной и межстрочной обработке с помощью масок, записанных во второй и третий регистры 31 и 32 сдвига, при этом нуль в m-ом разряде второго регистра 31 сдвига запрещает обмен сигналами между m-м и т +1-м блоками 14 внутристрочной обработки сигнала, а единица в m-м разряде третьего регистра 32 сдвига разрешает запись текущего значения сигнала в m-й блок 15 междустрочного накопителя. Граница сегментов определяется из двух условий: превышение сигналом и его производной заданных уровней. 1 З.п.ф-лы, 2 ил. Ё

Г, II It OfftIII О I I I t t I t f

I f I I I II II I I Г I 111 I I II

. m,.:

000001 ft If t 10 CO 00000

I I 1 1 1 I l I r I I I I 1 I 1 t I

.

А.ДГ

| Способ воспроизведения телевизионного изображения на экране многопучкового электронно-лучевого прибора | 1985 |

|

SU1327324A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1993-02-28—Публикация

1989-11-23—Подача