ел

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль для логических преобразований булевых функций | 1989 |

|

SU1667050A1 |

| Устройство для вычисления булевых дифференциалов | 1989 |

|

SU1777132A1 |

| Устройство для вычисления булевых производных | 1987 |

|

SU1481793A1 |

| Устройство для решения булевых дифференциальных уравнений | 1989 |

|

SU1661791A1 |

| Устройство для распознавания на линейность булевых функций | 1990 |

|

SU1756879A1 |

| Устройство для логического дифференцирования булевых функций | 1988 |

|

SU1541591A1 |

| Устройство для вычисления булевых производных | 1988 |

|

SU1518825A2 |

| Устройство для преобразования булевых функций | 1988 |

|

SU1532946A1 |

| Устройство для логического дифференцирования и интегрирования булевых функций | 1988 |

|

SU1541592A1 |

| Модуль для вычисления логических производных | 1989 |

|

SU1730617A1 |

Изобретение относится цифровой вычислительной технике и может быть исполь- збвано как основа для построения устройств аппаратной поддержки1 вычислений в системах автоматизированного анализа и синтеза цифровых автоматов, при их диагностике и контроле, в системах анализа и синтеза изображений, логического управления сложными объектами. Цель изобретения - расширение функциональных возможностей устройства за счет вычисления логических минимумов и максимумов булевых функций. Цель достигается тем, что в модуль, содержащий Т-триггер, первый, второй и третий коммутаторы, сдвиговый регистр, элемент задержки, первый элемент ИЛИ, введены элемент И и второй элемент ИЛИ. 6 ил., 2 табл.

Изобретение относится к области цифровой вычислительной техники и может быть использовано как основа для построения устройств аппаратной поддержки вычислений в системах автоматизированного анализа и синтеза цифровых автоматов, при их диагностике и контроле, в системах анализа и синтеза изображений, логического управления сложными объектами.

Цель изобретения - расширение функциональных возможностей устройства за сч$т вычисления логических минимумов и максимумов булевых функций.

Поставленная цель достигается тем, что в модуль для вычисления булевых функций, содержащий Т-триггер, первый, второй и третий коммутаторы, сдвиговый регистр, элемент задержки, первый элемент ИЛИ, причем первый информационный вход первого коммутатора соединен с информационным входом модуля, информационный выход которого соединен с первым выходом второго коммутатора, введены элемент И и второй элемент ИЛИ, причем первый тактовый вход модуля соединен со входом Т-триг- гера, выход которого соединен с тактовым выходом модуля и первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы которых соединены с первым управляющим входом модуля, второй управляющий вход которого соединен с управляющим входом третьего коммутатора, первый и второй выходы которого соединены со входами элемента И, третий и четвертый выходы третьего коммутатора соединены со входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен со вторым информационным входом первого коммутатора и первым информаци00

о со ч о

00

онным входом второго коммутатора, второй информационный вход которого соединен с выходом старшего разряда сдвигового регистра, информационный вход которого соединен с первым выходом первого коммутатора, второй выход которого соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен со вторым выходом второго коммутатора, второй тактовый вход модуля соединен со входом разрешения сдвига сдвигового регистра и входом элемента задержки, выход которого соединен со входом разрешения записи сдвигового регистра, выход элемента I/I соединен со вторым входом второго элемента ИЛИ.

Суть данного изображения заключается в реализации вычислений логических минимумов и максимумов бинарных данных на однородных компонентах.

В основу изобретения положены следующие математические модели функционирования компонентов и модуля в целом.

Операторы логического минимума и максимума булевой функции f(X) f(xi, X2,..,, xn) n переменных по i-й переменной xi определяются соответственно соотношениями:

MIN f(X) f(xi,..., xi,..., xn)Af(xi,..., Xi,..., xn) xi

MAXf(X) f(xi,..., xi,.,., xnb ffri,..., xi,..., xn) xi

Что эквивалентно матричной форме записи:

- 0) -.

MIN X Dan Х(Л),(1) xi

+ (0

MAXX D2n X(V),(2) xi

где X - вектор значений булевой функции f(X) (столбец обычной таблицы истинности, интерпретируемый как вектор бинарных

nanMu, r)v(1) y(2n

XWX

xv

данных: X

(0 n „

Dan - матрица размерности 2 x 2 , формируемая по соотношению 0)

Dan la

i-1,

11 M

n-I.

(3)

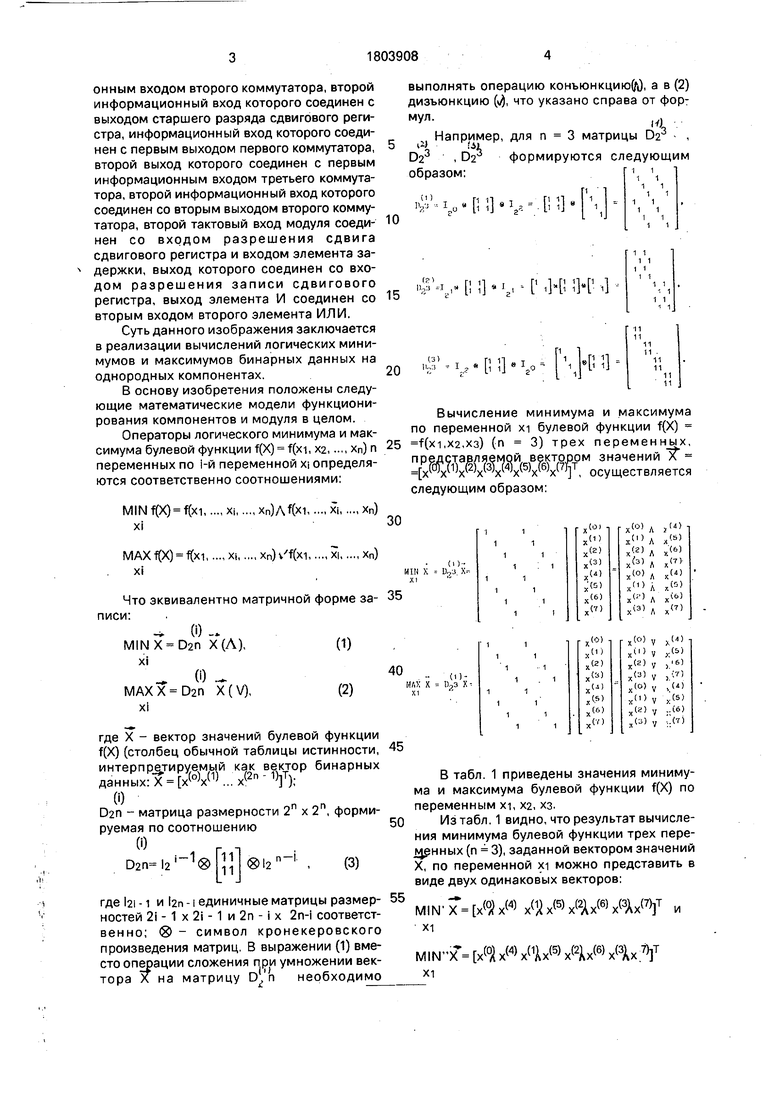

где lai -1 и lan - i единичные матрицы размерностей 2i - 1 x 2i - 1 и 2n - i x 2n-i соответственно; 8 - символ кронекеровского произведения матриц. В выражении (1) вместо onei тора

перации сложения при умножении век- X на матрицу необходимо

выполнять операцию конъюнкцию(д), а в (2) дизъюнкцию (у), что указано справа от фор- мул.

10

$4 I V С К 1

1 1

1 1

1 1

1 1

1 1

1 1

1 1

vGn-V -Pil

11 и.

11

11 11

11

Вычисление минимума и максимума

по переменной xi булевой функции f(X)

f(xi,X2,X3) (n 3) трех переменных,

представляемой вектором значений It

K№ xM3Ww,

следующим образом:

осуществляется

30

„(о)

,« п

„(г) Л х(б)

,fc

(7

« 5 ,(ь)

0

. - (О- МЛХ X 1)3 Х

11

11

1 1

11

1Г

11

11

45

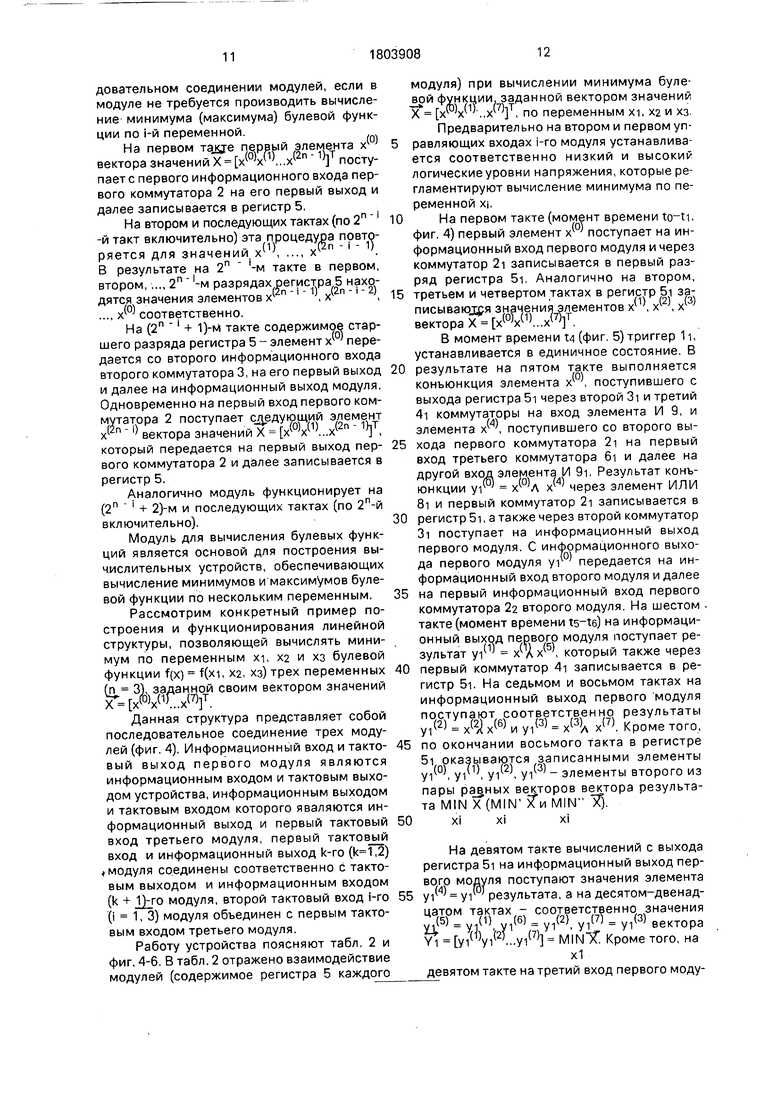

В табл. 1 приведены значения минимума и максимума булевой функции f(X) по переменным xi, xa, хз.

Из табл. 1 видно, что результат вычисления минимума булевой функции трех пере- нных (n 3), заданной вектором значений X, по переменной xi можно представить в виде двух одинаковых векторов:

хЦх®Мх®М7У и

Х1

Л х« Л x® x4lxW

Х1

размерности 22 каждый (в общем случае для функции п переменных эти два вектора имеют размерность 2П 1). В результате вычисления минимума булевой функции по второй временной Х2 можно выделить четыре вектора:

MlN X xV W, Х2

Mik x (3)T,

(, X2J

М,,. X

1

ра мерности 2 каждый (в общем случае размерность каждого из четырех векторов рае на 2П ), причем два из этих векторов пог арно равны, т.е.

л|111 гх -М1М Ги MIN x MIN xj.

Х2Х2 Х2 Х2

Аналогично для оператора нахождения минимума по переменной хз:

Miff Х- x.W, MINT Х xVf,

хз

хз

Mirf X - x V3)T MIN X )f,

X3i

хз

х$

ХЗ

Mils)- X x(4Ax(5)f, MIN - X x(4,lx(5)T, 35

Mirjv х(6Ах(7)т. MIN -X х(6) х(7)т.

Здерь выделены восемь векторов размерности 2° каждый (в общем случае 2П ), при это4 гдрпарно равны следующие вектора: MlN X MIN MlN vZ

хз + хзхз г хз . X MIN X, MIN X MIN .

хзхз хз хз

Аналогичные результаты получаются при вычислении максимума булевой функ- ции по переменной xi(i 1,п)(табл. 1).

Таким образом, искомый результат, т.е. вектЬр минимаксной операции по И переменной MIN X (МАХ X) состоит их 2 векторов

XIXI

разМериотси 2П каждый, среди которых имефтся попарно равные. Следовательно необходимо вычислять только один вектор из .

Пусть требуется вычислить минимум и максимум по переменной хч булевой функции f(X) X1X2VX3 трех (п 3) переменных. Вектор) значений булевой функции имеет вид Х 0101 . В соответствии с математическими моделями (1) и (2) определим минимум и максимум булевой функции х-|Х2 хз по переменной xi:

20

о 1 1 1

о

0

5

0

5

0

5

По векторам значений MIN X 0101 и

xi МАХ X 0111 0111 строим их аналитичеХ1

ские выражения:

MIN (xix2vxs) Х2 хз,

Х1

MAX (X1X2VX3) X2VX3. Х1

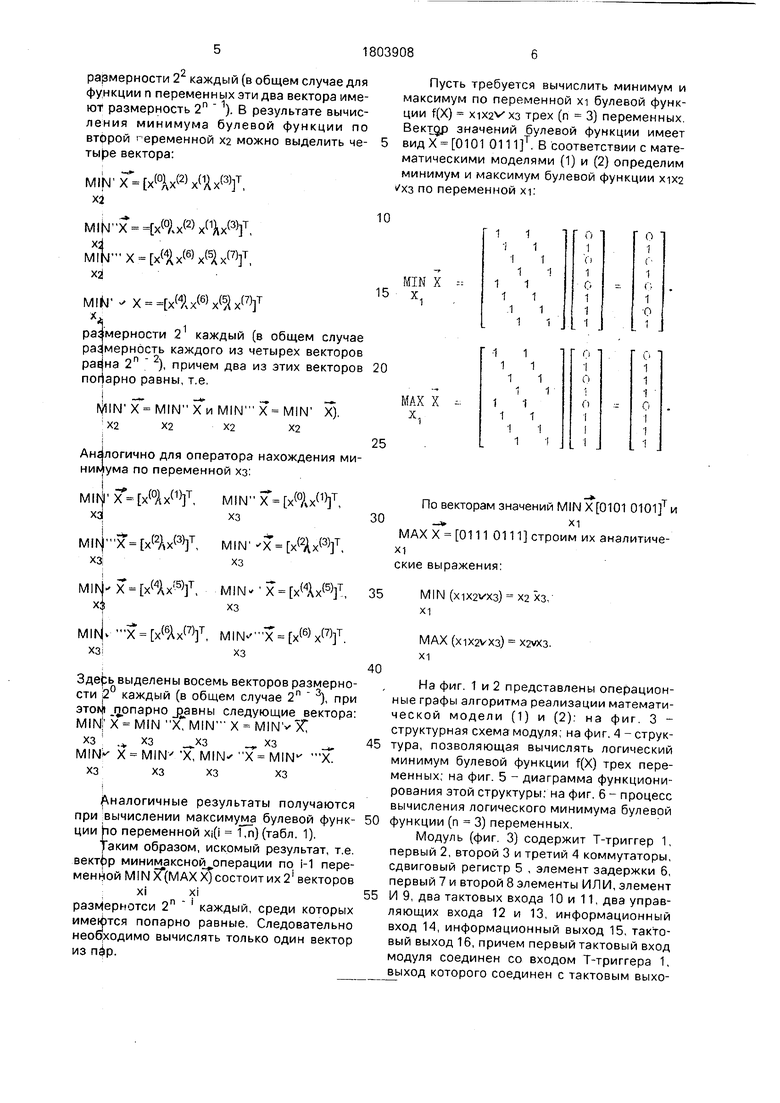

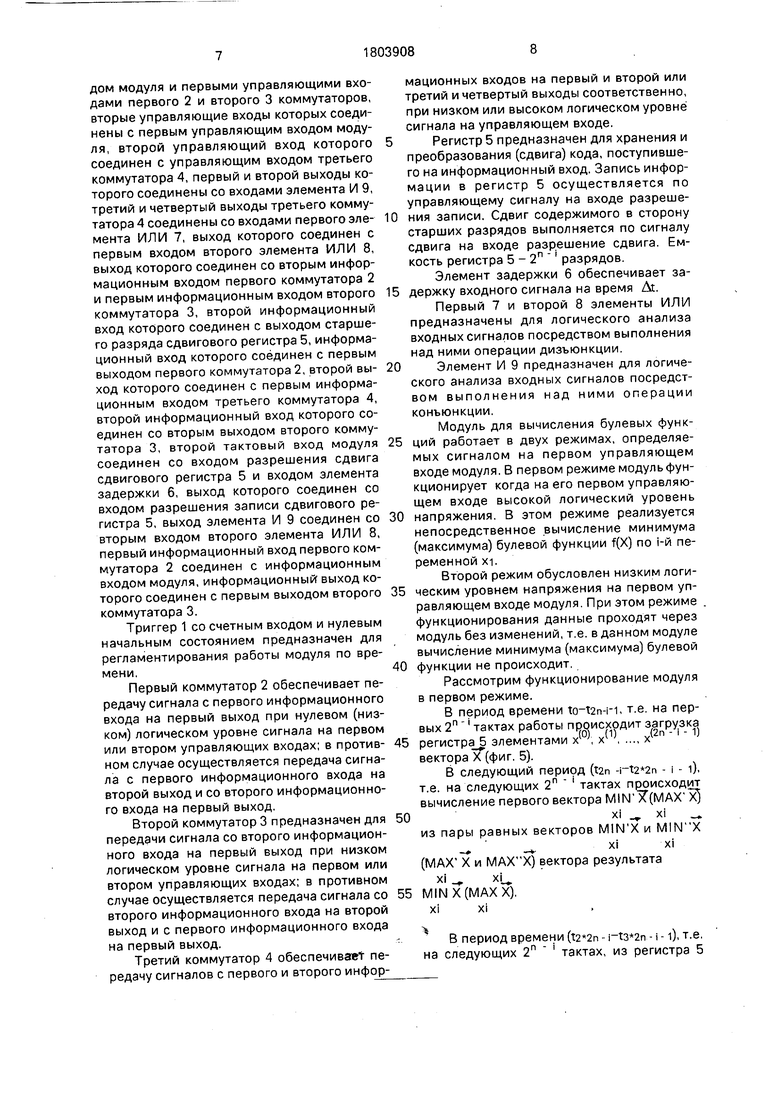

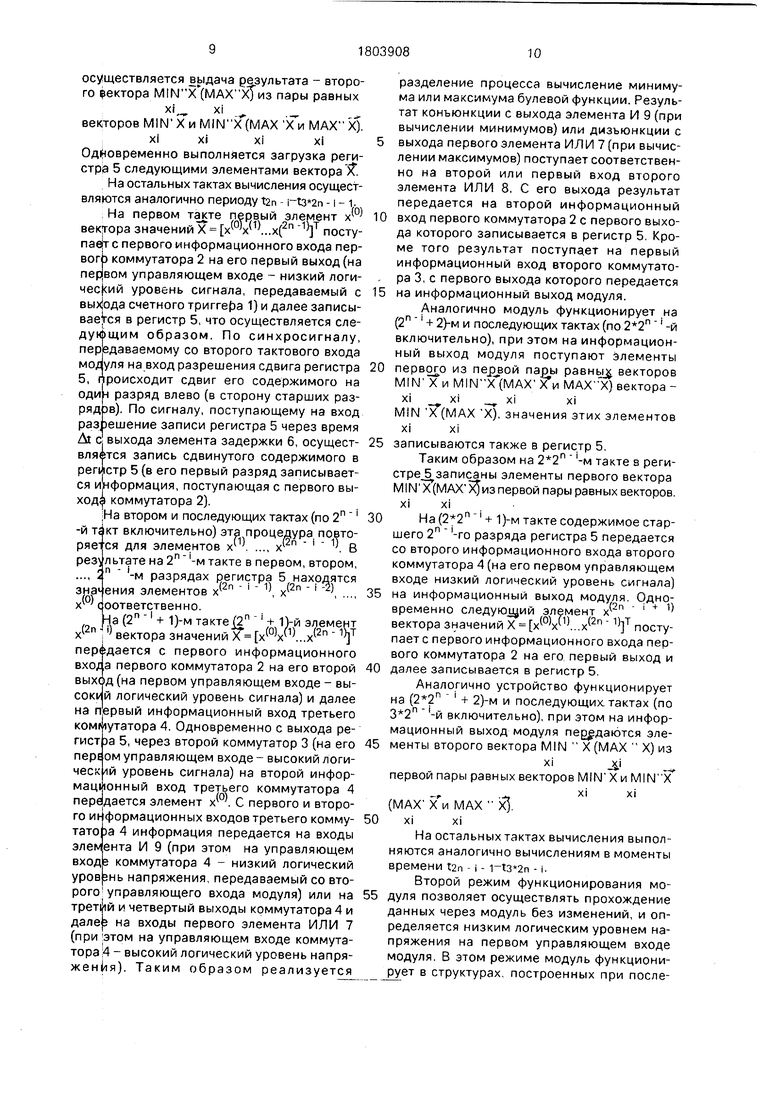

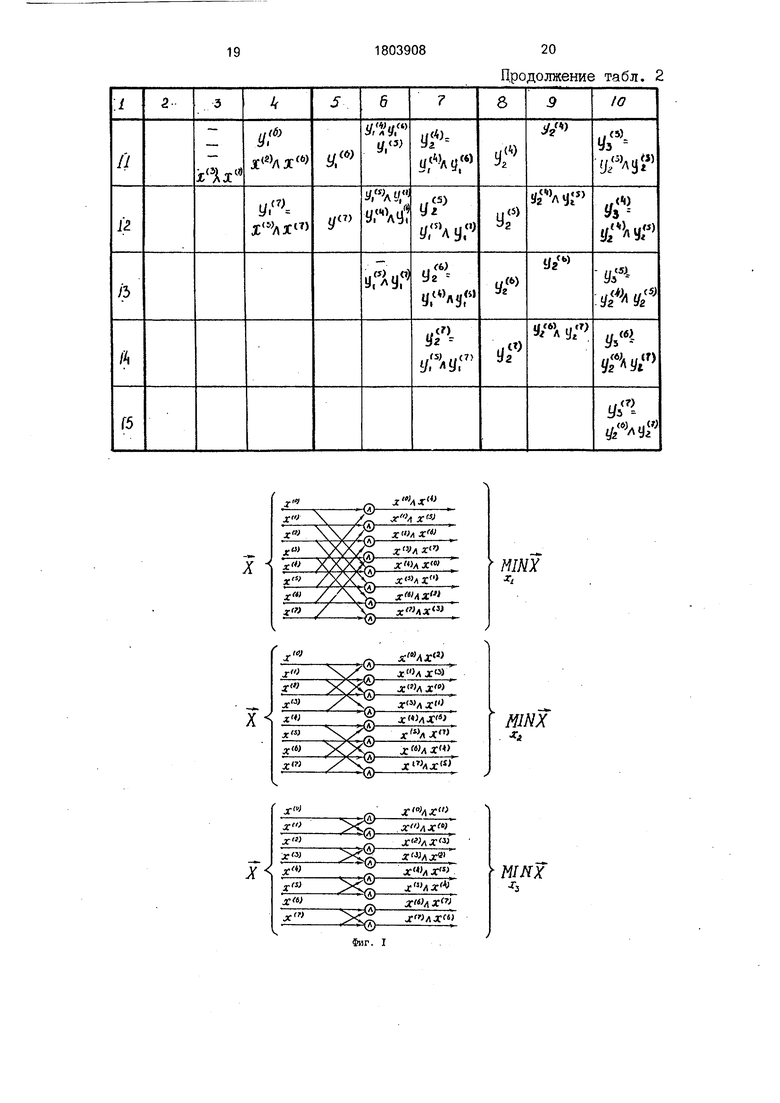

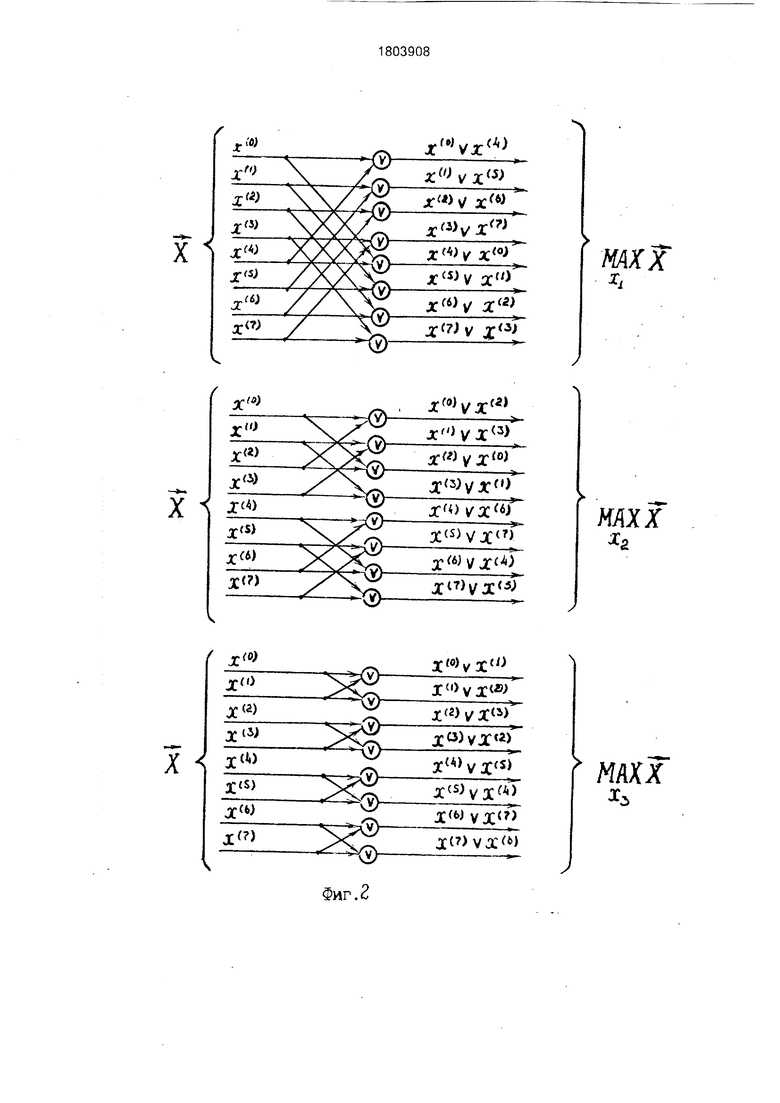

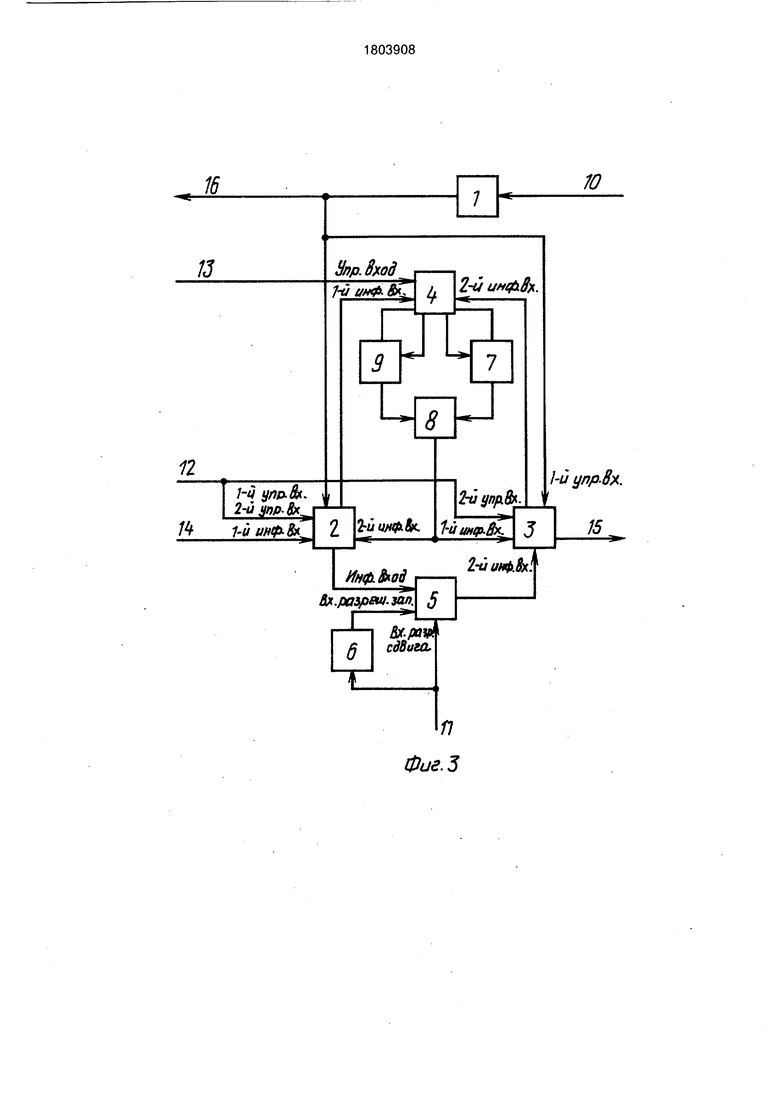

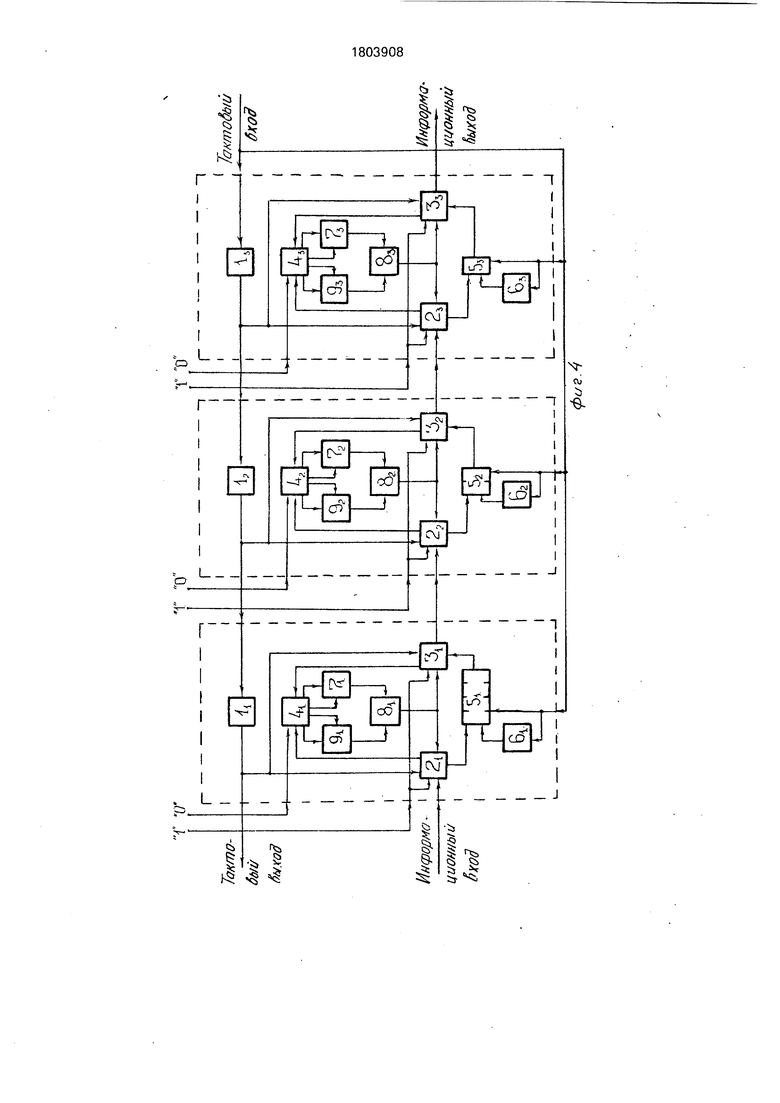

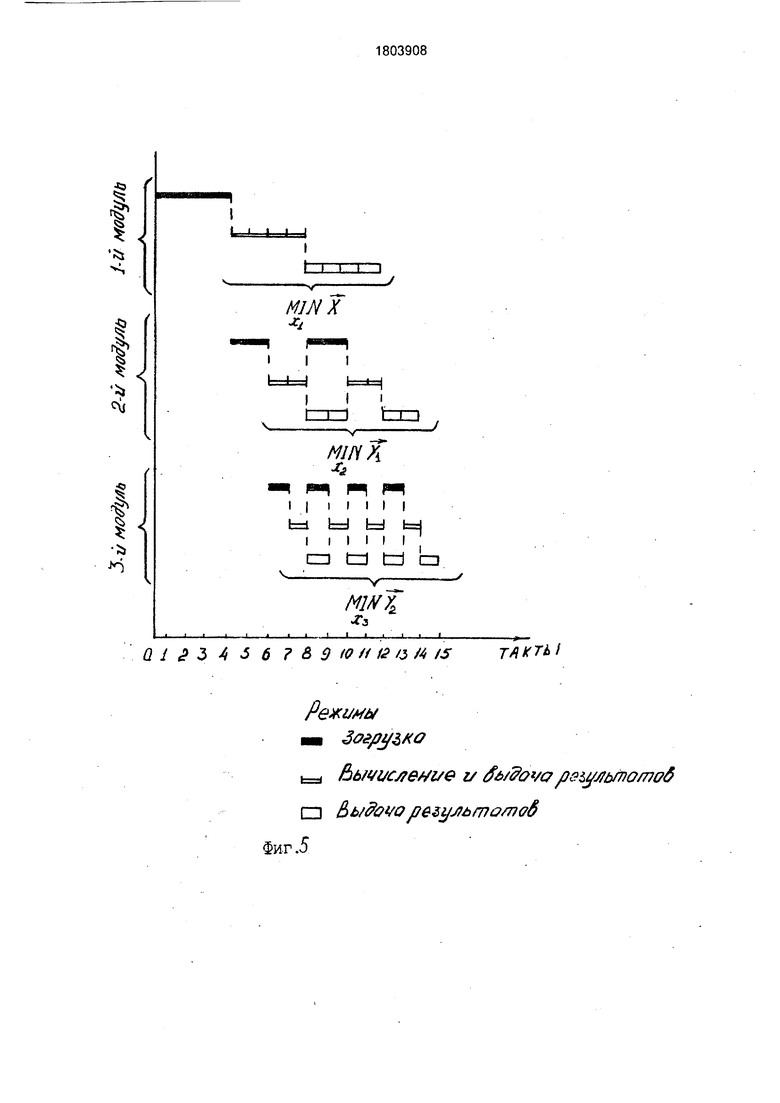

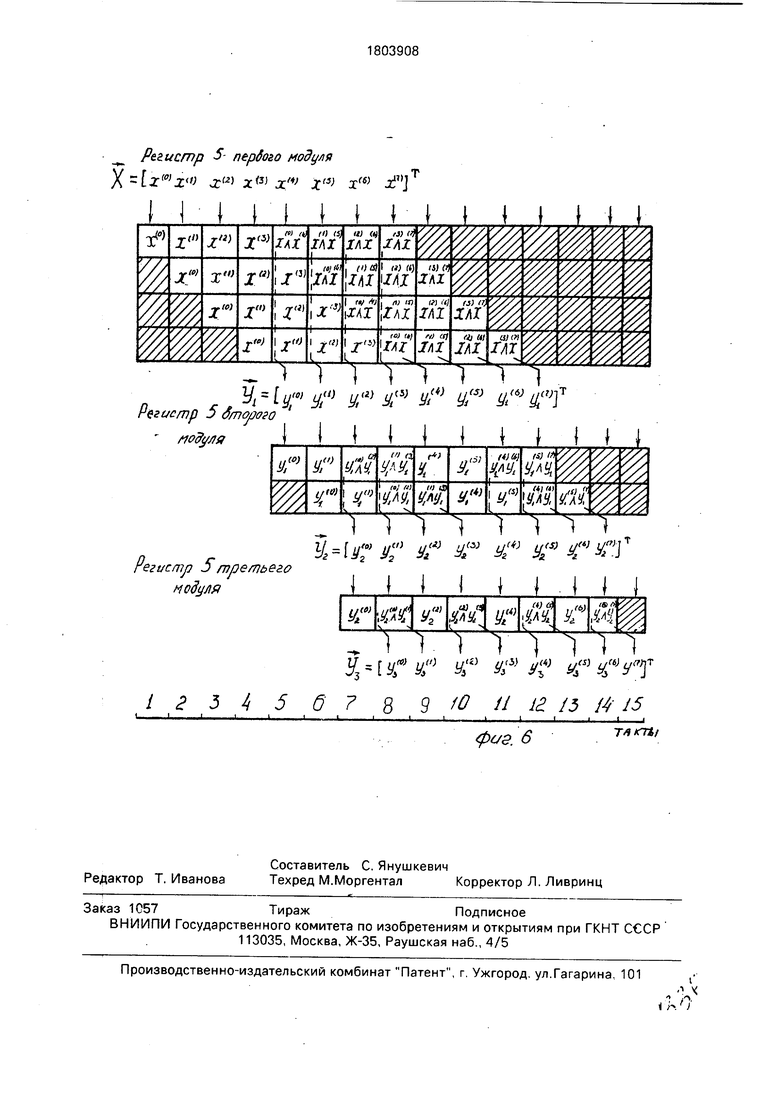

На фиг. 1 и 2 представлены операционные графы алгоритма реализации математической модели (1) и (2): на фиг. 3 - структурная схема модуля; на фиг. 4 - структура, позволяющая вычислять логический минимум булевой функции f(X) трех переменных; на фиг. 5 - диаграмма функционирования этой структуры; на фиг. 6- процесс вычисления логического минимума булевой функции (п 3) переменных.

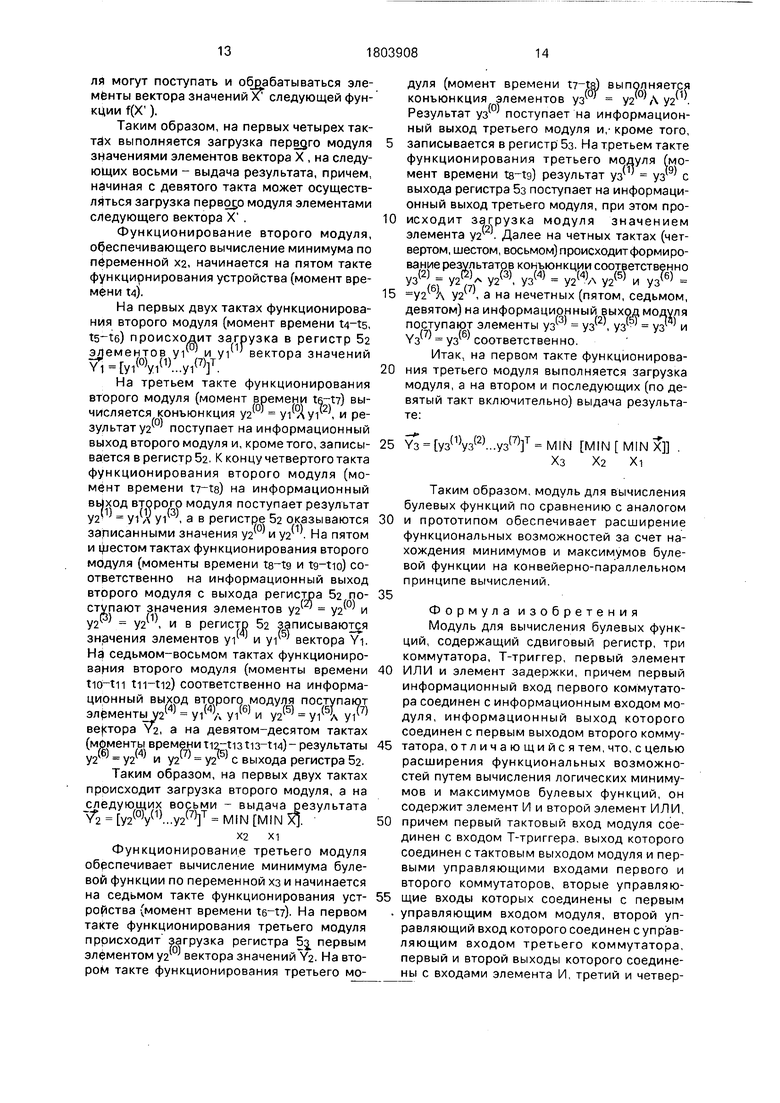

Модуль (фиг. 3) содержит Т-триггер 1, первый 2, второй 3 и третий 4 коммутаторы, сдвиговый регистр 5 , элемент задержки 6, первый 7 и второй 8 элементы ИЛИ, элемент И 9, два тактовых входа 10 и 11, два управляющих входа 12 и 13, информационный вход 14, информационный выход 15, тактовый выход 16, причем первый тактовый вход модуля соединен со входом Т-триггера 1, выход которого соединен с тактовым выходом модуля и первыми управляющими входами первого 2 и второго 3 коммутаторов, вторые управляющие входы которых соединены с первым управляющим входом модуля, второй управляющий вход которого соединен с управляющим входом третьего коммутатора 4, первый и второй выходы которого соединены со входами элемента И 9, третий и четвертый выходы третьего коммутатора 4 соединены со входами первого элемента ИЛИ 7, выход которого соединен с первым входом второго элемента ИЛИ 8, выход которого соединен со вторым информационным входом первого коммутатора 2 и первым информационным входом второго коммутатора 3, второй информационный вход которого соединен с выходом старшего разряда сдвигового регистра 5, информационный вход которого соединен с первым выходом первого коммутатора 2, второй выход которого соединен с первым информационным входом третьего коммутатора 4, второй информационный вход которого соединен со вторым выходом второго коммутатора 3, второй тактовый вход модуля соединен со входом разрешения сдвига сдвигового регистра 5 и входом элемента задержки 6, выход которого соединен со входом разрешения записи сдвигового регистра 5, выход элемента И 9 соединен со вторым входом второго элемента ИЛИ 8, первый информационный вход первого коммутатора 2 соединен с информационным входом модуля, информационный выход которого соединен с первым выходом второго коммутатора 3.

Триггер 1 со счетным входом и нулевым начальным состоянием предназначен для регламентирования работы модуля по времени,

Первый коммутатор 2 обеспечивает передачу сигнала с первого информационного входа на первый выход при нулевом (низком) логическом уровне сигнала на первом или втором управляющих входах; в противном случае осуществляется передача сигнала с первого информационного входа на второй выход и со второго информационного входа на первый выход.

Второй коммутатор 3 предназначен для передачи сигнала со второго информационного входа на первый выход при низком логическом уровне сигнала на первом или втором управляющих входах; в противном случае осуществляется передача сигнала со второго информационного входа на второй выход и с первого информационного входа на первый выход.

Третий коммутатор 4 обеспечивает передачу сигналов с первого и второго информационных входов на первый и второй или третий и четвертый выходы соответственно, при низком или высоком логическом уровне сигнала на управляющем входе. Регистр 5 предназначен для хранения и преобразования (сдвига) кода, поступившего на информационный вход. Запись информации в регистр 5 осуществляется по управляющему сигналу на входе разрешения записи. Сдвиг содержимого в сторону старших разрядов выполняется по сигналу сдвига на входе разрешение сдвига. Емкость регистра 5 - 2П разрядов.

Элемент задержки 6 обеспечивает задержку входного сигнала на время At.

Первый 7 и второй 8 элементы ИЛИ предназначены для логического анализа входных сигналов посредством выполнения над ними операции дизъюнкции.

Элемент И 9 предназначен для логического анализа входных сигналов посредством выполнения над ними операции конъюнкции.

Модуль для вычисления булевых функций работает в двух режимах, определяемых сигналом на первом управляющем входе модуля. В первом режиме модуль функционирует когда на его первом управляющем входе высокой логический уровень

напряжения. В этом режиме реализуется непосредственное вычисление минимума (максимума) булевой функции f(X) по i-й переменной XL

Второй режим обусловлен низким логическим уровнем напряжения на первом управляющем входе модуля. При этом режиме функционирования данные проходят через модуль без изменений, т.е. в данном модуле вычисление минимума (максимума) булевой

функции не происходит.

Рассмотрим функционирование модуля в первом режиме.

В период времени to-t2n-i-i, т.е. на первых тактах работы происходит загрузка

регистра 5 элементами х , х , ..., х 2п вектора X (фиг. 5).

В следующий период (t2n - i - 1), т.е. на следующих 2П тактах происходит вычисление первого вектора (МАХ х}

xi xi из пары равных векторов MIN X и

. xi xi (MAX X и ) вектора результата xi хЦ

MINX (MAX X). xixi

В период времени (t2 2n-rt3 2n-i-1), т.е. на следующих 2П тактах, из регистра 5

осуществляется выдача результата - второго ректора () из пары равных

V -г

векторов MIN MIN)T(MAX )Ги МАХ X).

xlxi xi xi Одновременно выполняется загрузка регистра 5 следующими элементами вектора )Г.

На остальных тактах вычисления осуществляются аналогично периоду t2n - -1 - 1.

На первом такте первый элемент х вектора значений ) ..x(2n посту- naejr с первого информационного входа пер- вогЬ коммутатора 2 на его первый выход (на перовом управляющем входе - низкий логи- уровень сигнала, передаваемый с выфда счетного триггера 1) и далее записы- ваеУся в регистр 5, что осуществляется следующим образом. По синхросигналу, передаваемому со второго тактового входа модуля на вход разрешения сдвига регистра 5, происходит сдвиг его содержимого на один разряд влево (в сторону старших разряд эв). По сигналу, поступающему на вход разрешение записи регистра 5 через время At с выхода элемента задержки 6, осуществляется запись сдвинутого содержимого в регистр 5 (в его первый разряд записывается информация, поступающая с первого выхода коммутатора 2).

;На втором и последующих тактах (по -и те кт включительно) эта процедура повтохГ1). ..., Xе Ч В -м такте в первом, втором,

ряется для элементов результате на

п

-м разрядах

элементов х х соответственно.

,п - I

регистра

ftn - i -М1)

5 находятся

v(2n - i 3)

,n-i

На (2n + 1)-м такте (2П + 1)-й элемент х(2п вектора значений X )...х(2п У передается с первого информационного Bxojca первого коммутатора 2 на его второй выход (на первом управляющем входе - вы- СОКУЙ логический уровень сигнала)и далее на первый информационный вход третьего коммутатора 4. Одновременно с выхода ре- гист за 5, через второй коммутатор 3 (на его пера ом управляющем входе - высокий л оги- ческчй уровень сигнала) на второй информационный вход третьего коммутатора 4 передается элемент х С первого и второго ик формационных входов третьего комму- тато )а 4 информация передается на входы элемента И 9 (при этом на управляющем входэ коммутатора 4 - низкий логический уров энь напряжения, передаваемый со второго; управляющего входа модуля) или на третей и четвертый выходы коммутатора 4 и дале на входы первого элемента ИЛИ 7 (при;этом на управляющем входе коммутатора - высокий логический уровень напряжения). Таким образом реализуется

0

5

0

5

0

5

0 5 0 5

разделение процесса вычисление минимума или максимума булевой функции. Результат конъюнкции с выхода элемента И 9 (при вычислении минимумов) или дизъюнкции с выхода первого элемента ИЛИ 7 (при вычислении максимумов) поступает соответственно на второй или первый вход второго элемента ИЛИ 8. С его выхода результат передается на второй информационный вход первого коммутатора 2 с первого выхода которого записывается в регистр 5. Кроме того результат поступает на первый информационный вход второго коммутатора 3, с первого выхода которого передается на информационный выход модуля.

Аналогично модуль функционирует на ( + 2)-м и последующих тактах (по -и включительно), при этом на информационный выход модуля поступают элементы первого из первой пары равны х. векторов МИМ ЗГи (MAX ) вектора xixi . xi xi MIN X (MAX X), значения этих элементов

xixi записываются также в регистр 5.

Таким образом на -м такте в регистре 5 записаны элементы первого вектора М1М Х(МАХ Х)изпервой пары равных векторов.

xi xi

На ( + 1)-м такте содержимое старшего 2Л -го разряда регистра 5 передается со второго информационного входа второго коммутатора 4 (на его первом управляющем входе низкий логический уровень сигнала) на информационный выход модуля. Одновременно следукиуий элемент + 1 вектора значений X ... поступает с первого информационного входа первого коммутатора 2 на его первый выход и далее записывается в регистр 5.

Аналогично устройство функционирует на ( + 2)-м и последующих тактах (по -и включительно), при этом на информационный выход модуля передаются элементы второго вектора MIN X (МАХ X) из

первой пары равных векторов MIN X и

.-,xi xi (MAX X и MAX X).

xixi

На остальных тактах вычисления выполняются аналогично вычислениям в моменты времени t2n - i - - i.

Второй режим функционирования модуля позволяет осуществлять прохождение данных через модуль без изменений, и определяется низким логическим уровнем напряжения на первом управляющем входе модуля. В этом режиме модуль функционирует в структурах, построенных при последовательном соединении модулей, если в модуле не требуется производить вычисление минимума (максимума) булевой функции по i-й переменной.

На первом Tajye первый элемента х вектора значений Х .. поступает с первого информационного входа первого коммутатора 2 на его первый выход и далее записывается в регистр 5,

На втором и последующих тактах (по -и такт включительно) эта процедура повтоy{1)v(2n - i - 1)

В результате на 2П

ряется для значении , ..., х

-м такте в первом,

втором, ..., 2П -м разрядах регистра 5 находятся значения элементов х п , х , ..., х соответственно.

На (2П + 1)-м такте содержимое старшего разряда регистра 5 - элемент передается со второго информационного входа второго коммутатора 3, на его первый выход и далее на информационный выход модуля. Одновременно на первый вход первого коммутатора 2 поступает следующий элемент $ - 0 вектора значений X ... - 1)т, который передается на первый выход первого коммутатора 2 и далее записывается в регистр 5.

Аналогично модуль функционирует на (2П + 2)-м и последующих тактах (по 2п-й включительно).

Модуль для вычисления булевых функций является основой для построения вычислительных устройств, обеспечивающих вычисление минимумов и максимумов булевой функции по нескольким переменным.

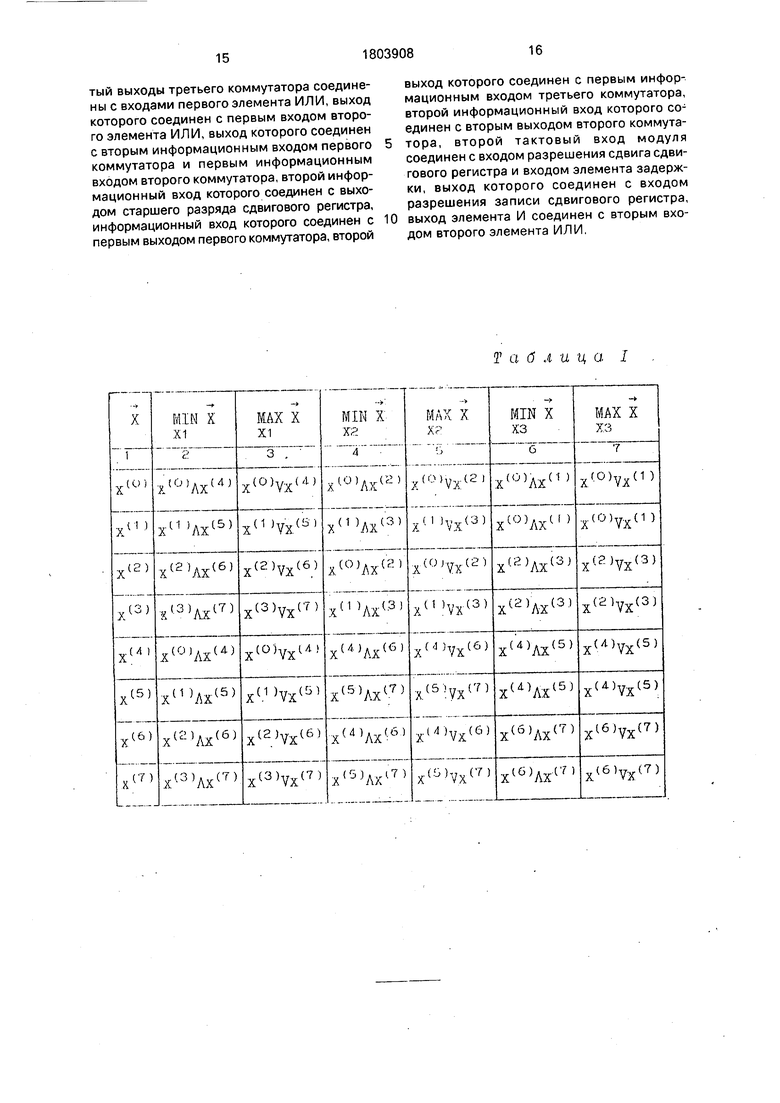

Рассмотрим конкретный пример построения и функционирования линейной структуры, позволяющей вычислять минимум по переменным XT, X2 и хз булевой функции f(x) f(xi, X2, хз) трех переменных заданной своим вектором значений

IJ - (

Данная структура представляет собой последовательное соединение трех модулей (фиг. 4). Информационный вход и тактовый выход первого модуля являются информационным входом и тактовым выходом устройства, информационным выходом и тактовым входом которого я валяются информационный выход и первый тактовый вход третьего модуля, первый тактовый вход и информационный выход k-ro (,2) f модуля соединены соответственно с тактовым выходом и информационным входом (k + модуля, второй тактовый вход i-ro (i 1, 3) модуля объединен с первым тактовым входом третьего модуля.

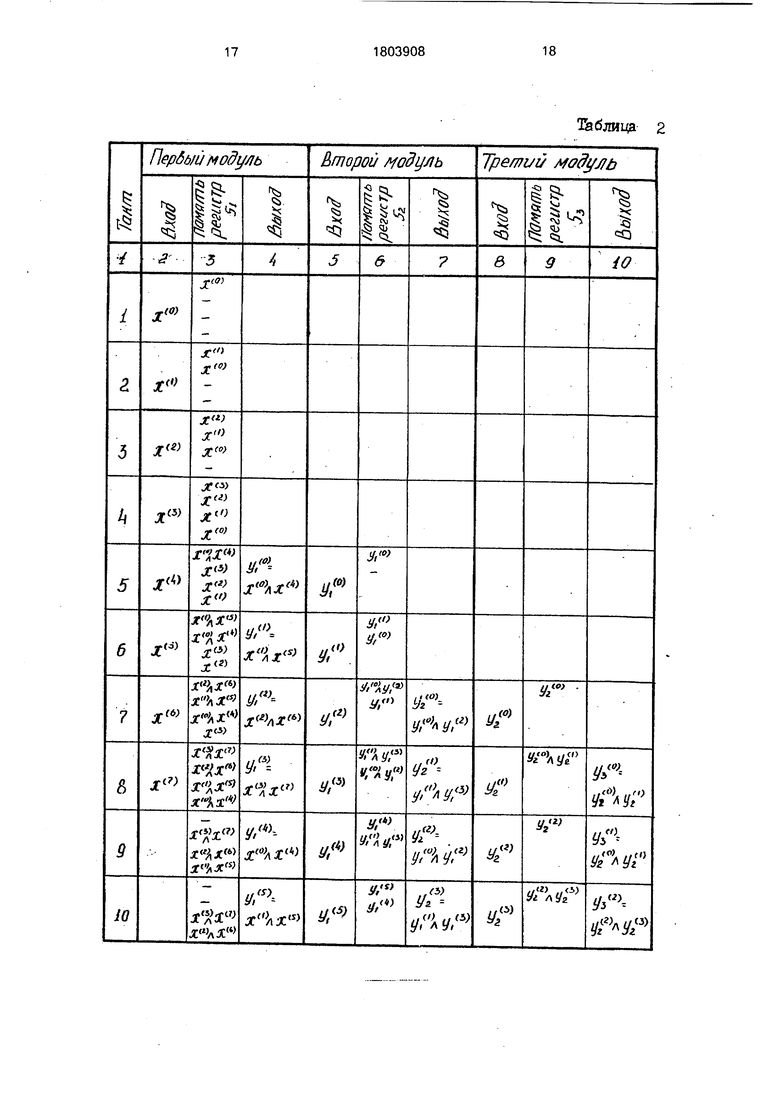

Работу устройства поясняют табл, 2 и фиг. 4-6. В табл. 2 отражено взаимодействие модулей (содержимое регистра 5 каждого

и

модуля) при вычислении минимума буле вой функции, заданной вектором значений

X .., по переменным xi, X2 и хз,

Предварительно на втором и первом управляющих входах i-ro модуля устанавливается соответственно низкий и высокий логические уровни напряжения, которые регламентируют вычисление минимума по переменной Xj.

На первом такте (момент времени , фиг. 4) первый элемент поступает на информационный вход первого модуля и через коммутатор 2i записывается в первый разряд регистра 5i. Аналогично на втором,

третьем и четвертом тактах в регистр 5i записываются значения элементов х л , х 3 вектора Х х(о5х(1)...хЦт

В момент времени t4 (фиг. 5) триггер 11, устанавливается в единичное состояние. В

результате на пятом такте выполняется конъюнкция элемента х , поступившего с выхода регистра 5i через второй Зт и третий 4i коммутаторы на вход элемента И 9, и элемента х л поступившего со второго выхода первого коммутатора 2i на первый вход третьего коммутатора 6i и далее на другой вход элемента И 9i. Результат конъюнкции У. через элемент ИЛИ 8i и первый коммутатор 2i записывается в

регистр 5i, а также через второй коммутатор 3i поступает на информационный выход первого модуля. С информационного выхода первого модуля уг передается на информационный вход второго модуля и далее

на первый информационный вход первого коммутатора 2г второго модуля. На шестом такте (момент времени ts-te) на информационный выход первого модуля поступает результат уг1 , который также через

первый коммутатор 4i записывается в регистр 5i. На седьмом и восьмом тактах на информационный выход первого модуля поступают соответственно результаты хЮ и yi& хЮ. Кроме того.,

по окончании восьмого такта в регистре 5i оказываются записанными элементы У1 , yi , yi , уг - элементы второго из

50

пары равных векторов вектора результата MIN X(MIN Хи MIN К.

XI

XI

XI

На девятом такте вычислений с выхода регистра 5i на информационный выход первого модуля поступают значения элемента уг4 уг результата, а на десятом-двенад- цатом тактах - соответственно значения -yi -yi yij-yi вектора Yi yi(1W2)...yil7) MINX Кроме того, на

х1 девятом такте на третий вход первого модуля могут поступать и обрабатываться элементы вектора значений Х следующей функции f(X ).

Таким образом, на первых четырех тактах выполняется загрузка первого модуля значениями элементов вектора X , на следующих восьми - выдача результата, причем, начиная с девятого такта может осуществляться загрузка первого модуля элементами следующего вектора X .

Функционирование второго модуля, обеспечивающего вычисление минимума по переменной ха, начинается на пятом такте функционирования устройства (момент времени T4J.

На первых двух тактах функционирования второго модуля (момент времени , ) происходит загрузка в регистр 5а элементов уг и уг вектора значений YUyi V LyW

На третьем такте функционирования второго модуля (момент времени te-t) вычисляется конъюнкция у2 yi луг , и результат у2 поступает на информационный выход второго модуля и, кроме того, записы- вается в регистр 5а. К концу четвертого такта функционирования второго модуля (момент времени ty-ts) на информационный выход второго модуля поступает результат уа- угл У1 , а в регистре 52 оказываются записанными значения уа ° и yz . На пятом и щестом тактах функционирования второго модуля (моменты времени ts-tg и tg-tio) соответственно на информационный выход второго модуля с выхода регистра 5а по- ступают значения элементов у2 У2 и уа уа , и в регистр 52 записываются значения элементов уг и уг вектора YI. На седьмом-восьмом тактах функционирования второго модуля (моменты времени tiOf-tn tn-tia) соответственно на информационный выход второго модуля поступают элементыу2(4) yi /ч уг6 и уа(5) yi(5k уг) вектора Y2, а на девятом-десятом тактах (моменты времени Ti2-ti3 ) - результаты у2№) у2(4) и уа уа с выхода регистра 52.

Таким образом, на первых двух тактах происходит загрузка второго модуля, а на следующих восьми - выдача результата Y2 y2(0)y(1)...y2(7)T .

Х2 Х1

Функционирование третьего модуля обеспечивает вычисление минимума булевой функции по переменной хз и начинается на седьмом такте функционирования уст- рорства (момент времени ). На первом такте функционирования третьего модуля происходит загрузка регистра 5 первым элементом уа вектора значений а. На втором такте функционирования третьего модуля (момент времени t7-ts) выполняется конъюнкция элементов уз уа А У2 . Результат уз поступает на информационный выход третьего модуля и,- кроме того, записывается в регистр 5з. На третьем такте функционирования третьего модуля (момент времени ta-tg) результат уз уз с выхода регистра 5з поступает на информационный выход третьего модуля, при этом происходит загрузка модуля значением элемента уа . Далее на четных тактах (четвертом, шестом, восьмом) происходит формирование результатов конъюнкции соответственно УЗ®/А уА УЗ( - уЛ У2(5° и уз У2 А уа , а на нечетных (пятом, седьмом, девятом) на информационный выход модуля поступают элементы уз уз , уз уз и УЗ уз соответственно.

Итак, на первом такте функционирования третьего модуля выполняется загрузка модуля, а на втором и последующих (по девятый такт включительно) выдача результате:

Уз уз(1)уз(2)--УЗ(7)Т MIN MIN MIN X .

Хз Х2 Xi

Таким образом, модуль для вычисления булевых функций по сравнению с аналогом и прототипом обеспечивает расширение функциональных возможностей за счет нахождения минимумов и максимумов булевой функции на конвейерно-параллельном принципе вычислений.

Формула изобретения Модуль для вычисления булевых функций, содержащий сдвиговый регистр, три коммутатора, Т-триггер, первый элемент ИЛИ и элемент задержки, причем первый информационный вход первого коммутатора соединен с информационным входом модуля, информационный выход которого соединен с первым выходом второго коммутатора, отличающийся тем, что, с целью расширения функциональных возможностей путем вычисления логических минимумов и максимумов булевых функций, он содержит элемент И и второй элемент ИЛИ, причем первый тактовый вход модуля соединен с входом Т-триггера, выход которого соединен с тактовым выходом модуля и первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы которых соединены с первым управляющим входом модуля, второй управляющий вход которого соединен с управляющим входом третьего коммутатора, первый и второй выходы которого соединены с входами элемента И, третий и четвертый выходы третьего коммутатора соединены с входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторым информационным входом первого коммутатора и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом старшего разряда сдвигового регистра, информационный вход которого соединен с первым выходом первого коммутатора, второй

выход которого соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен с вторым выходом второго коммутатора, второй тактовый вход модуля соединен с входом разрешения сдвига сдвигового регистра и входом элемента задержки, выход которого соединен с входом разрешения записи сдвигового регистра,

выход элемента И соединен с вторым входом второго элемента ИЛИ,

Т а б л и ц а I

Таблица 2

19

1803908

20

Продолжение табл. 2

Фиг. 2

13

Пар. 8ход

7-й t/нФ- 8х±

12

1-3 У/7А&.

2-йуиь8к

№ 1-й инФ-В

Инф.

Вх.разрен.зал.

2-й ин&8.

2гиупр.&.

1-йупр.8х.

ТгйинФ-Ь.

1-U иМф-З ;,

15

2-иииф.№

п

Фие.З

;

J L,TTJ /

Ml MX t

I I I

I I II , ,

I I I

fcXD

,

MJ/i/i

-C

Ч Щ ГЩ РЩ I I I I I I I

Ы Ы I I I I I I

(H Hd CD

./

А7//Г x3

i iГ I i ..i i j

Q 1 e 3 «5 tf & 9 Ю H & Q M /5ТАКГЬ /

Рехимы

mm ЗогруЗХО

t-, Ьычусяемие г/ fotfovcr реульяю/яоб а Ьыёочоpesyjb/nosTJod

Фиг .5

Регистр 5- первого модуля ,г«) ы Х х) х

I I I I I I I t I I I I )

-4)

t

fti)

tt ct

IAJC

11} Mj

Ш

rW

r«)

JT

:3)

1 VI Т ) 111

. Л- Ч ..tl it. ff .ft. I . /

%( H У У1 tf Ј i 3 4 5 :6 7 8 . 9 JO t// ,/3 y-f/5

и; (4 1/1X

И)

хм.

« «; /1I

fj) i

IM

1 VI Т ) 111

. Л- Ч ..tl it. ff .ft. I . /

( H У У1 tf Ј 8 . 9 JO t// ,/3 y-f/5

УС. 5

| Модуль для логических преобразований булевых функций | 1989 |

|

SU1667050A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Модуль для вычисления логических производных | 1989 |

|

SU1730617A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-03-23—Публикация

1989-11-09—Подача