Изобретение относится к вычислительной ехнике и радиолокации и предназначено для установления попарного соответствия (отождествления) между двумя наборами пеленгов (углов места и азимутов) и вычисления координат точки пересечения соответствующих Линий положения.

Цель изобретения - повышение быстродействия.

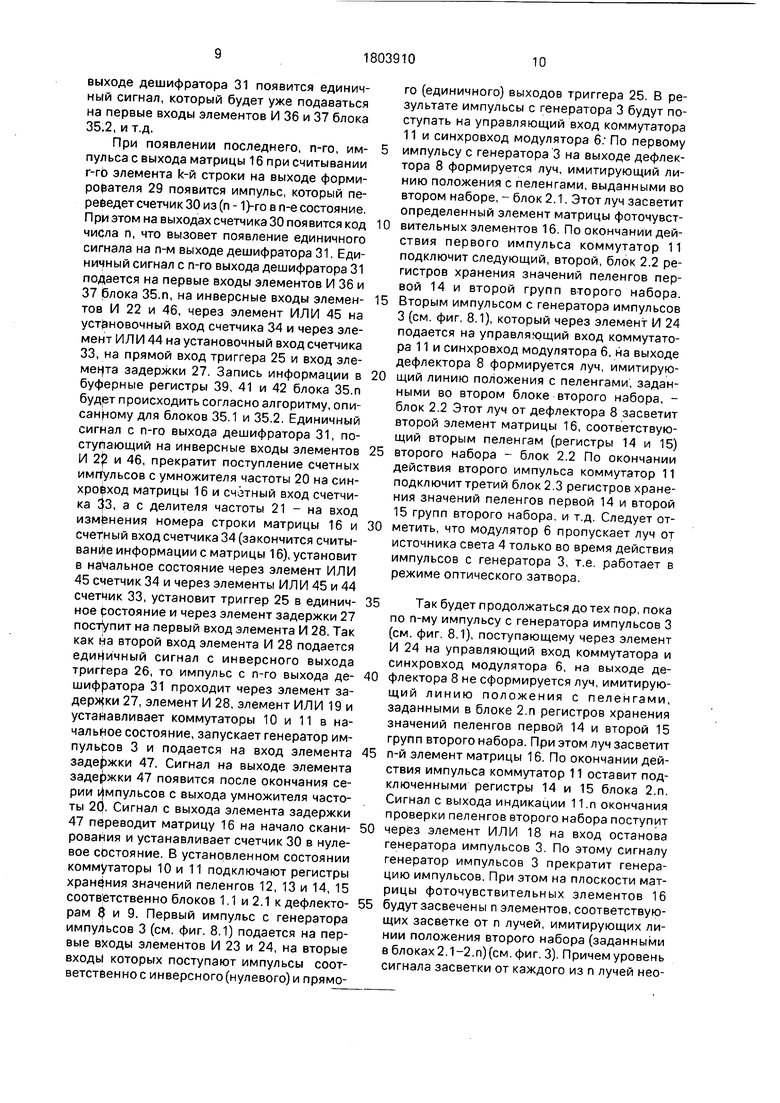

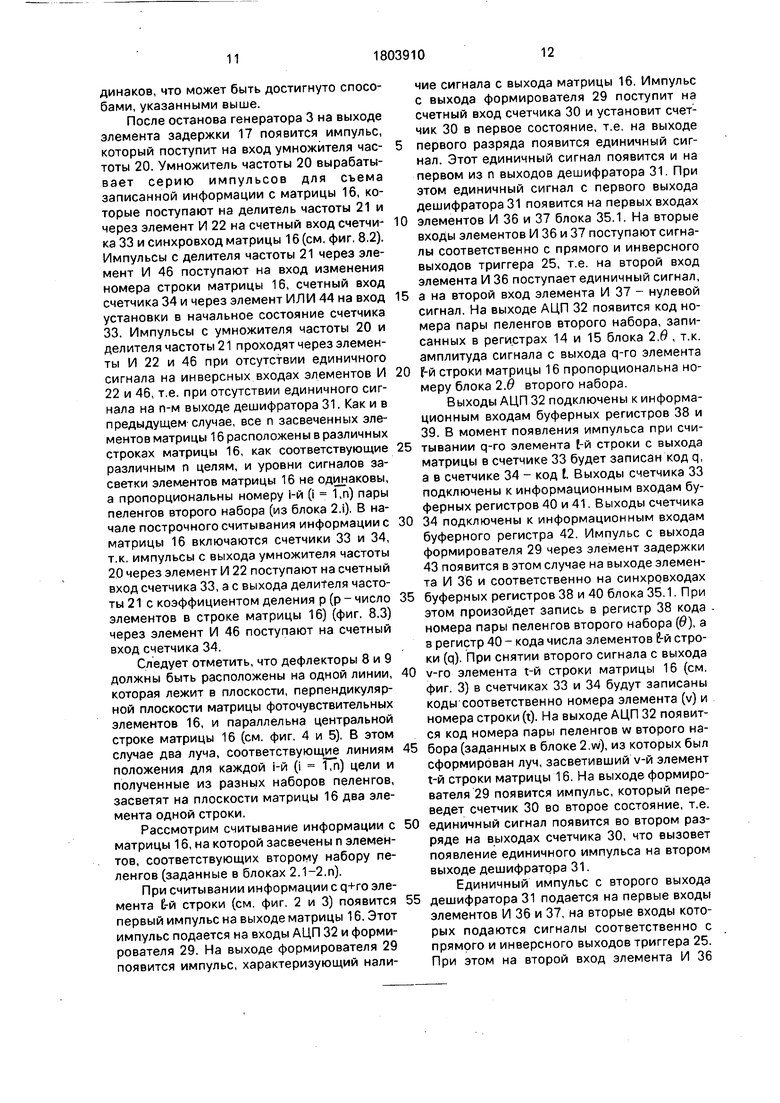

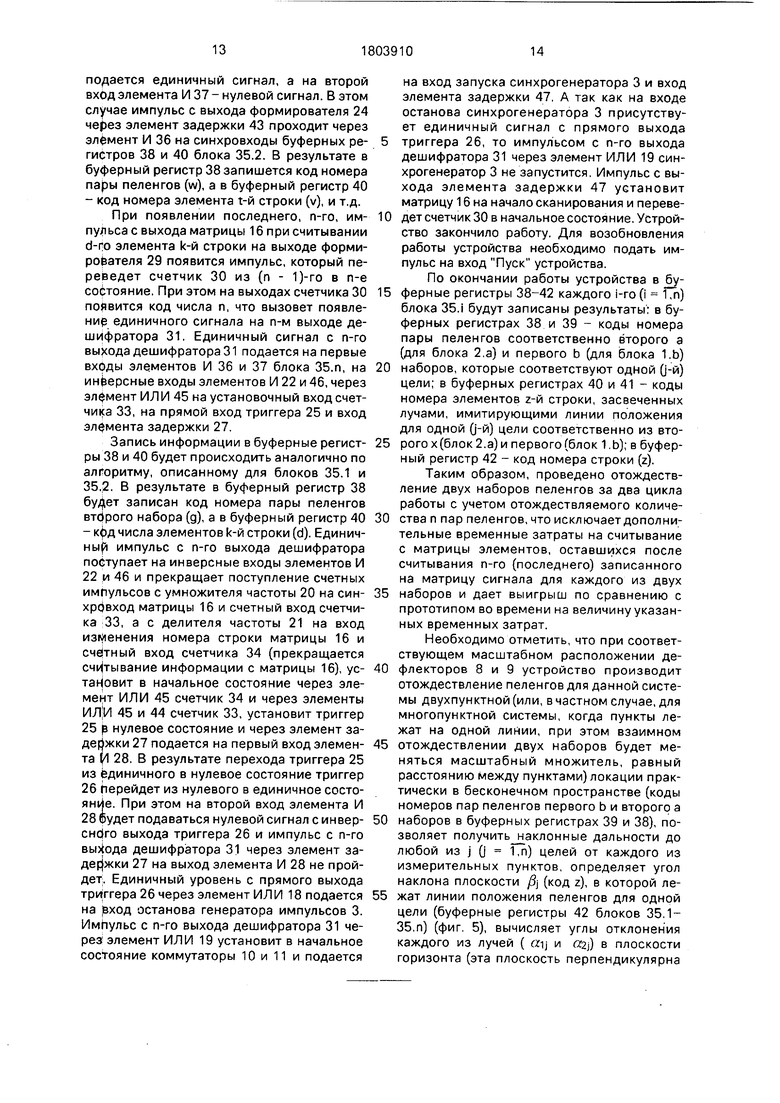

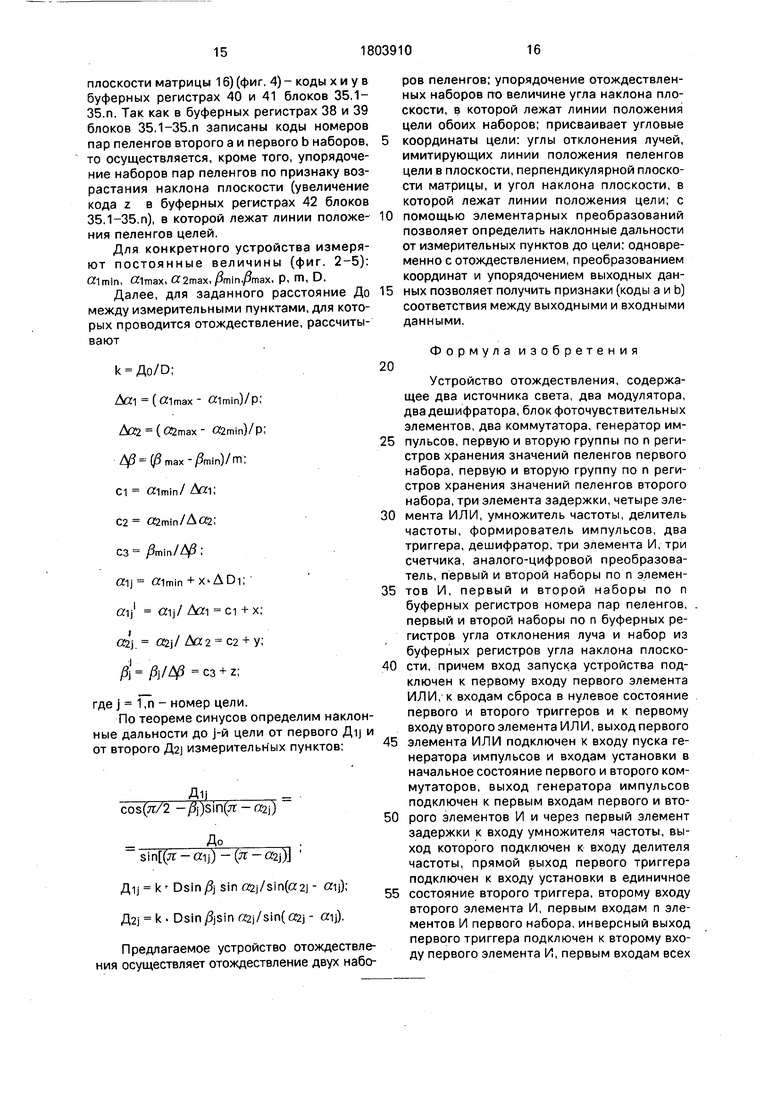

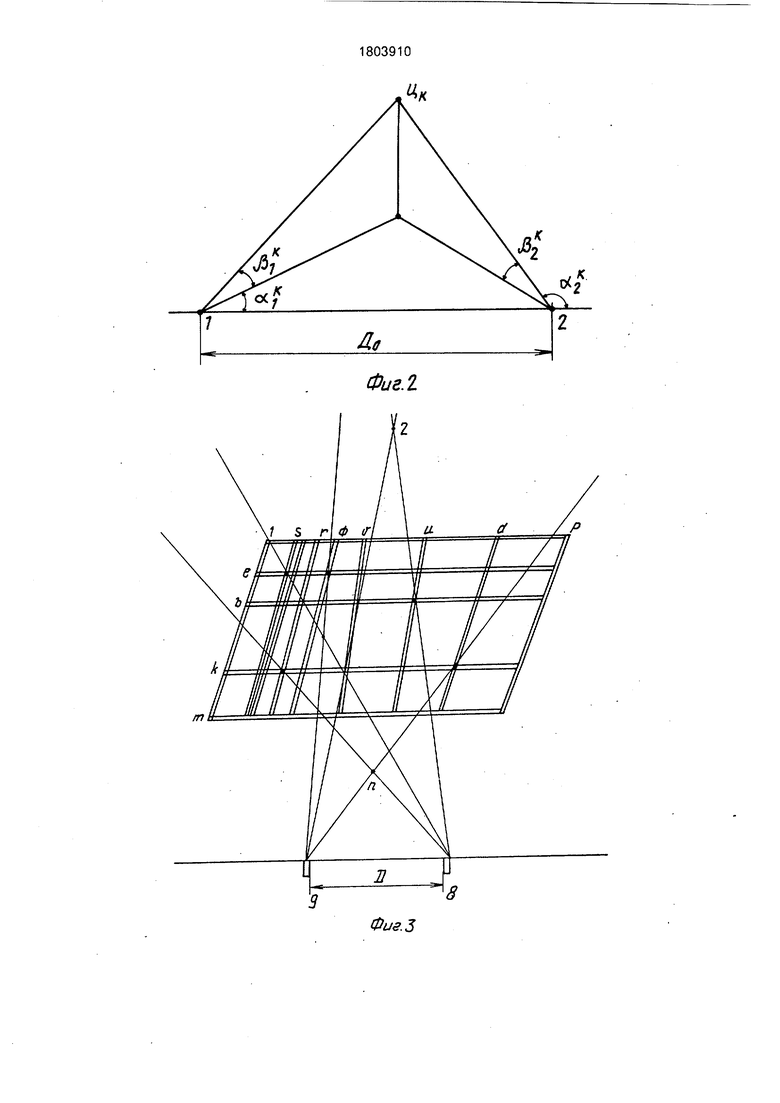

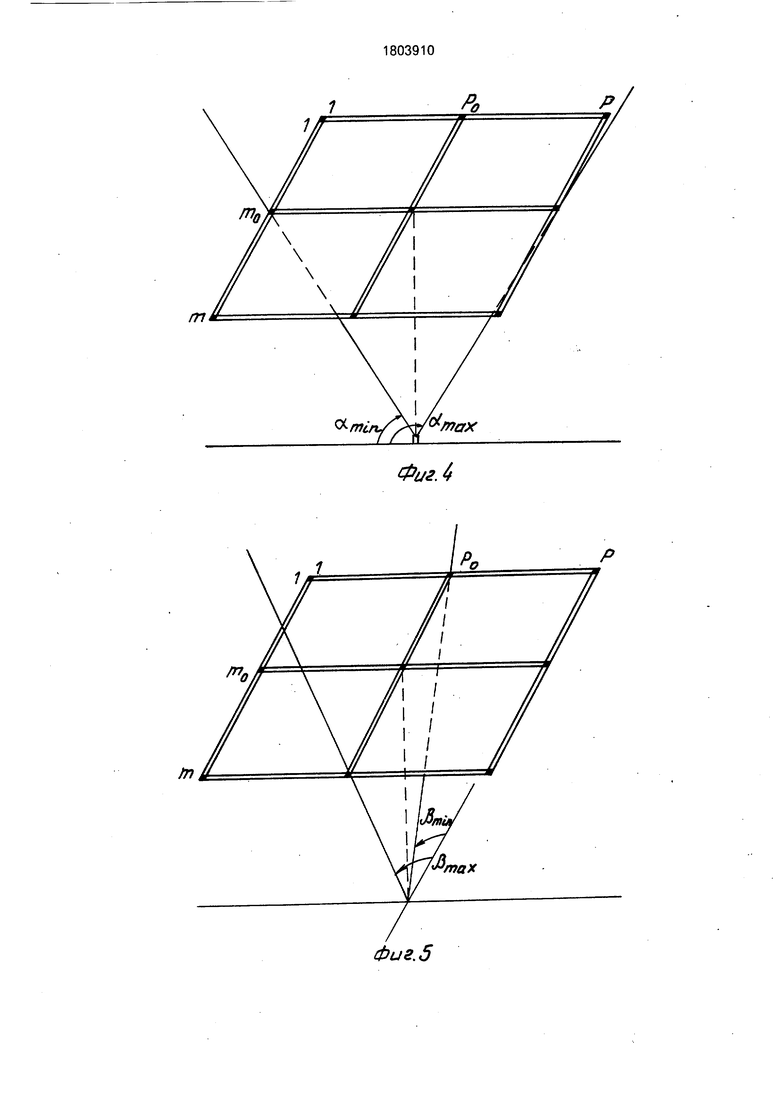

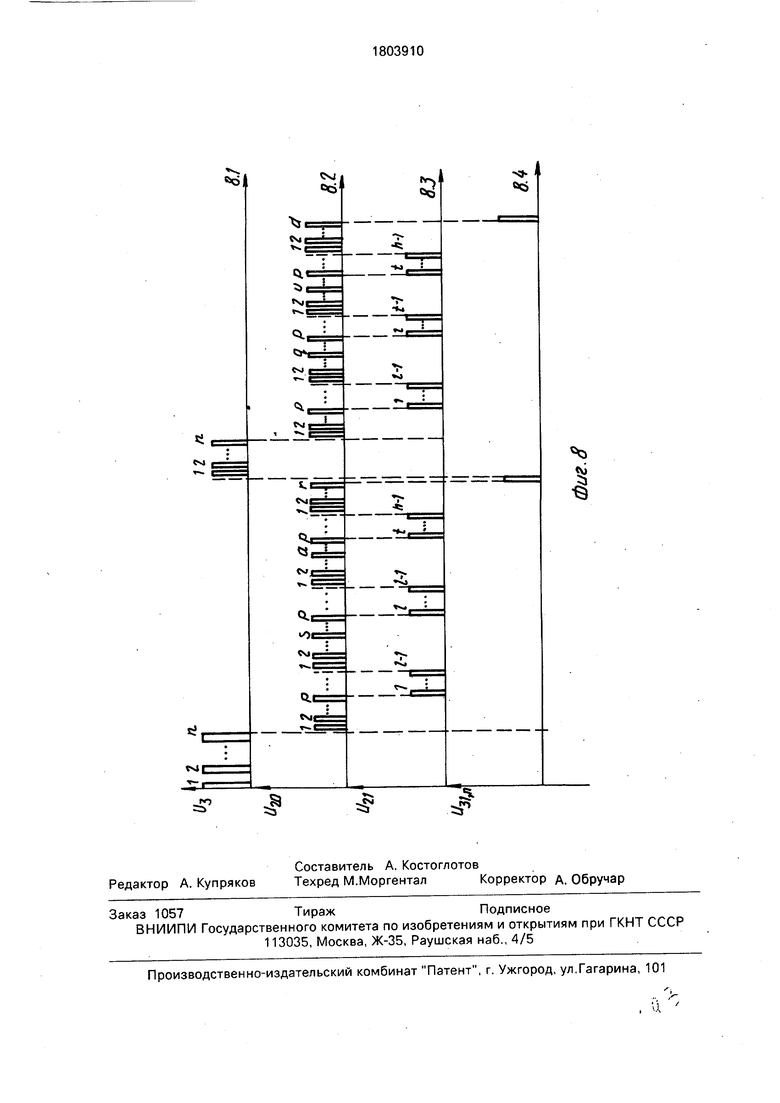

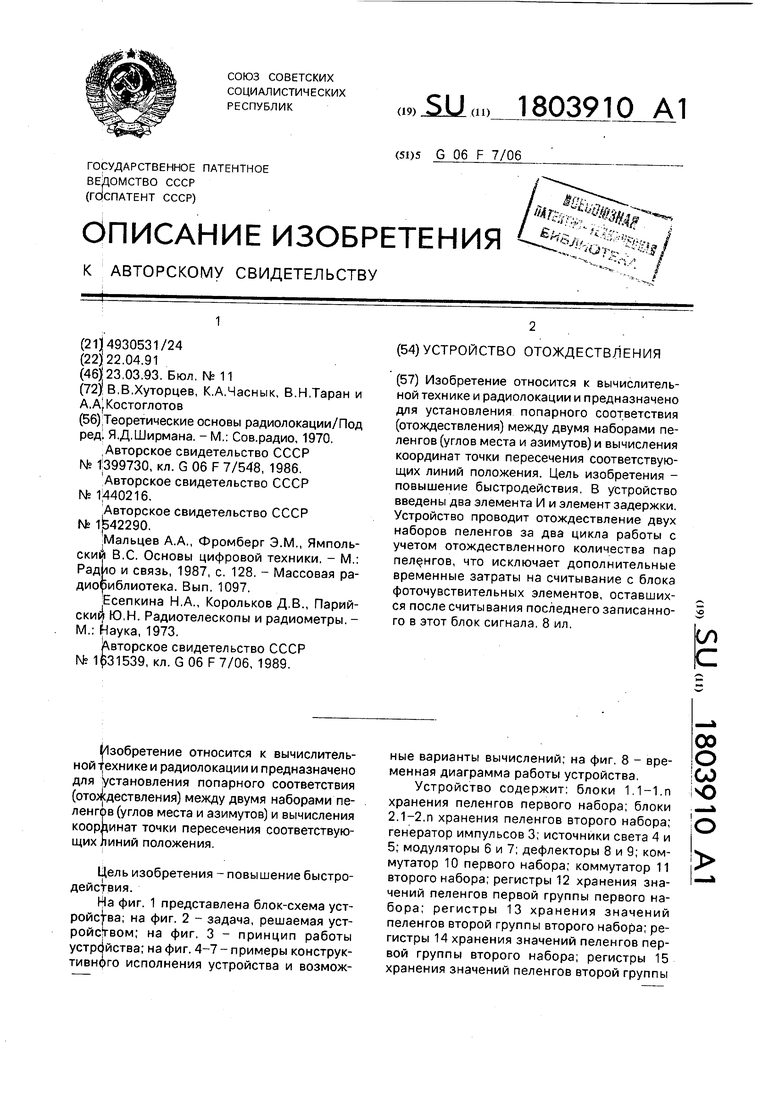

Ьра фиг. 1 представлена блок-схема устройства, на фиг. 2 - задача, решаемая уст- ройс гвом; на фиг. 3 - принцип работы устройства; на фиг. 4-7 - примеры конструктивного исполнения устройства и возможные варианты вычислений; на фиг. 8 - временная диаграмма работы устройства.

Устройство содержит: блоки 1.1-l.n хранения пеленгов первого набора; блоки 2.1-2.П хранения пеленгов второго набора; генератор импульсов 3; источники света 4 и 5; модуляторы 6 и 7; дефлекторы 8 и 9; коммутатор 10 первого набора; коммутатор 11 второго набора; регистры 12 хранения значений пеленгов первой группы первого набора; регистры 13 хранения значений пеленгов второй группы второго набора; регистры 14 хранения значений пеленгов первой группы второго набора; регистры 15 хранения значений пеленгов второй группы

00

о

CJ

о о

второго набора; матрицу 16 фоточувствительных элементов размером m x р; элемента задержки 17; элементы ИЛИ 18 и 19; умножитель частоты 20; делитель частоты 21 (с коэффициентом деления, равным m, m - число элементов строки матрицы фоточувствительных элементов 16); элемент И 22-24; триггеры 25 и 26; элементы задержки 27; элемент И 28; формирователь импульсов 29; счетчик 30; дешифратор 31; аналого-цифро вой преобразователь 32; счетчики 33 и 34; блоки 35.1-35.п хранения результатов; элементы 36 и 37 И; буферные регистры 38 номера пары пеленгов второго набора; буферные регистры 39 номера пары пеленгов первого набора; буферные регистры 40 угла отклонения луча второго набора; буферные регистры 41 угла отклонения луча первого набора; буферные регистры 42 наклона плоскости; элемент задержки 43; элементы ИЛИ 44 и 45; элемент И 46; элемент задержки 47.

Вход Пуск устройства подключен к входу установки в нулевое состояние триггеров 25 и 26 и первым входам элементов ИЛИ 19 и 45. Выход элемента ИЛИ 45 подключен к установочному входу счетчика 34 и первому входу элемента ИЛИ 44, выход которого подключен к установочному входу счетчика 33, Выход элемента ИЛИ 19 подключен к входу пуска генератора импульсов .3, через элемент задержки 47 к входу перехода на начало сканирования матрицы 16 и установочному входу счетчика 30 и входам установки в начальное состояние коммутаторов 10 и. 11. Выход генератора импульсов 3 подключен к первым входам элементов И 23 и 24 и через элемент задержки 17 к входу умножителя частоты 20.

Выход умножителя частоты 20 подключен к входу делителя частоты 21 и к прямому входу элемента И 46. Выход делителя частоты 21 подключен к прямому входу элемента И 46. Выход элемента И 22 подключен к синхровходу матрицы фоточувствительных элементов 16 и счетному входу счетчика 33. Выход элемента И 46 подключен к входу изменения номера строки матрицы фоточувствительных элементов 16, второму входу элемента ИЛИ 44 и счетному входу счетчика 34.

Прямой выход триггера 25 подключен ко входу установки 1 триггера 26, второму входу элемента И 24 и первым входом всех элементов И 36. Выход элемента И 24 подключен к управляющему входу коммутатора 11 и синхровходу модулятора 6. Инверсный выход триггера 25 подкл ючен к второму входу элемента И 23 и первым входам всех элементов И 37. Выход элемента И 23 подключен к управляющему входу коммутатора 10 и синхровходу модулятора 7. Прямой выход триггера 26 подключен к первому входу элемента ИЛИ 18, выход которого подключен к входу останова генератора импульсов 3. Инверсный выход триггера 26 подключен к второму входу элемента И 28, выход которого подключен к второму входу элемента ИЛИ 19. Выходы i-x (i 1 ,п, п - число сорти0 руемых пар пеленгов) регистров хранения значений пеленгов первой 12 и второй 13 групп первого набора 1.1 подключены к входам коммутатора 10, выходы которого подключены к входам управления отклонения

5 луча дефлектора 9. Выходы k-x (k 1 ,п) регистров хранения значений пеленгов первой 14 и второй 15 групп второго набора 2.k подключены к k-м информационным входам коммутатора 11, выходы которого подклю0

чены к входам управления отклонением луча дефлектора 8. Выходы индикации окончания проверки пеленгов первого 10.п и второго 11.п наборов подключены соответственно к второму и третьему входам

5 элемента ИЛИ 18. Источники света 4 и 5 соответственно через модуляторы 6 и 7 и дефлекторы 8 и 9 оптически связаны с матрицей фоточувствительных элементов 16. Выход матрицы фоточувствительных эле0 ментов 16 подключен к информационным, входам формирователя импульсов 29 и ана- лого-цифрового преобразователя (АЦП) 32. Выход формирователя импульсов 29 подключен к входу элемента задержки 43 и счет5 ному входу счетчика 30, выходы которого подключены к информационным входам дешифратора 31.

Примером конструктивного исполнения счетчика 30 и дешифратора 31 может слу0 жить схема, изображенная на фиг. 7. Каждый i-1 (i 1,п) выход дешифратора 31 подключен к вторым входам всех п элементов И 36 и 37, Причем n-й выход дешифрато- . ра 31 подключен к вторым (инверсным)

5 входам элементов И 22 и 46, а также к входу установки в 1 триггера 25, второму входу элемента ИЛИ 45 и через элемент задержки 27 к первому входу элемента И 28. Третьи входы всех элементов И 36 и 37 подключены

0 к выходу элемента задержки 43. Выходы АЦП 32 подключены к информационным входам всех п буферных регистров 39 номера пары пеленгов первого набора и всех п буферных регистров 38 номера пары пелен5 гов второго набора. Выходы счетчика 33 подключены к информационным входам всех п буферных регистров 41 угла отклонения луча первого набора и всех п буферных регистров 40 угла отклонения луча второго набора. Выходы счетчика 34 подключены к

информационным входам всех п буферных регистров наклона плоскости. Выход i-го (i 1,n) элемента И 36 подключен к Јинхровходам соответствующих i-x (i iTn) буферного регистра 38 номера пары пелен- foe второго набора 38 и буферного регистра 40 угла отклонения луча второго набора 40. $ыход i-го (i 1 ,п) элемента И 37 подключен it синхровходам соответствующих i-x (i 1 ,n) буферного регистра 39 номера пары пелен- Нов первого набора и буферного регистра 42 у|гла наклона плоскости. Выходы каждого из ri буферных регистров 38-42 являются информационными выходами устройства.

Устройство работает следующим образрм.

На вход Пуск устройства поступает пусковой импульс, который устанавливает в начальное состояние через элемент ИЛИ 45 сметчик 34 и через элементы ИЛИ 45 и 44 счетчик 33, в нулевое состояние триггеры 25 и 26, а через элемент ИЛИ 19 запускает генератор импульсов 3, устанавливает в на- чгльное состояние коммутаторы 10 и 11, че- риз элемент задержки 47 переводит митрицу фоточувствительных элементов 16 Ш начало сканирования и устанавливает в нулевое состояние счетчик 30. В установленном состоянии коммутатора 10 и 11 под- Ыючает регистры 12-15 хранения значений пеленгов соответственно блоков 1.1 и 2.1 и дефлекторам 8 и 9. Первый импульс с генератора импульсов 3 (см. фиг, 8.1) подается на первые входы элементов И 23 и 24, а так ка с на вторые входы элементов И 23 и 24 по ступают соответственно сигналы с инвер- сн )го (единичный) и прямого (нулевой) выхо- доз триггера 25, то импульс с генератора импульсов 3 поступит на синхровход моду- ля|ора 7 и управляющий вход коммутатора 10J По первому импульсу на выходе дефлектора 9 формируется луч, имитирующий линию положения с пеленгами, заданными в первом наборе, - блок 1.1. Этот луч засветит определенный элемент матрицы фоточувст- вит|ельных элементов 16. По окончании дей- импульса коммутатор 10 подключит следующий, второй, блок 1.2 регистров хра- нейия значений пеленгов первой 12 и вто- рой 13 групп первого набора.

Вторым импульсом с генератора им- 3 (см, фиг. 8.1), который через элемент И 23 подается на управляющий вход коммутатора 10 и синхровход модулятора 7, на ыходе дефлектора 9 формируется луч, имитирующий линию положения с пеленгами, заданными во втором блоке первого на- бор|а - блок 1.2. Луч от дефлектора 9 засветит второй элемент матрицы фоточув0

5

0 5 0 5 0 5 0

5

ствительных элементов 16, соответствующий вторым пеленгам (регистры 12 и 13) первого набора - блок 1.2. По окончании действия второго импульса коммутатор 10 подключит третий блок 1,3 регистров хранения значений пеленгов первой 12 и второй 13 групп первого набора, и т.д. Следует отметить, что модулятор 7 пропускает луч от источника света 5 только во время действия импульсов с генератора 3, т.е. работает в режиме оптического затвора. Так будет продолжаться до тех пор, пока пол-му импульсу с генератора импульсов 3 (см. фиг. 8.1), поступающему через элемент И 23 на управляющий вход коммутатора 10 и синхровход модулятора 7, на выходе дефлектора 9 не сформируется луч, имитирующий линию положения с пеленгами, заданными 6 n-м блоке 1.п регистров хранения значений пеленгов первой 12 и второй 13 групп первого набора. При этом луч засветит n-й элемент матрицы фоточувствительных элементов 16. По окончании действия импульса коммутатор 10 оставит подключенными регистры 12 и 13 в блоке 1.п. Сигнал с выхода индикации 10.п окончания проверки пеленгов первого набора поступит через элемент ИЛИ 18 на вход останова генератора импульсов 3. По этому сигналу генератор импульсов 3 прекратит генерацию импульсов. При этом на плоскости матрицы фото- чувствительных элементов 16 будут засвечены п элементов, соответствующих засветке от п лучей, имитирующих линии положения первого набора (блоки 1.1-1.п) (см. фиг. 3). Причем уровень сигнала засветки от каждого из п лучей неодинаков, что может быть достигнуто линейным увеличением длительности импульсов в пачке из п импульсов генератора 3 или модуляцией луча в модуляторе 6.

Третьим вариантом модуляции засветки элемента матрицы 16 может служить схемное построение коммутатора 10, для которого переключение из i-ro в (i + 1)-е состояние будет осуществляться только при поступлении пачки из i импульсов (при этом соответственно изменится фиг. 8.1). После останова генератора импульсов 3 появится импульс на выходе элемента задержки 17, который поступит на вход умножителя частоты 20. Умножитель частоты 20 вырабатывает серию импульсов для съема записанной информации с матрицы фоточувствительных элементов 16, которые поступают на делитель частоты 21 и через элемент И 22 на счетный вход счетчика 33 и синхровход матрицы 16 (см. фиг. 8.2). Импульсы с делителя частоты 21 через элемент И 46 поступают на вход изменения номера строки матрицы фоточувствительных элементов 16 и счетный вход счетчика 34 и элемент ИЛИ 44. Заметим, что импульсы с умножителя частоты 20 и с делителя частоты 21 проходят через элементы И 22 и 46 только до момента появле- ния импульса на n-м выходе дешифратора 31. Необходимо также отметить, что все п засвеченных элементов матрицы 16 расположены в различных строках матрицы 16, как соответствующие различным п целям, и уровни сигналов засветки элементов матрицы 16 неодинаковы, а пропорциональны номеру 1-й (I 1,п) пары пеленгов первого набора (от блока 1.1).

В начале построчного считывания ин- формации с матрицы 16 включаются счетчики 33 и 34, т.к. импульсы с выхода умножителя частоты 20 через элемент И 22 поступают на счетный вход счетчика 33, а с выхода делителя частоты 21с коэффициен- том деления р (р - число элементов в строке матрицы 16) (фиг. 8.3) через элемент I/I 46 поступают на счетный вход счетчика 34.

Отметим, что установка в начальное состояние (сброс) счетчика 34 осуществляется по заданному фронту импульса, поступающего через элемент ИЛИ 45 с входа запуска устройства или с n-го выхода дешифратора 31. Установка в начальное состояние (сброс) счетчика 33 осуществляется подачей им- пульса через элемент ИЛИ 44 с выхода элемента ИЛИ 45 или с выхода делителя частоты 21 через элемент И 22. Таким образом, счетчик 34 сбрасывается в м омент запуска устройства и в момент появления сигнала на n-м выходе дешифратора 31, т.е. после снятия последнего, n-го, засвеченного элемента матрицы 16 до окончания полного сканирования матрицы 16 (см. фиг. 8.3). Счетчик 33 сбрасывается в момент запуска устройства, в момент окончания снятия информации с каждой строки матрицы 16 и в момент снятия последнего, n-го, засвеченного элемента матрицы 16 (см, фиг. 8.2).

Рассмотрим считывание информации с матрицы 16 (см. фиг. 3). При считывании сигнала с S-ro элемента 1-й строки появится импульс на входах АЦП 32 и формирователя импульсов 29. При этом на выходе АЦП 32 появится код номера пары пеленгов перво- го набора, записанных в регистрах 12 и 13 блока l.i, т.к. амплитуда сигнала с выхода S-ro элемента fc-й строки матрицы 16 пропорциональна номеру блока 1.1 первого набора. На выходе формирователя импульсов 29 независимо от амплитуды поступающего сигнала появится импульс, характеризующий наличие сигнала на выходе матрицы 16. Этот импульс с выхода формирователя 24 поступает на счетный вход счетчика 30.

Предположим, что до появления данного сигнала с S-ro элемента 1-й строки матрицы 16 при считывании информации с матрицы 16 других сигналов еще не появлялось, т.е. t-я строка матрицы 16 является первой с начала считывания/где засвечен лучом элемент матрицы 16. Остальные п -1 засвеченных элементов матрицы 16 расположены в оставшихся (т - |)(т - Е) п -1 строках матрицы 16, где m - число строк в матрице 16. Тогда, при поступлении импульса на счетный вход счетчика 30 на выходе первого разряда счетчика 30 появится единица. Этот единичный сигнал появится и на первом из п выходов дешифратора 31. При этом единичный сигнал с первого выхода дешифратора 31 появится на первых входах элементов И 36 и 37 блока 35.1. А так как на вторые входы элементов И 36 и 37 поступают сигналы соответственно с прямого и инверсного выходов триггера 25, то на второй вход элемента И 36 поступает нулевой сигнал, а на второй вход элемента И 37 - единичный сигнал. Тогда единичный импульс с выхода формирователя 29 через элемент задержки 43 появится только на выходе элемента И 37 и соответственно появится единичный импульс на синхровходах буферных регистров 39, 41 и 42 блока 35.1. В момент появления сигналы с выхода S-ro элемента -й строки матрицы 16 в счетчиках 33 и 34 будут записаны коды соответственно номера элемента строки (S) и номера строки (Е). Эти коды с выходов счетчиков 33 и 34 поступают на информационные входы буферных регистров соответственно 40-42. По единичному импульсу с выхода элемента И 37 произойдет запись информации в буферные регистры 39, 41 и 42. При этом в буферный регистр 41 запишется код номера засвеченного элемента (S) матрицы 16, в буферный регистр 42 запишется код номера считываемой строки (Q матрицы 16, а в буферный регистр 39 запишется код номера пары пеленгов i первого набора, заданных в блоке 1.1, из которых был сформирован луч, засветивший S-й элемент t-й строки матрицы 16. При снятии второго сигнала с выхода n-го элемента t-й строки (t ty матрицы 16 в счетчиках 33 и 34 будут записаны соответственно коды номера элемента (и) и номера строки (t) на выходе АЦП 32 появится код номера пары пеленгов первого набора, заданных в блоке 1.J, из которых был сформирован луч, засветивший u-й элемент t-й строки матрицы 16. На выходе формирователя 29 появится импульс, который переведет счетчик 30 в следующее состояние, т.е. единичный сигнал появится на выходе второго разряда счетчика 30 и при этом на

выходе дешифратора 31 появится единичный сигнал, который будет уже подаваться на первые входы элементов И 36 и 37 блока 35.2, и т.д.

При появлении последнего, n-го, импульса с выхода матрицы 16 при считывании г-го элемента k-й строки на выходе формирователя 29 появится импульс, который переведет счетчик 30 из (п - 1)-го в n-е состояние. При этом на выходах счетчика 30 появится код числа п, что вызовет появление единичного сигнала на n-м выходе дешифратора 31. Единичный сигнал с n-го выхода дешифратора 31 подается на первые входы элементов И 36 и 37 блока 35.п, на инверсные входы элементов И 22 и 46, через элемент ИЛИ 45 на установочный вход счетчика 34 и через элемент ИЛИ 44 на установочный вход счетчика 33, на прямой вход триггера 25 и вход элемента задержки 27. Запись информации в буферные регистры 39, 41 и 42 блока 35,п будет происходить согласно алгоритму, описанному для блоков 35.1 и 35.2. Единичный сигнал с n-го выхода дешифратора 31, поступающий на инверсные входы элементов И 2 и 46, прекратит поступление счетных имгтульсов с умножителя частоты 20 на син- хро&ход матрицы 16 и счбтный вход счетчика 33, а с делителя частоты 21 - на вход изменения номера строки матрицы 16 и счетный вход счетчика 34 (закончится считывание информации с матрицы 16), установит в начальное состояние через элемент ИЛИ 45 счетчик 34 и через элементы ИЛИ 45 и 44 счетчик 33, установит триггер 25 в единичное ростояние и через элемент задержки 27 поступит на первый вход элемента И 28. Так как на второй вход элемента И 28 подается единичный сигнал с инверсного выхода триггера 26, то импульс с л-го выхода дешифратора 31 проходит через элемент за- 27, элемент И 28, элемент ИЛИ 19 и устанавливает коммутаторы 10 и 11 в начальное состояние, запускает генератор импульсов 3 и подается на вход элемента задержки 47. Сигнал на выходе элемента задержки 47 появится после окончания серии мпульсов с выхода умножителя частоты 20. Сигнал с выхода элемента задержки 47 переводит матрицу 16 на начало сканирования и устанавливает счетчик 30 в нулевое состояние. В установленном состоянии коммутаторы 10 и 11 подключают регистры хранения значений пеленгов 12, 13 и 14, 15 соответственно блоков 1,1 и 2.1 к дефлекторам $ и 9. Первый импульс с генератора импульсов 3 (см. фиг. 8.1) подается на первые входы элементов И 23 и 24, на вторые входы которых поступают импульсы соответственно с инверсного (нулевого) и прямого (единичного) выходов триггера 25. В результате импульсы с генератора 3 будут поступать на управляющий вход коммутатора 11 и синхровход модулятора б: По первому

импульсу с генератора 3 на выходе дефлектора 8 формируется луч, имитирующий линию положения с пеленгами, выданными во втором наборе, - блок 2.1. Этот луч засветит определенный элемент матрицы фоточувствительных элементов 16. По окончании действия первого импульса коммутатор 11 подключит следующий, второй, блок 2.2 регистров хранения значений пеленгов первой 14 и второй групп второго набора.

Вторым импульсом с генератора импульсов 3 (см. фиг, 8.1), который через элемент И 24 подается на управляющий вход коммутатора 11 и синхровход модулятора 6, на выходе дефлектора 8 формируется луч, имитирующий линию положения с пеленгами, заданными во втором блоке второго набора, - блок 2.2 Этот луч от дефлектора 8 засветит второй элемент матрицы 16, соответствующий вторым пеленгам (регистры 14 и 15)

второго набора - блок 2.2 По окончании действия второго импульса коммутатор 11 подключит третий блок 2.3 регистров хранения значений пеленгов первой 14 и второй 15 групп второго набора, и т.д. Следует отметить, что модулятор 6 пропускает луч от источника света 4 только во время действия импульсов с генератора 3, т.е. работает в режиме оптического затвора.

Так будет продолжаться до тех пор, пока по n-му импульсу с генератора импульсов 3 (см. фиг. 8.1), поступающему через элемент И 24 на управляющий вход коммутатора и синхровход модулятора 6, на выходе дефлектора 8 не сформируется луч, имитирующий линию положения с пеленгами, заданными в блоке 2,п регистров хранения значений пеленгов первой 14 и второй 15 групп второго набора. При этом луч засветит

n-й элемент матрицы 16. По окончании действия импульса коммутатор 11 оставит подключенными регистры 14 и 15 блока 2.п. Сигнал с выхода индикации 11.п окончания проверки пеленгов второго набора поступит

через элемент ИЛИ 18 на вход останова генератора импульсов 3. По этому сигналу генератор импульсов 3 прекратит генерацию импульсов. При этом на плоскости матрицы фоточувствительных элементов 16

будут засвечены п элементов, соответствующих засветке от п лучей, имитирующих линии положения второго набора (заданными в блоках 2,1-2.п) (см. фиг. 3). Причем уровень сигнала засветки от каждого из п лучей неодинаков, что может быть достигнуто способами, указанными выше.

После останова генератора 3 на выходе элемента задержки 17 появится импульс, который поступит на вход умножителя частоты 20. Умножитель частоты 20 вырабатывает серию импульсов для съема записанной информации с матрицы 16, которые поступают на делитель частоты 21 и через элемент И 22 на счетный вход счетчика 33 и синхровход матрицы 16 (см. фиг. 8.2). Импульсы с делителя частоты 21 через элемент И 46 поступают на вход изменения номера строки матрицы 16, счетный вход счетчика 34 и через элемент ИЛИ 44 на вход установки в начальное состояние счетчика 33. Импульсы с умножителя частоты 20 и делителя частоты 21 проходят через элементы И 22 и 46 при отсутствии единичного сигнала на инверсных входах элементов И 22 и 46, т.е. при отсутствии единичного сигнала на n-м выходе дешифратора 31. Как и в предыдущем случае, все п засвеченных элементов матрицы 16 расположены в различных строках матрицы 16, как соответствующие различным п целям, и уровни сигналов засветки элементов матрицы 16 не одинаковы, а пропорциональны номеру i-й (i 1,n) пары пеленгов второго набора (из блока 2.1), В начале построчного считывания информации с матрицы 16 включаются счетчики 33 и 34, т.к. импульсы с выхода умножителя частоты 20 через элемент И 22 поступают на счетный вход счетчика 33, а с выхода делителя частоты 21 с коэффициентом деления р (р - число элементов в строке матрицы 16) (фиг. 8.3) через элемент И 46 поступают на счетный вход счетчика 34.

Следует отметить, что дефлекторы 8 и 9 должны быть расположены на одной линии, которая лежит в плоскости, перпендикулярной плоскости матрицы фоточувствительных элементов 16, и параллельна центральной строке матрицы 16 (см. фиг. 4 и 5). В этом случае два луча, соответствующие линиям положения для каждой i-й (i 1,n) цели и полученные из разных наборов пеленгов, засветят на плоскости матрицы 16 два элемента одной строки.

Рассмотрим считывание информации с матрицы 16, на которой засвечены п элементов, соответствующих второму набору пеленгов (заданные в блоках 2.1-2.п).

При считывании информации с q+ro элемента t-й строки (см. фиг. 2 и 3) появится первый импульс на выходе матрицы 16. Этот импульс подается на входы АЦП 32 и формирователя 29. На выходе формирователя 29 появится импульс, характеризующий наличие сигнала с выхода матрицы 16. Импульс с выхода формирователя 29 поступит на счетный вход счетчика 30 и установит счетчик 30 в первое состояние, т.е. на выходе

первого разряда появится единичный сигнал. Этот единичный сигнал появится и на первом из п выходов дешифратора 31. При этом единичный сигнал с первого выхода дешифратора 31 появится на первых входах

элементов И 36 и 37 блока 35.1. На вторые входы элементов И 36 и 37 поступают сигналы соответственно с прямого и инверсного выходов триггера 25, т.е. на второй вход элемента И 36 поступает единичный сигнал,

а на второй вход элемента И 37 - нулевой сигнал. На выходе АЦП 32 появится код номера пары пеленгов второго набора, записанных в регистрах 14 и 15 блока 2.9 , т.к. амплитуда сигнала с выхода q-ro элемента

t-й строки матрицы 16 пропорциональна номеру блока 2.0 второго набора.

Выходы АЦП 32 подключены к информационным входам буферных регистров 38 и 39. В момент появления импульса при считывании q-ro элемента 1-й строки с выхода матрицы в счетчике 33 будет записан код q, а в счетчике 34 - код I. Выходы счетчика 33 подключены к информационным входам буферных регистров 40 и 41. Выходы счетчика

34 подключены к информационным входам буферного регистра 42, Импульс с выхода формирователя 29 через элемент задержки 43 появится в этом случае на выходе элемента И 36 и соответственно на синхровходах

буферных регистров 38 и 40 блока 35.1. При этом произойдет запись в регистр 38 кода номера пары пеленгов второго набора (6), а в регистр 40 - кода числа элементов 2-й строки (q). При снятии второго сигнала с выхода

v-ro элемента t-й строки матрицы 16 (см. фиг. 3) в счетчиках 33 и 34 будут записаны коды соответственно номера элемента (v) и номера строки (t). На выходе АЦП 32 появится код номера пары пеленгов w второго набора (заданных в блоке 2.w), из которых был сформирован луч, засветивший v-й элемент t-й строки матрицы 16. На выходе формирователя 29 появится импульс, который переведет счетчик 30 во второе состояние, т.е.

единичный сигнал появится во втором разряде на выходах счетчика 30, что вызовет появление единичного импульса на втором выходе дешифратора 31.

Единичный импульс с второго выхода

дешифратора 31 подается на первые входы элементов И 36 и 37, на вторые входы которых подаются сигналы соответственно с прямого и инверсного выходов триггера 25. При этом на второй вход элемента И 36

подается единичный сигнал, а на второй вход элемента И 37 - нулевой сигнал. В этом случае импульс с выхода формирователя 24 через элемент задержки 43 проходит через элемент И 36 на синхровходы буферных ре- гистров 38 и 40 блока 35.2. В результате в буферный регистр 38 запишется код номера пары пеленгов (w), а в буферный регистр 40

- код номера элемента t-й строки (v), и т.д.

При появлении последнего, n-го, им- пульса с выхода матрицы 16 при считывании d-ro элемента k-й строки на выходе формирователя 29 появится импульс, который переведет счетчик 30 из (п - 1)-го в п-е состояние. При этом на выходах счетчика 30 появится код числа п, что вызовет появление единичного сигнала на n-м выходе дешифратора 31. Единичный сигнал с п-го выхода дешифратора 31 подается на первые входы элементов И 36 и 37 блока 35.п, на инёерсные входы элементов И 22 и 46, через элемент ИЛ И 45 на установочный вход счетчика 33, на прямой вход триггера 25 и вход элемента задержки 27.

Запись информации в буферные регист- ры 38 и 40 будет происходить аналогично по алгоритму, описанному для блоков 35.1 и 35,2. В результате в буферный регистр 38 бу4ет записан код номера пары пеленгов втброго набора (д), а в буферный регистр 40

- кбд числа элементов k-й строки (d). Единичный импульс с n-го выхода дешифратора поступает на инверсные входы элементов И 22 и 46 и прекращает поступление счетных импульсов с умножителя частоты 20 на син- хровход матрицы 16 и счетный вход счетчика i33, а с делителя частоты 21 на вход изменения номера строки матрицы 16 и счётный вход счетчика 34 (прекращается считывание информации с матрицы 16), ус- тановит в начальное состояние через элемент ИЛИ 45 счетчик 34 и через элементы ИЛ:И 45 и 44 счетчик 33, установит триггер

25 р нулевое состояние и через элемент задержки 27 подается на первый вход элемен- та И 28. В результате перехода триггера 25 из единичного в нулевое состояние триггер

26 Перейдет из нулевого в единичное состояние. При этом на второй вход элемента И 28 шудет подаваться нулевой сигнал с инвер- сноУо выхода триггера 26 и импульс с п-го вывода дешифратора 31 через элемент задержки 27 на выход элемента И 28 не пройдет. Единичный уровень с прямого выхода триггера 26 через элемент ИЛ И 18 подается на (вход останова генератора импульсов 3. Импульс с n-го выхода дешифратора 31 через1 элемент ИЛИ 19 установит в начальное состояние коммутаторы 10 и 11 и подается

на вход запуска синхрогенератора 3 и вход элемента задержки 47. А так как на входе останова синхрогенератора 3 присутствует единичный сигнал с прямого выхода триггера 26, то импульсом с n-го выхода дешифратора 31 через элемент ИЛИ 19 син- хрогенератор 3 не запустится. Импульс с выхода элемента задержки 47 установит матрицу 16 на начало сканирования и переведет счетчик 30 в начальное состояние. Устройство закончило работу. Для возобновления работы устройства необходимо подать импульс на вход Пуск устройства.

По окончании работы устройства в бу- ферные регистры 38-42 каждого i-ro(i 1,п) блока 35. будут записаны результаты: в буферных регистрах 38 и 39 - коды номера пары пеленгов соответственно второго а (для блока 2.а) и первого b (для блока 1.Ь) наборов, которые соответствуют одной (j-й) цели; в буферных регистрах 40 и 41 - коды номера элементов z-й строки, засвеченных лучами, имитирующими линии положения для одной (j-й) цели соответственно из второго х(блок 2.а) и первого (блок 1 .Ь); в буферный регистр 42 - код номера строки (z).

Таким образом, проведено отождествление двух наборов пеленгов за два цикла работы с учетом отождествляемого количества п пар пеленгов, что исключает дополнительные временные затраты на считывание с матрицы элементов, оставшихся после считывания n-го (последнего) записанного на матрицу сигнала для каждого из двух наборов и дает выигрыш по сравнению с прототипом во времени на величину указанных временных затрат.

Необходимо отметить, что при соответствующем масштабном расположении дефлекторов 8 и 9 устройство производит отождествление пеленгов для данной системы двухпунктной(или, в частном случае, для многопунктной системы, когда пункты лежат на одной линии, при этом взаимном отождествлении двух наборов будет меняться масштабный множитель, равный расстоянию между пунктами) локации практически в бесконечном пространстве (коды номеров пар пеленгов первого b и второго а наборов в буферных регистрах 39 и 38), позволяет получить наклонные дальности до любой из j 0 1,п) целей от каждого из измерительных пунктов, определяет угол наклона плоскости fi (код z), в которой лежат линии положения пеленгов для одной цели (буферные регистры 42 блоков 35.1- 35.п) (фиг. 5), вычисляет углы отклонения каждого из лучей ( ац и «2j) в плоскости горизонта (эта плоскость перпендикулярна

плоскости матрицы 16) (фиг. 4) - коды х и у в буферных регистрах 40 и 41 блоков 35,1- 35.п. Так как в буферных регистрах 38 и 39 блоков 35.1-Зб.п записаны коды номеров пар пеленгов второго а и первого b наборов, то осуществляется, кроме того, упорядочение наборов пар пеленгов по признаку возрастания наклона плоскости (увеличение кода z в буферных регистрах 42 блоков 35.1-35.п), в которой лежат линии положе- ния пеленгов целей.

Для конкретного устройства измеряют постоянные величины (фиг. 2-5):

GMmln, 21тпах, «2тах, ДптДпах, Р т D.

Далее, для заданного расстояние До между измерительными пунктами, для которых проводится отождествление, рассчитывают

к До/0;

ЬОЛ ( «1max - «1min)/p; A02 (22max- «2тт)/р; ()6max-/ min)/m;

ci aimin/ Aai;

C2 Ct2min/A«2;

c3 /3min/43;

«U aimin + X ADi;

aij1 «ij/ Aai ci + x;

O2j. A22 C2 + y;

0J fl/43 C3 + z;

где j 1 ,n - номер цели.

По теореме синусов определим наклонные дальности до j-й цели от первого flij и от второго Д2 измерительных пунктов:45

Ди

С08(л/2 -/5j)sin(7T O2j) До

sin(jr-aij)-(-«2j)j flij k DsinySj sin«2j/sin(a2j- aij); Д2 k Dsin /3jSin «2j/sin( ai - aij).

Предлагаемое устройство отождествления осуществляет отождествление двух набо510

15

0

5

0

5

0

5

0

5

ров пеленгов; упорядочение отождествленных наборов по величине угла наклона плоскости, в которой лежат линии положения цели обоих наборов; присваивает угловые координаты цели: углы отклонения лучей, имитирующих линии положения пеленгов цели в плоскости, перпендикулярной плоскости матрицы, и угол наклона плоскости, в которой лежат линии положения цели; с помощью элементарных преобразований позволяет определить наклонные дальности от измерительных пунктов до цели; одновременно с отождествлением, преобразованием координат и упорядочением выходных данных позволяет получить признаки (коды а и Ь) соответствия между выходными и входными данными.

Формула изобретения

Устройство отождествления, содержащее два источника света, два модулятора, два дешифратора, блок фоточувствительных элементов, два коммутатора, генератор импульсов, первую и вторую группы по п регистров хранения значений пеленгов первого набора, первую и вторую группу по п регистров хранения значений пеленгов второго набора, три элемента задержки, четыре элемента ИЛИ, умножитель частоты, делитель частоты, формирователь импульсов, два триггера, дешифратор, три элемента И, три счетчика, аналого-цифровой преобразователь, первый и второй наборы по п элементов И, первый и второй наборы по п буферных регистров номера пар пеленгов, первый и второй наборы по п буферных регистров угла отклонения луча и набор из буферных регистров угла наклона плоскости, причем вход запуска устройства подключен к первому входу первого элемента ИЛИ, к входам сброса в нулевое состояние первого и второго триггеров и к первому входу второго элемента ИЛ И, выход первого элемента ИЛИ подключен к входу пуска генератора импульсов и входам установки в начальное состояние первого и второго коммутаторов, выход генератора импульсов подключен к первым входам первого и второго элементов И и через первый элемент задержки к входу умножителя частоты, выход которого подключен к входу делителя частоты, прямой выход первого триггера подключен к входу установки в единичное состояние второго триггера, второму входу второго элемента И, первым входам п элементов И первого набора,инверсный выход первого триггера подключен к второму входу первого элемента И, первым входам всех

элементов И второго набора, прямой выход второго триггера подключен к первому входу третьего элемента ИЛИ, инверсный выход второго триггера подключен к первому входу третьего элемента И, второй вход ко- торого подключен к выходу второго элемента задержки, выход третьего элемента И подключен к второму входу первого элемента ИЛИ, выходы первого и второго элементов И подключены к управляющим входам соответственно первого и второго коммутаторов и синхровходам соответственно первого и второго модуляторов, выходы индикации окончания проверки пеленгов первого и второго коммутаторов подключе- ны соответственно к второму и третьему входам третьего элемента ИЛИ, выход которого подключен к входу останова генератора импульсов, выходы К-х(К 1,п) регистров хранения значений пеленгов первой и вто- рой групп первого набора подключены к К-м информационным входам первого коммутатора, выходы К-х регистров хранения значений пеленгов первой и второй групп второго набора подключены к К-м информационным входам второго коммутатора, выходы первого и второго коммутаторов подключены к входам управления отклонением луча соответственно первого и второго дефлекторов, информационные входы которых соедине- ны с выходами первого и второго модуляторов соответственно, выходы первого и второго источников света соединены с информационными входами соответственно первого и второго модуляторов, выходы первого и второго дефлекторов связаны с соответствующими информационными входами блоков фотоэлементов, выход которого подключен к входу формирователя импульсов и входу ана- лого-цифрового преобразователя, выходы ко- торого подключены к информационным входам всех буферных регистров номера пар пеленгов первого и второго наборов, первый вход четвертого элемента ИЛИ подключен к входу изменения номера строки блока фотоэлементов и счетному входу первого счетчика, выход формирователя импульсов подключен к счетному входу второго счетчика и через элемент задержки ко всем вторым входам элементов И первого и второго наборов, выход второго элемента ИЛИ подключен к второму входу четвертого

элемента ИЛИ и входу установки первого счетчика, выход четвертого элемента ИЛИ подключен к входу установки третьего счетчика, счетный вход которого подключен к синхровходу блока фотоэлементов, выход второго счетчика подключен к входу дешифратора, выход третьего счетчика подключен к информационным входам всех буферных регистров угла отклонения луча первого и второго наборов, выход первого счетчика подключен к информационным входам п буферных регистров угла наклона плоскости, i-й выход дешифратора подключен к третьим входам соответствующих i-x (i 1,n) элементов И первого и второго наборов, выход каждого, i-ro элемента И первого набора подключен к синхровходам i-ro буферного регистра номера пар пеленгов и i-ro буферного регистра отклонения луча первого набора, выход каждого i-ro элемента И второго набора подключен к синхровходам i-ro буферного регистра номера пар пеленгов и i-ro буферного регистра отклонения луча второго набора и буферного регистра угла наклона плоскости, отличающееся тем, что, с целью повышения быстродействия, в него введены четвертый и пятый элементы И и четвертый элемент задержки, причем n-й выход дешифратора подключен к второму входу второго элемента ИЛИ, инверсным входам четвертого и пятого элементов И, входу установки в единицу первого триггера и к входу третьего элемента задержки, выход первого элемента ИЛИ подключен через четвертый элемент задержки к входу перехода на начало сканирования блока фотоэлементов и к установочному входу второго счетчика, выход умножителя частоты подключен к прямому входу четвертого элемента И, выход делителя частоты подключен к прямому входу пятого элемента И, выход четвертого элемента И подключен к синхровходу блока фотоэлементов, выход пятого элемента И подключен к входу изменения номера строки блока фотоэлементов, выходы буферных регистров номера пар пеленгов первого и второго наборов буферных регистров, угла отклонения луча первого и второго наборов буферных регистров, угла наклона плоскости являются соответственно первой-пятой группами информационных выходов устройства.

Фиг.1

Фиг. 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки информации | 1989 |

|

SU1631539A1 |

| Устройство обработки информации комплексной измерительной системы | 1990 |

|

SU1837283A1 |

| Устройство поиска степени оптимальности размещения в кластерных многопроцессорных системах при направленной передаче информации | 2022 |

|

RU2798392C1 |

| Устройство поиска степени оптимальности размещения в кластерных многопроцессорных системах | 2022 |

|

RU2791419C1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных гиперкубических циклических системах | 2019 |

|

RU2718166C1 |

| УСТРОЙСТВО ПОИСКА НИЖНЕЙ ОЦЕНКИ РАЗМЕЩЕНИЯ В ПОЛНОСВЯЗНЫХ МАТРИЧНЫХ СИСТЕМАХ ПРИ ОДНОНАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2010 |

|

RU2470357C2 |

| Устройство для распределения заданий процессорам | 1989 |

|

SU1837287A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| УСТРОЙСТВО ПОИСКА НИЖНЕЙ ОЦЕНКИ РАЗМЕЩЕНИЯ В МАТРИЧНЫХ СИСТЕМАХ ПРИ НАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2009 |

|

RU2452005C2 |

| УСТРОЙСТВО ПОИСКА НИЖНЕЙ ОЦЕНКИ РАЗМЕЩЕНИЯ В МАТРИЧНЫХ СИСТЕМАХ ПРИ ДВУНАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2009 |

|

RU2447485C2 |

Изобретение относится к вычислительной технике и радиолокации и предназначено для установления попарного соответствия (отождествления) между двумя наборами пеленгов (углов места и азимутов) и вычисления координат точки пересечения соответствующих линий положения. Цель изобретения - повышение быстродействия, В устройство введены два элемента И и элемент задержки. Устройство проводит отождествление двух наборов пеленгов за два цикла работы с учетом отождествленного количества пар пеленгов, что исключает дополнительные временные затраты на считывание с блока фоточувствительных элементов, оставшихся после считывания последнего записанного в этот блок сигнала. 8 ил. со

Фиг. 5

Фиг. 7

сч

э

S

| Теоретические основы радиолокации/Под ред Я.Д.Ширмана | |||

| - М.: Сов.радио, 1970 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мальцев А.А., Фромберг Э.М., Ямполь- ский B.C | |||

| Основы цифровой техники | |||

| - М.: Радио и связь, 1987, с | |||

| Сепаратор-центрофуга с периодическим выпуском продуктов | 1922 |

|

SU128A1 |

| - Массовая ради ори бл йоте ка | |||

| Вып | |||

| 1097 | |||

| Есепкина Н.А., Корольков Д.В., Парий- скии Ю.Н | |||

| Радиотелескопы и радиометры | |||

| - М.: Йаука, 1973 | |||

| Устройство для обработки информации | 1989 |

|

SU1631539A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-03-23—Публикация

1991-04-22—Подача