Изобретение относится к электротехнике и может быть использовано при построе- нии систем управления вентильных электроприводов.

Целью изобретения является повышение точности формирования фазовых сдвигов.

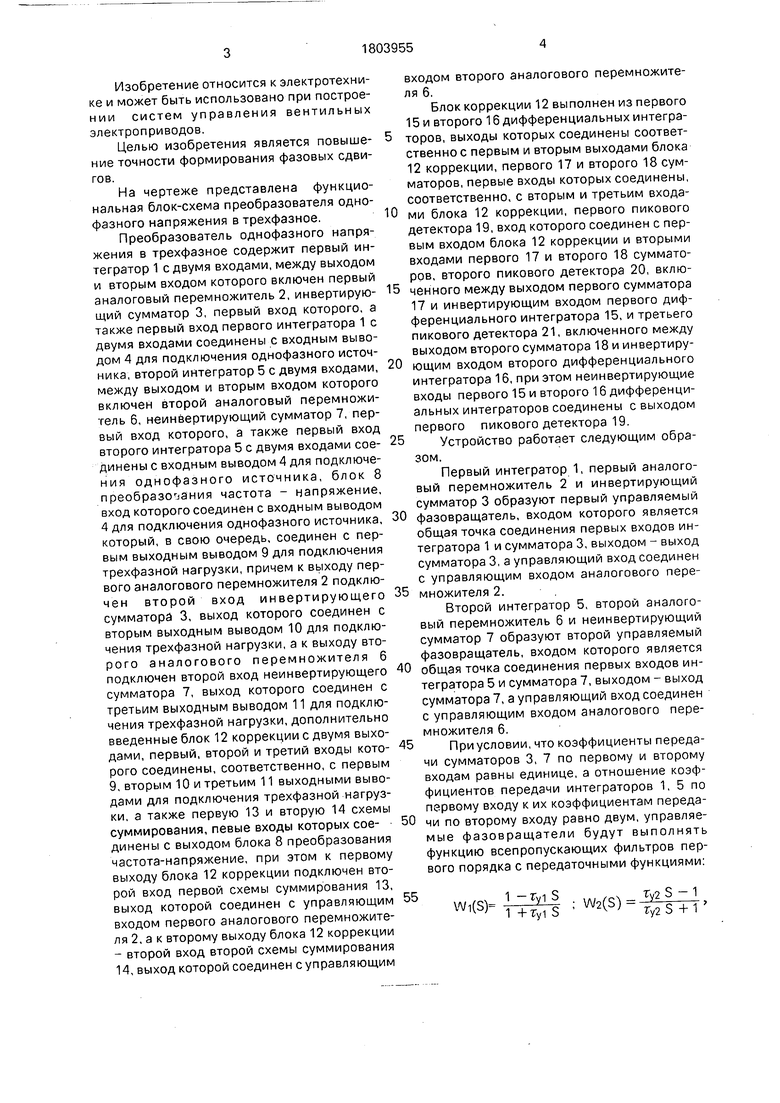

На чертеже представлена функциональная блок-схема преобразователя однофазного напряжения в трехфазное.

Преобразователь однофазного напряжения в трехфазное содержит первый интегратор 1 с двумя входами, между выходом и вторым входом которого включен первый аналоговый перемножитель 2, инвертирующий сумматор 3, первый вход которого, а также первый вход первого интегратора 1 с двумя входами соединены с входным выводом 4 для подключения однофазного источника, второй интегратор 5 с двумя входами, между выходом и вторым входом которого включен второй аналоговый перемножитель 6, неинвертирующий сумматор 7, первый вход которого, а также первый вход второго интегратора 5 с двумя входами соединены с входным выводом 4 для подключе- ния однофазного источника, блок 8 преобразования частота - напряжение, вход которого соединен с входным выводом 4 для подключения однофазного источника, который, в свою очередь, соединен с первым выходным выводом 9 для подключения трехфазной нагрузки, причем к выходу первого аналогового перемножителя 2 подключен второй вход инвертирующего сумматора 3, выход которого соединен с вторым выходным выводом 10 для подключения трехфазной нагрузки, а к выходу второго аналогового перемножителя 6 подключен второй вход неинвертирующего сумматора 7, выход которого соединен с третьим выходным выводом 11 для подключения трехфазной нагрузки, дополнительно введенные блок 12 коррекции с двумя выходами, первый, второй и третий входы которого соединены, соответственно, с первым 9, вторым 10 и третьим 11 выходными выводами для подключения трехфазной нагрузки, а также первую 13 и вторую 14 схемы суммирования, левые входы которых соединены с выходом блока 8 преобразования частота-напряжение, при этом к первому выходу блока 12 коррекции подключен второй вход первой схемы суммирования 13, выход которой соединен с управляющим входом первого аналогового перемножителя 2, а к второму выходу блока 12 коррекции - второй вход второй схемы суммирования 14, выход которой соединен с управляющим

входом второго аналогового перемножителя 6.

Блок коррекции 12 выполнен из первого 15 и второго 16 дифференциальных интеграторов, выходы которых соединены соответственно с первым и вторым выходами блока 12 коррекции, первого 17 и второго 18 сумматоров, первые входы которых соединены, соответственно, с вторым и третьим входами блока 12 коррекции, первого пикового детектора 19, вход которого соединен с первым входом блока 12 коррекции и вторыми входами первого 17 и второго 18 сумматоров, второго пикового детектора 20, вклюценного между выходом первого сумматора 17 и инвертирующим входом первого дифференциального интегратора 15, и третьего пикового детектора 21, включенного между выходом второго сумматора 18 и инвертирующим входом второго дифференциального интегратора 16, при этом неинвертирующие входы первого 15 и второго 16 дифференциальных интеграторов соединены с выходом первого пикового детектора 19.

Устройство работает следующим образом.

Первый интегратор 1, первый аналоговый перемножитель 2 и инвертирующий сумматор 3 образуют первый управляемый

фазовращатель, входом которого является общая точка соединения первых входов интегратора 1 и сумматора 3, выходом - выход сумматора 3, а управляющий вход соединен с управляющим входом аналогового перемножителя 2.

Второй интегратор 5, второй аналоговый перемножитель 6 и неинвертирующий сумматор 7 образуют второй управляемый фазовращатель, входом которого является

общая точка соединения первых входов интегратора 5 и сумматора 7, выходом - выход сумматора 7, а управляющий вход соединен с управляющим входом аналогового перемножителя 6.

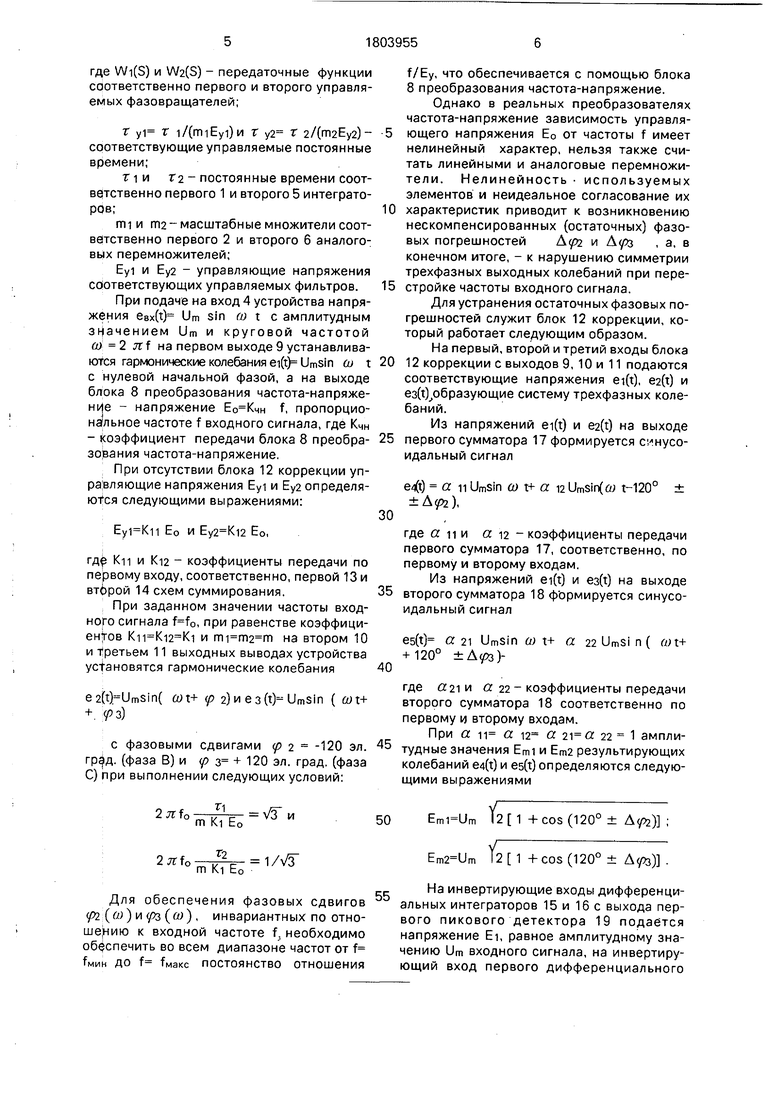

Приусловии, что коэффициенты передачи сумматоров 3, 7 по первому и второму входам равны единице, а отношение коэффициентов передачи интеграторов 1, 5 по первому входу к их коэффициентам передачи по второму входу равно двум, управляемые фазовращатели будут выполнять функцию всепропускающих фильтров первого порядка с передаточными функциями:

ш гсп 1 -lyiS Wl(S) 1+ryiS

W2(S)

ТУ2 S - 1 ГУ2 S + 1

где Wi(S) и W2(S) - передаточные функции соответственно первого и второго управляемых фазовращателей;

г У1 Г i/(miEyi)H г У2 г 2/(гп2ЕУ2)- соответствующие управляемые постоянные времени;

Пи г 2 - постоянные времени соответственно первого 1 и второго 5 интеграторов;

mi и ГП2- масштабные множители соответственно первого 2 и второго 6 аналоговых перемножителей;

ЕУ1 и ЕУ2 - управляющие напряжения соответствующих управляемых фильтров.

При подаче на вход 4 устройства напряжения e8x(t) Dm sin т t с амплитудным значением Um и круговой частотой ш 2 Jti на первом выходе 9 устанавливаются гармонические колебания ei(t) Umsin ш t с нулевой начальной фазой, а на выходе блока 8 преобразования частота-напряжение - напряжение f, пропорциональное частоте f входного сигнала, где КЧн - коэффициент передачи блока 8 преобразования частота-напряжение.

При отсутствии блока 12 коррекции управляющие напряжения ЕУ1 и ЕУ2 определяются следующими выражениями:

Ео и Ео,

гд0 Кц и Ki2 - коэффициенты передачи по первому входу, соответственно, первой 13 и втброй 14 схем суммирования.

При заданном значении частоты входного сигнала , при равенстве коэффициентов и на втором 10 и третьем 11 выходных выводах устройства установятся гармонические колебания

e2(t)Umsin( wi+ p 2) и e3(t)Umsin ( wt+

+ рз)

с фазовыми сдвигами р г -120 эл. грдд. (фаза В) и р з + 120 эл. град, (фаза С) при выполнении следующих условий:

f/Ey, что обеспечивается с помощью блока 8 преобразования частота-напряжение.

Однако в реальных преобразователях частота-напряжение зависимость управляющего напряжения Е0 от частоты f имеет нелинейный характер, нельзя также считать линейными и аналоговые перемножители. Нелинейность используемых элементов и неидеальное согласование их

характеристик приводит к возникновению нескомпенсированных (остаточных) фазовых погрешностей Д.р2 и Дузз , а, в конечном итоге, - к нарушению симметрии трехфазных выходных колебаний при перестройке частоты входного сигнала.

Для устранения остаточных фазовых погрешностей служит блок 12 коррекции, который работает следующим образом.

На первый, второй и третий входы блока

12 коррекции с выходов 9, 10 и 11 подаются соответствующие напряжения ei(t), e2(t) и ез(т.)/ бразующие систему трехфазных колебаний.

Из напряжений ei(t) и e2(t) на выходе

первого сумматора 17 формируется синусоидальный сигнал

30

) а и Umsin о t+ a 12 Umsin(tw t-120° ± ±Дрг),

где 2 11 и а 12 -коэффициенты передачи первого сумматора 17, соответственно, по первому и второму входам.

Из напряжений ei(t) и es(t) на выходе второго сумматора 18 формируется синусоидальный сигнал

40

es(t) a 21 UmSin CD t+

+ 120° )а 22 Umsi п( ftm

где «21 и а 22- коэффициенты передачи второго сумматора 18 соответственно по первому и второму входам.

При а ц а 12 а 22 1 ампли- тудные значения Emi и Ет2 результирующих колебаний e4(t) и es(t) определяются следующими выражениями

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь однофазного напряжения в трехфазное | 1991 |

|

SU1786616A1 |

| Преобразователь однофазного напряжения в трехфазное | 1991 |

|

SU1775820A1 |

| Преобразователь однофазного напряжения в трехфазное | 1989 |

|

SU1679586A1 |

| Преобразователь однофазного напряжения в трехфазное | 1990 |

|

SU1758799A1 |

| ФОРМИРОВАТЕЛЬ ТРЕХФАЗНЫХ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2014 |

|

RU2553418C1 |

| Преобразователь однофазного напряжения в трехфазное | 1988 |

|

SU1594665A1 |

| Устройство для преобразования однофазного напряжения в трехфазное | 1989 |

|

SU1653098A1 |

| Генератор ортогональных сигналов | 1990 |

|

SU1702514A1 |

| Преобразователь однофазного напряжения в трехфазное | 1989 |

|

SU1674332A1 |

| Преобразователь однофазного напряжения в трехфазное | 1991 |

|

SU1778891A1 |

Использование: при построении систем уНравления электроприводов. Сущность изобретения: устройство содержит интеграторы 1,5с двумя входами и одним выходом каждый, аналоговые перемножители 2, 6, инвертирующий 3 и неинвертирующий 7 сумматоры, первые входы которых, а также первые входы интеграторов 1, 5 соединены с фходным выводом 4, причем между выхо- до м и вторым входом каждого интегратора включены соответственно аналоговые перемножители 2, 6, к выходам которых подключены вторые входы сумматоров 3, 7 соответственно. Блок 8 преобразования частота-напряжение входом соединен с входным 4 и выходным 9 выводами и входом пикового детектора 19 блока коррекции 12. Выход блока 8 через схемы суммирования 13, 14 соединен с управляющими входами блоков 2, 6. Входы схем суммирования 13, 14 соединены с выходами дифференциальных усилителей 15, 16 блока коррекции 12, одни входы которых соединены с выходом детектора 19, а другие через пиковые детекторы 20, 21 и сумматоры 17, 18 - с выходными выводами 10, 11 и с выходами сумматоров 3, 7 соответственно. Другие входы сумматоров 17, Т8 соединены с выходным выводом 9. Устройство обеспечивает симметричную систему трехфазных колебаний в широком диапазоне входных частот. 1 з.п.ф-лы. 1 ил. СО С

2тгто

Г1

m Ki Ео

2 ж i0

Г2

m Ki Ео

1Л/3

Для обеспечения фазовых сдвигов (pi;(ftj) и рз (о) , инвариантных по отношению к входной частоте f, необходимо обеспечить во всем диапазоне частот от f

Тмин ДО f fMaKC ПОСТОЯНСТВО ОТНОШ6НИЯ

50Emi Um + cos (120° ± Дуз2) ; I2 1 + COS (120° ± Д) .

На инвертирующие входы дифференциальных интеграторов 15 и 16с выхода первого пикового детектора 19 подается напряжение EI, равное амплитудному значению Um входного сигнала, на инвертирующий вход первого дифференциального

интегратора 15 - напряжение с выхода второго пикового детектора 20, а на инвертирующий вход второго дифференциального интегратора 16 - напряжение Ез Ет2 с выхода третьего пикового детектора 21.

При отсутствии фазовых погрешностей А(р2 и напряжения рассогласования U 1-Еа и U 1-Ез, являющиеся входными напряжениями, соответственно, пер- вого 15 и второго 16 дифференциальных интеграторов, будут равны нулю, поэтому будут равны нулю и корректирующие напряжения EKI и Ек2, являющиеся выходными напряжениями дифференциальных интег- раторов 15 и 16. В этом случае при равенстве коэффициентов Кц схем суммирования 13 и 14 напряжения на их выходах, а, следовательно, управляющие напряжения ЕУ1 и ЕУ2 на входах соответст- вующих управляемых фильтров будут равны напряжению Е0.

При возникновении фазовых погрешностей или Ада амплитудные значения Emi и Ет2 результирующих колебаний e/t(t) и es(t) уже не будут равны амплитудному значению Dm.

Увеличение (уменьшение) фазового сдвига относительно номинального значения ро , равного 120 эл, град., приводит к уменьшению (увеличению) соответствующих амплитудных значений Ет и напряжений на инвертирующих входах дифференциальных интеграторов 15 и 16.

Усиленные напряжения рассогласова- ния, величина и полярность которых определяются величиной и знаком фазовых погрешностей, являются корректирующими напряжениями ЕЮ и Ек2На выходе первого управляемого фа- зовращателя формируется фазовый сдвиг (й)), определяемый следующим выражением:

п (e) -2arotg 2ttfm(Eo+E|(i)

а на выходе второго управляемого фа- зовращателя - фазовый сдвиг

.f

(P) - -2arotg 2 fm()

Наличие интеграторов 15 и 16 делает систему регулирования астатической, в которой при возникновении фазовых погрешностей корректирующие сигналы Ею и Ек2 будут изменяться до тех пор, пока статиче5

10 1520

25

30354045

50

55

ские ошибки (фазовые погрешности и Ада ) не станут равными нулю.

Технико-экономический эффект заключается в том, что введение блока коррекции позволяет устранить остаточные фазовые погрешности и сохранить симметричную систему трехфазных колебаний в широком диапазоне входных частот.

Формула изобретения

Авторы

Даты

1993-03-23—Публикация

1991-03-25—Подача