Изобретение относится к радиотехнике и может быть использовано для задержки высокочастотных сигналов, например, при измерении чувствительности высотомеров, РЛС или для настройки системы обработки эхо-сигналов.

Цель изобретения повышение точности задержки в условиях быстро меняющегося высокочастотного сигнала.

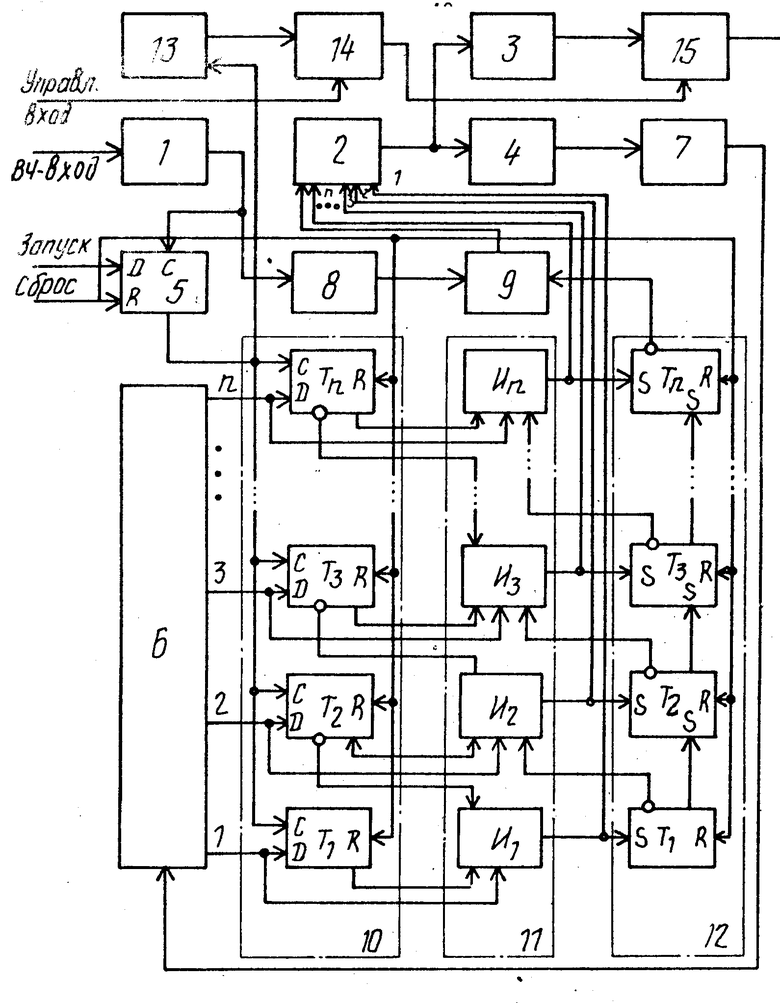

На чертеже приведена структурная схема устройства.

Устройство содержит формирователь 1, элемент ИЛИ 2, фильтр низких частот 3, линию задержки 4, триггер записи 5, линию задержки с отводами 6, усилитель-формирователь 7, элемент задержки 8, ключевой элемент 9, блок запоминания сигнала 10, блок выделения переднего фронта 11, блок выделения первой единицы 12, генератор импульсов 13, счетчик 14 и выходной ключ 15.

При этом последовательно соединенные элементы: линия задержки 4, усилитель-формирователь 7, линия задержки с отводами 6, блок выделения переднего фронта 11, элемент ИЛИ 2 представляет собой замкнутый контур, включение которого осуществляется посредством блока запоминания сигнала 10 и блока выделения первой единицы 12, выходы которых подключены к блоку выделения переднего фронта 11. Первоначальное занесение сигнала в контур происходит по цепи формирователь 1, элемент задержки 8, элемент 9. Задержка выполняется счетчиком 14, работающим от генераторов 13 и управляющим выходным ключом 15. Установка задержки осуществляется по управляющему входу устройства путем записи на счетчик 14.

Управление работой устройства осуществляется сигналами "Запуск" и "Сброс" через триггер записи 5, выход которого подключен к синхронизирующему входу блока запоминания сигнала 10 и разрешающему входу генератора импульсов 13.

Устройство работает следующим образом.

Входной ВЧ-сигнал приходит на формирователь 1, где из гармонического сигнала преобразуется в импульсный той же частоты. Далее поступает через элемент задержки 8 на ключевой элемент 9 и на синхронизирующий вход триггера записи 5. В исходном состоянии ключевой элемент 9 открыт для входного сигнала, который через элемент ИЛИ 2 поступает на фильтр низких частот 3, где восстановленный гармонический сигнал поступает на выход устройства через ключевой ключ 15, а также на выход линии задержки 4, далее на усилитель-формирователь 7, где восстанавливается амплитуда и форма сигнала искаженная в линии задержки 4, и с него на линию задержки с отводами 6. Все отводы последней подключены к информационным входам триггеров блока запоминания сигнала 10 и к входу схем совпадений блока выделения переднего фронта 11. При наличии сигнала "Запуск" на входе триггера записи 5 сигнал с формирователя 1 проходит через этот триггер и записывает состояние выходов линии задержки 6 в данный момент в триггерах блока запоминания сигнала 10.

Разрешением для прохождения сигнала с отвода линии задержки 6 является высокий уровень с прямого выхода соответствующего триггера и также высокий уровень с инверсного выхода последующего триггера блока запоминания сигнала 10, и разрешающий высокий уровень с инверсного триггера блока выделения первой единицы 12. Таким образом, через блок совпадения проходит импульс с отвода линии задержки 6, совпадающий с импульсным на выходе формирователя 1. Таких импульсов на отводах линии задержки 6 может оказаться более одного, для исключения этого прошедший импульс через блок совпадения блока выделения переднего фронта 11 через триггеры блока выделения первой единицы 12 запрещает прохождение последующих импульсов и в том числе закрывает ключевой элемент 9, через который проходил сигнал с выхода формирователя 1, т.е. на входе элемента ИЛИ 2 присутствует импульсный сигнал с выхода одной схемы совпадения. Таким образом, в замкнутой схеме циркулирует импульсная последовательность с частотой, определяемой частотой входного ВЧ-сигнала, и эта последовательность выдается на выход устройства, задержанная и сформированная выходным ключом 15. Сравнивая предложенное устройство задержки высокочастотных сигналов с прототипом получаем, что циркуляция импульсной последовательности в замкнутой системе осуществляется одинаковым образом, но время установки циркуляции, повторяющей входной сигнал в предлагаемой схеме, практически равно нулю, т.е. сюда не входит время отработки ошибки, подстройки схемы под частоту входного сигнала. И в общем случае оно в n раз меньше чем у прототипа, где n число отводов линии задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАДЕРЖКИ ВЫСОКОЧАСТОТНОГО СИГНАЛА | 1989 |

|

SU1734562A1 |

| Устройство для измерения частотного сдвига сигналов частотного телеграфирования | 1980 |

|

SU938188A1 |

| Формирователь радиоимпульсов | 1990 |

|

SU1748221A1 |

| Цифровой фазометр | 1987 |

|

SU1499264A1 |

| Формирующее устройство фазометра | 1984 |

|

SU1200195A1 |

| Устройство для измерения собственной частоты резонансной системы | 1987 |

|

SU1583875A1 |

| Устройство для контроля фазовыхиСКАжЕНий СигНАлА ВОСпРОизВЕдЕНия | 1979 |

|

SU853671A1 |

| Фазоимпульсный компаратор | 1986 |

|

SU1370761A1 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2093387C1 |

| Измеритель временных параметров случайных импульсных потоков | 1988 |

|

SU1575135A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение точности задержки в условиях быстро меняющегося задерживаемого ВЧ - сигнала. Устройство содержит циркуляционную схему усилителя - формирователя, линию задержки и линию задержки с отводами в цепи обратной связи, а также формирователь, фильтр низкой частоты, триггер записи, генератор импульсов, счетчик и выходной ключ. Дополнительно введены блок запоминания сигнала, блок выделения переходного фронта, блок выделения крайней единицы, элемент задержки, ключевой элемент и элемент ИЛИ. Совокупность элементов и их взаимное соединение обеспечивают повышение быстродействия обработки ошибки установки частоты за счет практически мгновенного определения положения совпадения входного и задержанного сигналов в отличие от прототипа, в котором данная операция осуществляется путем последовательного приближения, тем самым повышается точность установки задержки в условиях меняющегося входного ВЧ - сигнала. 1 ил.

УСТРОЙСТВО ЗАДЕРЖКИ ВЫСОКОЧАСТОТНОГО СИГНАЛА, содержащее усилитель-формирователь, соединенный входом с выходом линии задержки, а выходом с входом линии задержки с отводами, вход линии задержки соединен с входом фильтра низких частот, выход которого соединен через выходной ключ с высокочастотным выходом устройства, формирователь, соединенный входом с высокочастотным входом устройства, а выходом с синхронизирующим входом триггера записи, информационный вход которого соединен с входом устройства "Запуск", а установочный вход - с входом устройства "Сброс", генератор импульсов, соединенный выходом с счетным входом счетчика, а разрешающим входом - с выходом триггера записи, выход счетчика соединен с управляющим входом выходного ключа, а установочный вход счетчика - с управляющим входом устройства, отличающееся тем, что, с целью повышения точности задержки в условиях быстро меняющегося задерживающего ВЧ-сигнала, в него введены блок запоминания сигнала, блок выделения переднего фронта, блок выделения первой единицы, элемент задержки, ключевой элемент и элементы ИЛИ, при этом блок запоминания сигнала состоит из n триггеров, информационные входы которых соединены с n выходами линии задержки с соответствующими отводами и первым входом соответствующего элемента И, входящих в блок выделения переднего фронта, а синхронизирующие входы этих триггеров соединены с выходом триггера записи, прямой выход i-го триггера блока запоминания сигнала соединен с вторым входом i-го элемента И блока выделения переднего фронта, а инверсный выход - с третьим входом (i - 1)-го элемента И, четвертый вход i-го элемента И соединен с инверсным выходом Тi - 1 триггера блока выделения первой единицы, состоящего из n триггеров, первый установочный вход которых соединен с выходом соответствующего элемента И блока выделения переднего фронта и соответствующим входом элемента ИЛИ, второй установочный вход триггеров блока выделения первой единицы соединен с прямым выходом предыдущего триггера этого блока, инверсный выход n-го триггера блока выделения первой единицы соединен с первым входом ключевого элемента, второй вход которого соединен с выходом элемента задержки, соединенного входом формирователя, выход ключевого элемента соединен с входом элемента ИЛИ, выход которого соединен с входом линии задержки, входы сброса n триггеров блока выделения первой единицы и n триггеров блока запоминания сигнала соединены с третьим входом устройства.

| УСТРОЙСТВО ЗАДЕРЖКИ ВЫСОКОЧАСТОТНОГО СИГНАЛА | 1989 |

|

SU1734562A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1996-02-10—Публикация

1990-01-22—Подача