назначены для обеспечения разрыва информационных связей между машинами при отказе одной из них.

Элемент ИЛИ-НЕ 13 предназначен для формирования сигнала об отказе устройст- ва в целом в случае, когда во второй ВМ был обнаружен отказ до того, как был устранен отказ в первой. Напряжение питания на первый 7 (второй 8) элементы И подается с ВИПа 18(21) первого 3 ( второго 4) БКП. Питание же на третий 9 и четвертый 10 элементы И, триггеры 5,6. коммутатор 12 и элемент ИЛИ-НЕ 13 подается с выходов ВИПов 18 первого 1 и ВИПА 21 второго 2 БКП, таким образом, что оно будет в норме, если хотя бы один из этих ВИПов в норме.

Устройство работает следующим образом.

В исходном состоянии обе ВМ исправны (на контрольных выходах-единицы), оба триггера 5, 6 находятся в единичном состоянии, оба информационных входа коммутатора 12 открыты, на выходе 17 отказа устройства - нуль. В обе ВМ загружены одни и те же программы, на входы поступают одни и те же данные, ВМ работают в синхронном режиме, поддерживая этот режим обменом соответствующих сигналов по ши- не (входугвыходу) управления и данных обь- единяющих две одинаковыке ВМ в дублированную структуру. Данные, синхронно появляющиеся на выходах данных обоих ВМ через коммутатор 1. поступают на выход 16 данные устройства.

В случае обнаружения неисправности схемой самоконтроля 1.1.1(2.1.1) на контрольном выходе первой (второй) ВМ появляется нулевой потенциал. Этот нуль поступает на выход элемента И 7, далее по входу элемент И 9, а с его выхода - на инверсный R-вход триггера 5, обнуляется последний.

Нулевой потенциал, появившийся на выходе триггера 5, блокирует первой (второй) вход коммутатора 12, исключая тем самым попадание данных с выхода отказавшей ВМ на выход 16 данных устрой- ства. Кроме того, нуль с выхода И 9 (И 10) поступает на вход ЛУ второй 2 (первой 1) оставшейся исправной ВМ. предупреждая последнюю о том, что она работает без дублирования. ф

Кроме того, этот нуль с выхода элемента И 9 или И 10, поступая на один из входов элемента И .11, приведет к появлению на выходе последнего нуля. Этот нуль, поступая на управляющие входы первого 14 и

15

5

1

0

5 0 5

®

g 5

5

второго 15 блоков магистральных элементов, приведет их в высокоимпеданское состояние, обеспечив тем самым разрыв ранее соединенных входов-выходов управления и данных.

Т.о.. отказавшая ВМ не может оказать никакого влияния на исправную.

При поступлении нуля на оход ЛУ ВМ может быть предусмотрен переход программный либо аппаратно-масштабный (например про прерыванию), к подпрограмме диагностирования отказавшей ВМ.

После восстановления отказавшей ВМ (механизм восстановления может быть любым) на контрольном выходе вновь появляется единица. Однако, соответствующий информационный вход коммутатора 12 по- прежнему блокирован, так как ВМ еще не введена в синхронный режим с исправной и продолжавшей работу ВМ.

После того, как на входе ЛУ исправной ВМ вновь появился единичный сигнал о исправности другой ВМ, данная ВМ, являющаяся теперь ведущей, переходит к подпрограмме восстановления синхронной работы и по шине управления и данных делает все необходимые операции (загрузка ОЗУ другой ВМ и т.п.) для восстановления синхронной работы обоих ВМ. После того, как эта процедура закончилась, на одном из разрядов выхода данных ведущей (второй 2) ВМ появляется единичный импульс, который переводит первый 5 триггер в единичное состояние, деблокируя первый вход коммутатора 12. Обе ВМ вновь начинают работу в синхронном режиме.

Реализация входа ЛУ может быть выполнена программно-аппаратными средствами, например, как периодический опрос в процессе отработки основной программы двойного счетчика. Начинается такой периодический опрос только после выхода из режима синхронной работы, о чем ВМ всегда узнает по шине управления и данных.

Особенностью такой структуры является то, что ВМ запитывается от двух различных первичных источников питания, что значительно снижает вероятность одновременного изменения напряжения на обоих ВМ, ведущих к неверному функционированию ВМ. Однако, только такой меры недостаточно. Понижение напряжения ниже определенного уровня может привести к возникновению таких сигналов на шине управления и данных, что приведет к ошибочной (ложной) работе равносильной отказу и другой ВМ, напряжение питания которой в норме. Чтобы избежать таких случаев, з устройство введен постоянный контроль с помощью компараторов напряжений на выходах всех ВИПов ВМ. В случае выхода напряжения за допустимый предел, который выбирается таким образом и на таком уровне, когда ВМ еще работает устойчиво, на выходе соответствующего компаратора появляется нуль, который приводит к событиям, аналогичным описанным выше.

Кроме того, этот сигнал поступает на управляющий вход ВИПа, который задает заниженное напряжение, и отключает его, а следовательно и те блоки ВМ, которые он питает. ВМ переходит в режим устойчивого отказа, на шине управления и данных не могут появиться ложные сигналы, кроме того последняя разорвана, исправная. ВМ однозначно определяет соседа как отказавшего и продолжает работать, периодически опрашивая вход ЛУ, ожидая устранения неисправности в соседней ВМ.

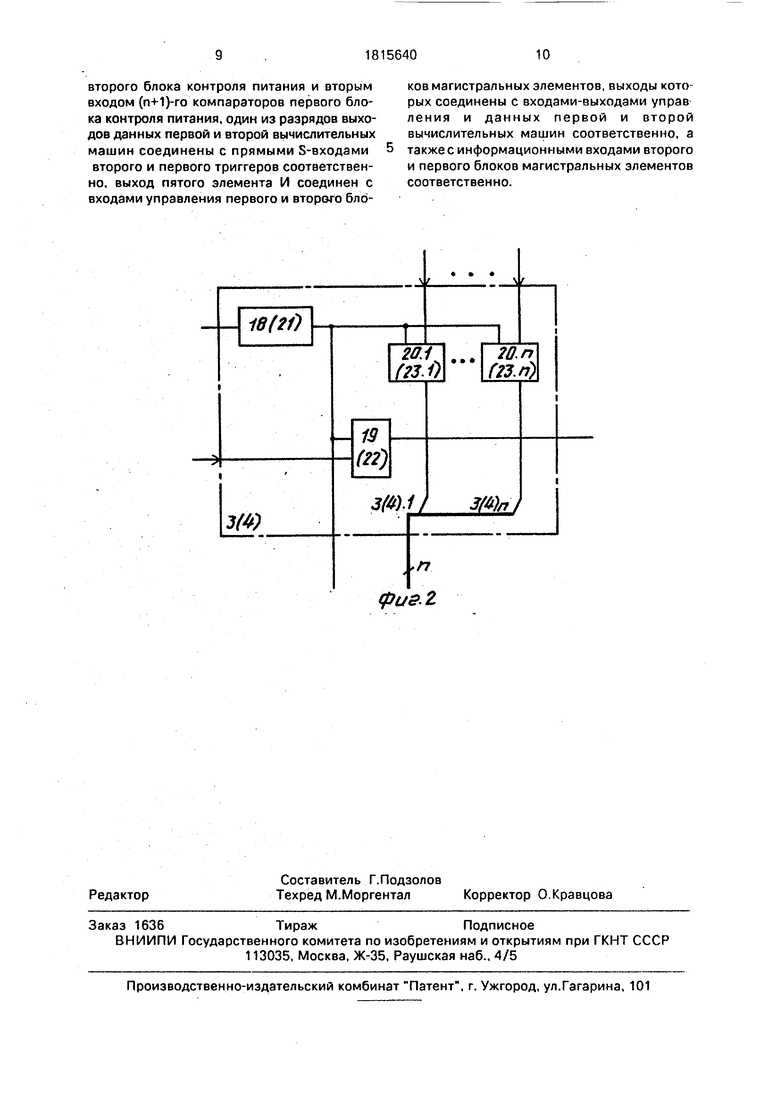

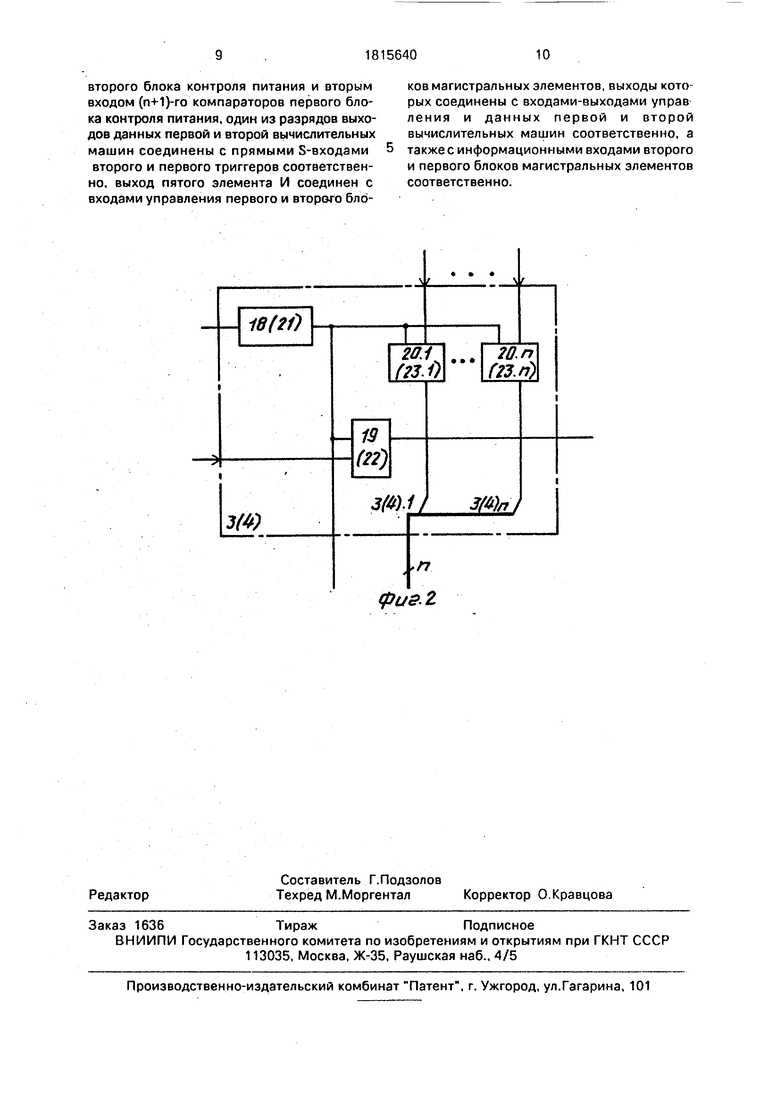

Особенностью устройства является и то, что выходы ВИПов самых БКП взаимно контролируются. Это сделано с учетом того, что при выходе за допустимые пределы напряжения выходе этого ВИПа, контроль за ВИПами ВМ не может быть достоверным. Поэтому (гН-1)-е компараторы обоих БКП контролируют питание на выходе ВИПов друг друга. Если произошло падение напряжения на этом ВИПе. то с выхода компаратора 19(22) нуль поступает на вход управления ВИПом 21(18), полностью обесточивая выход последнего.

Кроме того, этот нуль поступает на вход элемента И 10(И 9), говоря о неисправности второй 2 (первой 1) ВМ и блокируя соответствующий вход коммутатора 12, обнуляя триггер 5. Восстановление устройства из этого состояния аналогично вышеописанному;

Т.о., понижение напряжения на выходе хотя бы одного ВИПа ВМ либо на выходе одного из первичных источников питания не может привести к отказу структуры в целом в результате взаимного влияния ВМ, так как разрыв шины управления и данных исключает информационную связь между ВМ.

Ф о р м у л а и з о б р е т е н и я

Устройство для контроля дублированной вычислительной системы, содержащее первую и вторую вычислительные машины с п вторичными источниками питания каждая, коммутатор, элемент ИЛИ--НЕ, причем выходы данных первой и второй вычислительных машин соединены с первым и вторым

0

5

0

5

0

5

0

5

0

5

информационными входами коммутатора, выход которого является выходом данных устройства, выход элемента ИЛИ-НЕ является выходом отказа устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит пер- вый пятый элементы И, первый и второй триггеры, первый и второй блоки контроля питания, каждый из которых содержит вторичный источник питания и с первого по (п+1)-й компараторы, а устройство также содержит первый и второй блоки магистральных элементов, контрольные выходы первой и второй вычислительных машин соединены с первыми входами первого и второго элементов И соответственно, выходы которых соединены с первыми входами соответственно третьего и четвертого элементов И. связанных выходами с входами логических условий соответственно первой и второй вычислительных машин, с соответствующими входами пятого элемента И и инверсными R-входами соответственно первого и второго триггеров, выходы которых соединены с одноименными управляющими входами коммутатора и с соответствующими входами элемента ИЛИ-НЕ, выходы п вторичных источников питаний- первой вычислительной машины соединены с первыми входами одноименных компараторов первого блока контроля питания, выходы которых соединены соответственно с второго по (п+1)-й входами первого элемента И и с входами управления одноименных вторичных источников питания первой вычислительной машины, выходы п вторичных источников питания второй вычислительной машины соединены с первыми входами одноименных компараторов второго блока контроля питания, выходы которых соединены соответственно с второго по (п+1)-й входами второго элемента И и с входами управления одноименных вторичных источников питания второй вычислительной машины, выход вторичного источника питания первого блока контроля питания соединен с вторыми входами п компараторов данного блока и первыми входами (п+1)-х компараторов первого и второго блоков контроля питания/выходы которых соединены с вторыми входами соответственно четвертого и третьего элементов И и с входами управления вторичных источников питания соответственно второго и первого блоков контроля питания, выход вторичного источника питания второго блока контроля питания соединен с вторыми входами с первого по (п+1)-й компараторов

второго блока контроля питания и вторым входом (п+1)-го компараторов первого блока контроля питания, один из разрядов выходов данных первой и второй вычислительных машин соединены с прямыми S-входами второго и первого триггеров соответственно, выход пятого элемента И соединен с входами управления первого и второго блоков магистральных элементов, выходы которых соединены с входами-выходами управ ления и данных первой и второй вычислительных машин соответственно, а также с информационными входами второго и первого блоков магистральных элементов соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Устройство для сопряжения электронных вычислительных машин | 1982 |

|

SU1061129A1 |

| Блок обработки информации | 2017 |

|

RU2665225C1 |

| Устройство для сопряжения | 1980 |

|

SU903851A1 |

| СИСТЕМА ЭЛЕКТРОПИТАНИЯ КОМПЛЕКСА КОРАБЕЛЬНОЙ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ | 1998 |

|

RU2124260C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| СИСТЕМА ЭЛЕКТРОПИТАНИЯ КОМАНДНО-СТРЕЛЬБОВОЙ ИНФОРМАЦИОННО-УПРАВЛЯЮЩЕЙ СТИСТЕМЫ | 2001 |

|

RU2206167C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| СИСТЕМА ЭЛЕКТРОПИТАНИЯ КОРАБЕЛЬНОГО ИНФОРМАЦИОННО-УПРАВЛЯЮЩЕГО КОМПЛЕКСА | 2004 |

|

RU2267849C1 |

| Устройство для реконфигурации резервируемых блоков | 1990 |

|

SU1748155A1 |

М)

з(М I Я)/

Фи&г

Авторы

Даты

1993-05-15—Публикация

1990-11-26—Подача