Изобретение относится к цифровой вычислительной технике и автоматике и может быть использовано при построении высоконадежных устройств на основе однотипных резервируемых блоков.

Известно устройство для контроля вычислительных машин, содержащее два резервируемых блока (машины), элемент сравнения, триггер, коммутатор, элементы И, ИЛИ.

Недостатком указанного устройства является низкая надежность, обусловленная наличием лишь двух резервируемых блоков и, как следствие, невозможность обеспечения работоспособности при двух отказах.

Наиболее близким к изобретению является устройство, содержащее первый-четвертый резервируемые блоки, первый и второй элементы сравнения, коммутатор, причем выход первого резервируемого блока соединен с первым входом первого элемента сравнения, выход которого соединен с первым управляющим входом коммутато- рй, выход которого является выходом данных устройства, выход второго резервируемого блока соединен с первым входом второго элемента сравнения, выход которого соединен с вторым управляющим входом коммутатора, выход третьего резервируемого блока соединен с вторым входом первого элемента сравнения и первым информационным входом коммутатора, выход четвертого резервируемого блока соединен с вторым входом второго элемента сравнения и вторым информационным входом коммутатора.

Недостатком указанного устройства является низкая надежность. Этот недостаток обусловлен тем, что неисправность двух резервируемых блоков, выходы которых контXI

00

жА

СП |СЛ

ролируются различными схемами сравнения, приводит к отказу устройства в целом, так как отсутствует возможность поиска и выбора другой- двухканальной работоспособной конфигурации, составленной из оставшихся исправных резервируемых блоков.

Другим недостатком указанного устройства является низкая достоверность выдаваемой информации (низкая достоверность контроля) Так, если один из блоков, контролируемых одной схемой сравнения отказал, то на выходе схемы сравнения появится нуль, который блокирует соответствующий вход коммутатора Од- нако, если в процессе дальнейшего функционирования откажет и второй резервированный блок, выход которого соединен с другим Входом того же элемента сравнения, и информация на выходах этих блоков совпадает (либо будет совпадать периодически), то в коммутаторе произойдет смешивание рабочей и ложной информации, что приведет к выдаче на выход устройства неверной выходной последовательности

Целью изобретения является повышение надежности функционирования устройства

Сущность изобретения состоит в повышении надежности функционирования устройства путем обеспечения сохранения работоспособной конфигурации резервируемых блоков при любых двух отказавших до возникновения отказа в третьем из четырех блоков, обеспечения сохранения работоспособности устройства при одновременном отказе любых двух резервируемых блоков в случае несовпадения данных на их выходах, блокирования выходов элементов сравнения, осуществляющих контроль резервируемых блоков, которые признаны отказавшими.

Изобретение реализуется путем введения следующих элементов и связей.

Введение регистра данных и обусловленных им связей необходимо для исключения попадания на выход данных устройства ложной информации, которая появляется на выходе коммутатора с момента отказа одного из резервируемых блоков до момента блокирования соответствующего информационного входа коммутатора,

Введение третьего-шестого элементов сравнения и обусловленных ими связей необходимо для обеспечения попарного контроля выходов резервируемых блоков.

Ведение первого-четвертого счетчиков сбоев, первого-шестого элементов ИЛИ и обусловленных ими связей необходимо для обеспечения блокирования выходов соответствующих элементов сравнения при отказе резервируемых блоков.

Введение первого-четвертого элементов И и обусловленных ими связей необходимо для определения отказавшего резервируемого блока и блокирования при этом соответствующего информационного входа коммутатора.

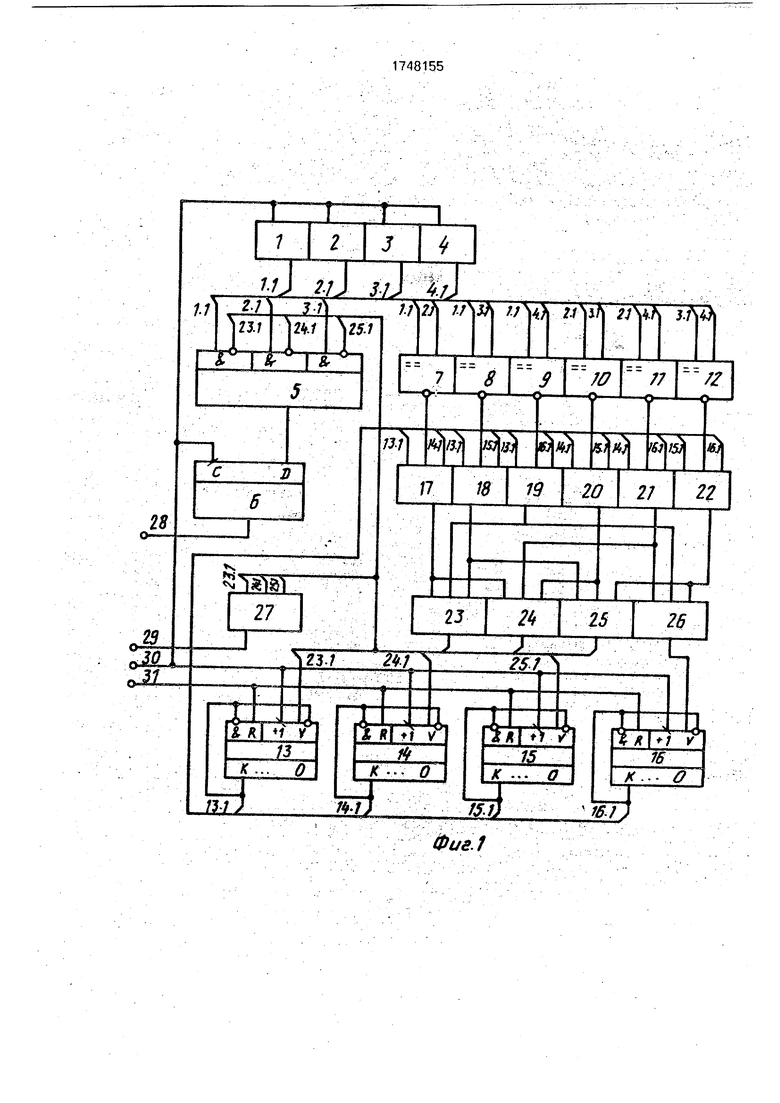

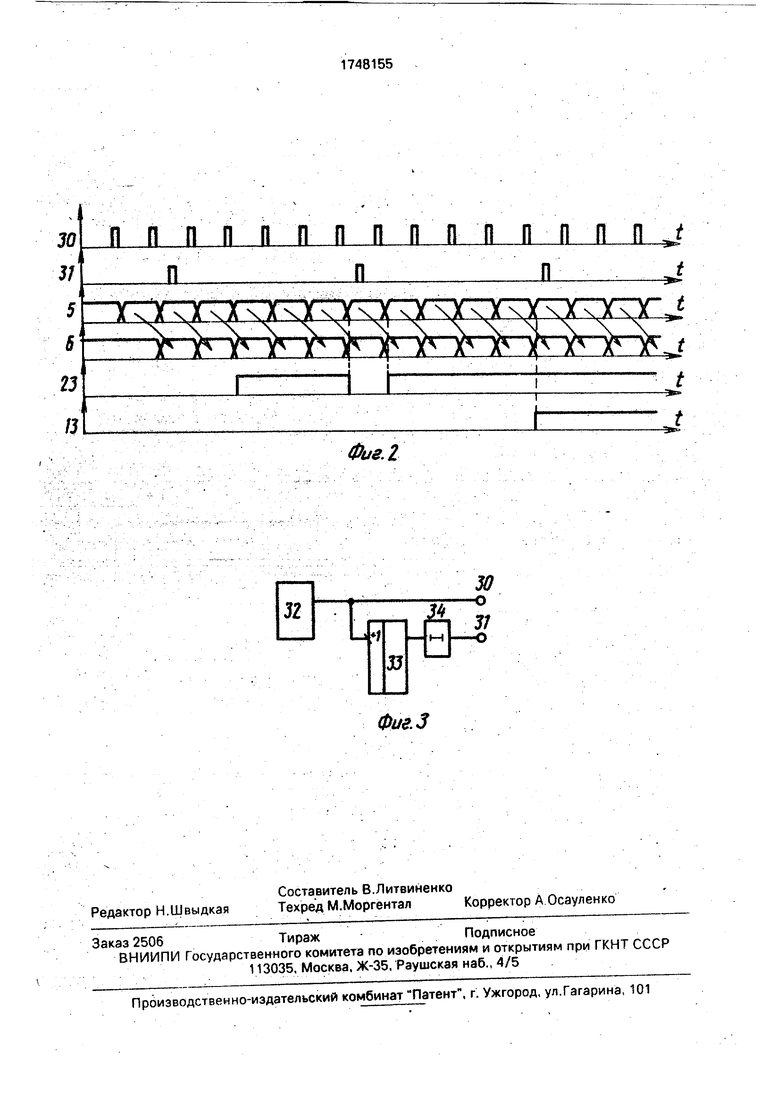

На фиг. 1 представлена функциональная схема устройства для реконфигурации резервируемых блоков; на фиг. 2 - временная диаграмма работы устройства; на фиг. 3 - вариант реализации блока синхронизации устройства.

На фиг. 1 использованы следующие обозначения; 1-4 - первый-четвертый резервируемые блоки, 5 - коммутатор данных, 6 - регистр данных 7-12 - первый-шестой элементы сравнения 13-16 - первый-четвертый счетчики сбоев, 17-22 - первый-шестой элементы ИЛИ, 23-27 - первый-пятый элементы И, 28 - выход данных устройства, 29 - выход отказа устройства, 30, 31 - первый и второй входы синхронизации устройства.

Первый 1 - четвертый 4 резервируемые блоки предназначены для синхронной выдачи требуемых данных по тактовым импульсам, поступающих с первого входа 30

синхронизации устройства В случае исправности блоков данные на их выходах идентичны

Коммутатор данных 5 предназначен для коммутации на D-вход регистра б выходов

первого 1 - третьего 3 резервируемых блоков в случае исправности последних и блокирования соответствующего входа в случае отказа этих блоков

Регистр данных 6 предназначен для

временного хранения выдаваемых устройством данных.

Первый 7 - шестой 12 элементы сравнения предназначены для попарного сравнения данных на выходах соответствующих

резервируемых блоков, а именно: первый 7 -для сравнения выходов первого 1 и второго 2 резервируемых блоков, второй 8 - первого 1 и третьего 3, третий 9 - первого 1 и четвертого 4, четвертый 10 - второго 2 и

третьего 3, пятый 11 - второго 2 и четвертого 4, шестой 12 - третьего 3 и четвертого 4,

Первый 13 -четвертый 16 счетчики сбоев предназначены для фиксации факта отказа первого t - четвертого 4 резервируемых

5 блоков соответственно

Первый 17 - шестой 22 элементы ИЛИ предназначены для блокирования выходов первого 7 - шестого 12 элементов сравнения соответственно

Первый 23 - четвертый 26 элементы И предназначены для определения состояния исправности (неисправности) первого 1 - четвертого 4 резервируемых блоков соответственно.

Первый 17 - шестой 22 элементы ИЛИ и первый 23 - четвертый 26 элементы И образуют коммутатор сигналов отказа с соответствующими связями.

Пятый элемент И 27 предназначен для определения состояния, при котором три и более резервируемых блока признаны отказавшими, т.е. этот элемент выдает сигнал о том, что далее устройство выдавать достоверные данные не может, на выходе регист- ра 6 при этом должны быть одни нули.

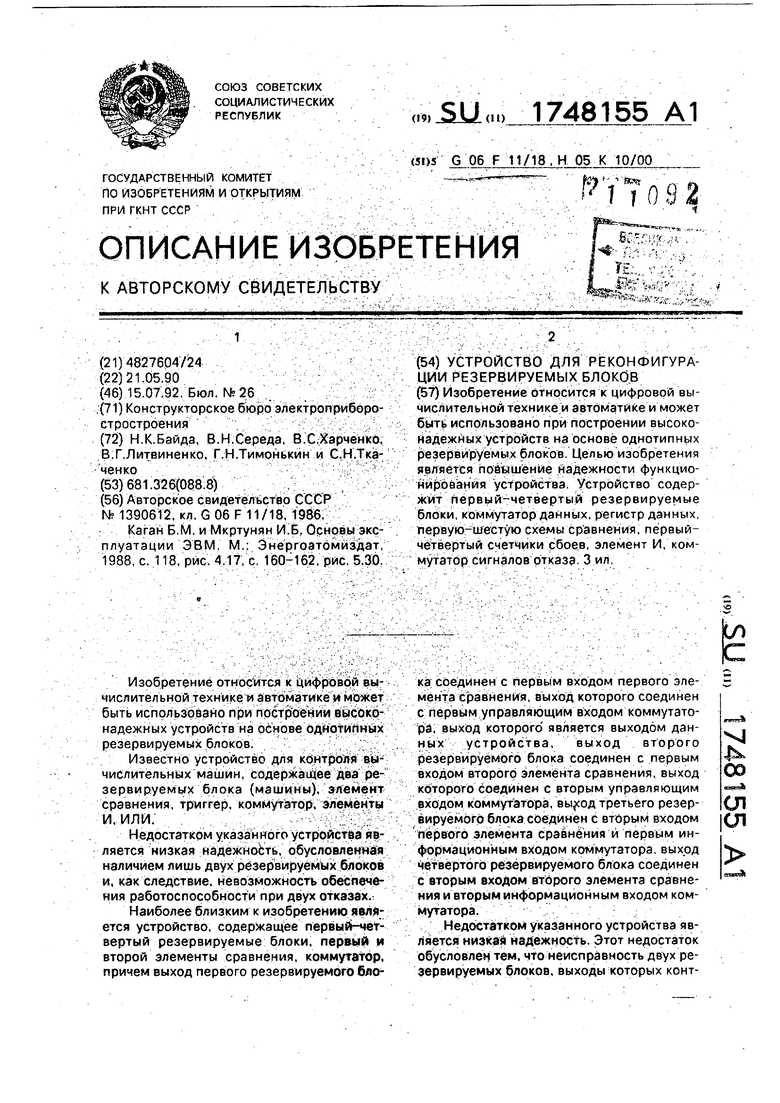

На фиг. 3 использованы следующие обозначения: 32 - генератор тактовых импульсов, 33 - счетчик с коэффициентом пересчета Н, 34 - элемент задержки, остальные обозначения соответствуют обозначениям фиг. 1.

Блок синхронизации, пример реализации которого изображен на фиг. 3, должен формировать две импульсные последова- тельности(фиг. 2), подаваемые на первый 30 и второй 31 входы синхронизации устройства.

Устройство работает следующим образом.

В исходном состоянии все резервируемые блоки исправны, и, допустим, на их выходах находятся одни нули, все счетчики сбоев 13-16 находятся в нулевом состоянии, в регистре данных 6 также записаны одни нули. Так как данные на выходах всех блоков 1-4 совпадают, то на выходах всех шести 7-12 элементов сравнения будут нули, следовательно, на все входы всех элементов ИЛИ поступают одни нули, на выходах первого 23 - четвертого 26 элементов И также будут нули. Все входы коммутатора данных 5 открыты. Данные (нули) с выходов первого 1 - третьего 3 блоков, пройдя поразрядное логическое сложение, которое не может их исказить, так как все они одинаковы, поступают на информационный вход регистра 6, в который будут за- писаны по заднему фронту первого тактового импульса, поступившего с перво- го 30 входа синхронизации устройства. Но так как в регистре данных б были записаны одни нули, изменение его состояния не про- исходит(фиг, 2), По заднему фронту этого не тактового импульса резервируемые блоки 1-4 выдадут данные, отличные от нулевых, и если все они продолжают находиться в исправном состоянии, то изменений не произойдет, и эти данные по заднему фронту очередного тактового импульса, поступившего с первого входа 30 синхронизации устройства, запишутся в регистр данных 6 (фиг 2). Далее устройство работает аналогично до тех пор, пока в одном из блоков не произошел отказ. Допустим, отказал первый блок 1. Тогда данные на его выходе будут отличны от данных на выходах всех остальных резервируемых блоков 2-4. Следовательно, на инверсных выходах первого 7, второго 8 и третьего 9 элементов сравнения появятся единицы, которые, пройдя через первый 17 - третий 19 элементы ИЛИ, поступят на соответствующие входы элементов И 23-26 (фиг. 1), Однако единицы на всех трех входах появятся только у первого элемента И 23, что приведет к появлению единицы на выходе только этого элемента И. Эта единица, поступив на первый инверсный управляющий вход коммутатора данных 5, блокирует соответствующий информационный вход, к которому подключен выход первого резервируемого блока 1, исключая сложение ложных данных первого блока 1 с данными двух других исправных блоков 2 и 3. Кроме того, эта единица поступает на прямой V-вход первого счетчика сбоев, разрешая работу последнего. Поочередному тактовому импульсу, поступающему со входа 30 синхронизация устройства на вход +1 счетчика сбоев, последний перейдет в очеденое состояние.

В таком состоянии устройство будет находиться до тех пор, пока на вход +Г счетчика сбоев не поступит 2К импульсов до прихода очередного импульса со второго 31 входа синхронизации, либо пока не восстановится отказавший блок (т.е., в нем произошел сбой), при этом единица на выходе элемента И 23 исчезнет.

Именно для того, чтобы устранить влияние сбоев, возникающих в резервируемых блоках на принятие решения о том, отказал данный блок или нет, и проводится периодическое обнуление счетчиков сбоев с частотой в Н раз меньшей, чем частота (fi) тактовых импульсов, поступающих с первого входа 30 синхронизации устройства (фиг. 2). Считаем, что отказавшим признается тот блок, данные на выходе которого за период следования импульсов () со второго входа 31 синхронизации устройства не совпали не менее чем в 2К тактах работы устройства. Причем П2 H/f 1.

Тогда за время Пг счетчик сбоев соответствующего резервируемого блока (допу- стим, первого, фиг, 2) успеет перейти в состояние 2К, при котором на выходе его к-того разряда появится единица. Эта единица, поступая на инверсные R и V-аходы этого же счетчика сбоев, исключает возможность дальнейшего изменения его состояния. Кроме того, она поступает на входы соответствующих элементов ИЛИ, блокируя влияние соответствующих элементов сравнения. Так, если отказавшим признан первый блок 1, то единица с выхода счетчика сбоев 13 поступает на входы первого 17 - третьего 19 элементов ИЛИ, как бы подтверждая отказ данного блока. При отказе второго блока 2 единица поступает с выхода счетчика сбоев 14 на входы первого 17, четвертого и пятого 21 элементов ИЛИ. При отказе третьего 3 - на входы второго 18, четвертого 20 и шестого 22, а при отказе четвертого А - на входы третьего 19, пятого 21 и шестого 22 элементов ИЛИ.

Предлагаемое устройство в отличие от прототипа дает возможность парировать одновременно возникшие отказы в любых двух блоках при условии, что данные на выходах отказавших блоков не совпадают. Допустим, отказали первый 1 и четвертый 4 резервируемые блоки, тогда на выходах всех элементов сравнения кроме 10(появят- ся единицы, что приведет к появлению единиц на выходах первого 23 и четвертого 26 элементов И. Следовательно, второй и третий выходы коммутатора данных 5 будут открыты, и на выход его будут поступать данные с исправных блоков,

Отказ любых трех резервируемых блоков приводит к появлению единиц на выходах всех элементов ИЛИ, а значит, и выходах первого 23 - четвертого 26 элементов И. Это приведет к блокированию всех входов коммутатора данных 6, после чего на выход 28 данных устройства будут выдаваться одни нули, а также к появлению единицы на выходе пятого элемента И 27, которая, поступая на выход 29 отказа устройства, свидетельствует о наличии трех отказавших блоков.

Формула изобретения

Устройство для реконфигурации резервируемых блоков, содержащее первый-чет- вертый резервируемые блоки, первую и вторую схемы сравнения, коммутатор данных и элемент И, первый вход синхронизации устройства соединен с синхровходами

первого-четвертого резервируемых блоков, выходы первого-третьего резервируемых блоков подключены к соответствующим информационным входам коммутатора данных, выход первого резервируемого блока соединен с первым входом первой схемы сравнения, второй вход которой подключен к выходу второго резервируемого блока, отличающееся тем, что, с целью повышения

надежности функционирования устройства, в него введены третья-шестая схемы сравнения, коммутатор сигналов отказа, регистр данных, первый-четвертый счетчики сбоев, выход коммутатора данных соединен с информационным входом регистра данных, вход управления записью которого подключен к первому входу синхронизации устройства, а выход регистра данных является информационным выходом устройства, выход первого резервируемого блока соединен с первыми входами второй и третьей схем сравнения, вторые входы которых подключены соответственно к выходам третьего и четвертого резервируемых блоков,

первым входам четвертой и пятой схем сравнения, к первому и второму входам шестой схемы сравнения, выход второго резервируемого блока соединен -с вторыми входами четвертой и пятой схем сравнения,

выходы которых, а также выходы первой- третьей и шестой схем сравнения подключены к соответствующим информационным входам коммутатора сигналов отказа, первый-четвертый выходы которого соединены

соответственно с управляющими входами разрешения счета первого-четвертого счетчиков сбоев, счетные входы которых подключены к первому входу синхронизации устройства, второй вход синхронизации которого соединен с входами установки в О первого-четвертого счетчиков сбоев, выходы старшего разряда каждого из которых подключены к собственным входам блокировки и соответствующим управляющим

входам коммутатора сигналов отказа, пер- вый-третий выходы которого соединены с соответствующими управляющими входами коммутатора данных и первым-третьим входами элемента И, выход которого является выходом сигнала отказа устройства.

Фие.1

30

п п п п п п п п п п п п п п п t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реконфигурации резервируемых блоков | 1990 |

|

SU1756893A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Резервированная система | 1982 |

|

SU1089771A1 |

| Резервируемое устройство | 1990 |

|

SU1732505A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И РЕЗЕРВИРОВАНИЯ ИНФОРМАЦИОННОЙ СИСТЕМЫ | 2010 |

|

RU2453079C2 |

| Резервированное устройство | 1991 |

|

SU1833877A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| Адаптивное четырехканальное резервированное устройство | 1990 |

|

SU1742821A1 |

| Устройство для контроля и реконфигурации дублированной системы | 1991 |

|

SU1807489A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1989 |

|

SU1667280A1 |

Изобретение относится к цифровой вычислительной технике и автоматике и может быть использовано при построении высоконадежных устройств на основе однотипных резервируемых блоков Целью изобретения является повышение надежности функционирования устройства Устройство содержит первый-четвертый резервируемые блоки, коммутатор данных, регистр данных, первую-шестую схемы сравнения, первый- четвертый счетчики сбоев, элемент И, коммутатор сигналов отказа 3 ил

23

п

П

Фие.1

К

33

фие.З

| Устройство для контроля вычислительных машин | 1986 |

|

SU1390612A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| и Мкртунян И.Б | |||

| Основы эксплуатации ЭВМ М.: Энергоатомиздат, 1988, с | |||

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-07-15—Публикация

1990-05-21—Подача