Изобретение относится к области микроэлектроники, а именно к конструкции интегральных схем, содержащих биполярные транзисторы (БТ).

Целью настоящего изобретения является обеспечение одновременной защиты от перенапряжения эмиттерного, коллекторного p-n-переходов и цепи коллектор-эмиттер основного транзистора при одновременном увеличении граничной частот усиления основного транзистора.

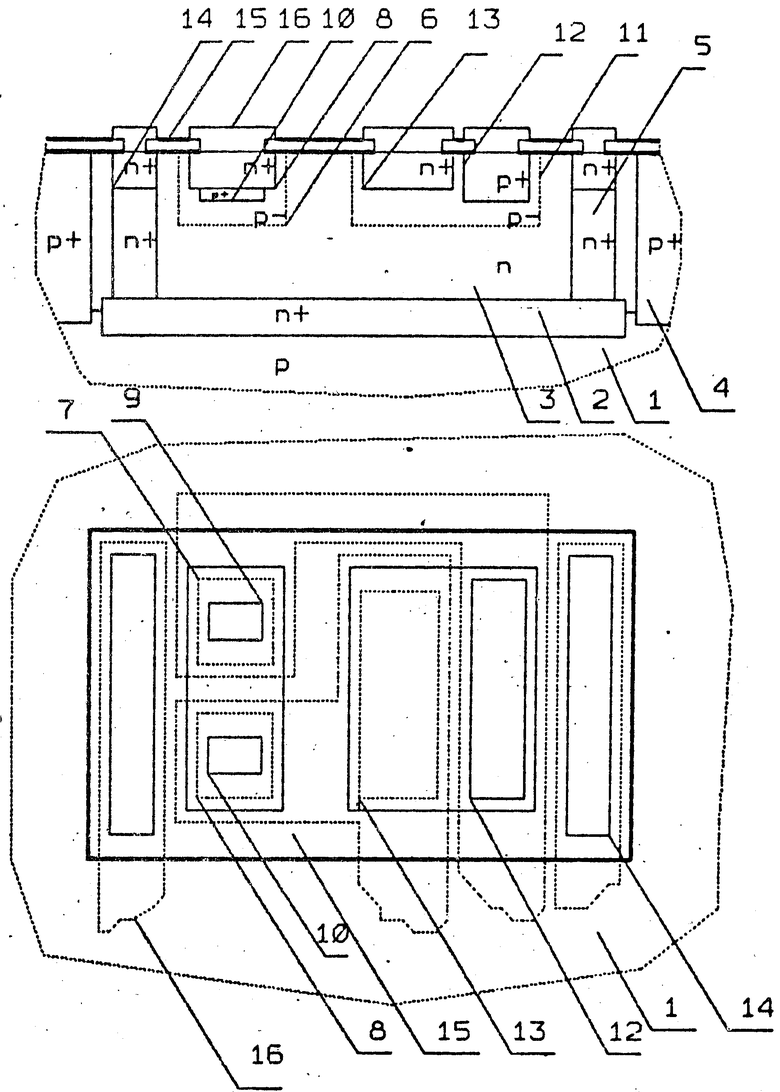

Сущность изобретения поясняет чертеж, на котором изображена интегральная схема в соответствии с формулой изобретения, где:

1 - полупроводниковая подложка p-типа проводимости;

2 - скрытый слой коллектора n+-типа проводимости;

3 - эпитаксиальный слой, коллектор n-типа проводимости;

4 - изолирующие области p+-типа проводимости;

5 - область глубокого коллектора n+-типа проводимости;

6 - область базы защитного транзистора p-типа проводимости;

7 - область первого эмиттера защитного транзистора n+-типа проводимости;

8 - область второго эмиттера защитного транзистора n+-типа проводимости;

9 - высоколегированная область p+типа проводимости, расположенная под донной частью первого эмиттера защитного транзистора;

10 - высоколегированная область p+типа проводимости, расположенная под донной частью второго эмиттера защитного транзистора;

11 - область базы основного транзистора p-типа проводимости;

12 - подконтактная область базы основного транзистора p+-типа проводимости;

13 - области эмиттера основного транзистора n+-типа проводимости;

14 - подконтактная область коллектора n+-типа проводимости;

15 - маска диэлектрического материала;

16 - контакты к областям.

В защитном транзисторе первый эмиттер n+-типа - 7, p+-область 9, p--область 6, n--область 3, n+-области 2, 5, 14 образуют вертикальный n+-p+-p--n--n+ (n-p-n) БТ и в этом случае при перенапряжении пробивается защитный вертикальный БТ, обеспечивая стабилизацию напряжения коллектор-база основного транзистора, т.е. его защиту от перенапряжения.

В защитном транзисторе второй эмиттер n+-типа 8, p+-область 10, p--область 6, n--область 3, n+-области 2,5,14 образуют вертикальный n+-p+-p--n--n+(n-p-n) БТ и в первом случае при перенапряжении происходит пробой защитного вертикального БТ, чем обеспечивается стабилизация напряжения коллектор-эмиттер основного транзистора, т.е. его защита от перенапряжения. В другом случае после пробоя указанного защитного вертикального БТ происходит стабилизация обратного напряжения коллектор-эмиттер основного транзистора и его защита от перенапряжения при инверсном включении.

В защитном транзисторе первый и второй эмиттеры n+-типа с высоколегированными p+-областями 9, 10 и p--областью 6 образуют горизонтальный n+-p+-p--p+-n+ (n-p-n) защитный БТ, который включен параллельно эмиттеру и базе основного БТ. При перенапряжении пробивается защитный горизонтальный БТ, стабилизируя напряжение эмиттер-база основного транзистора и защищая его от перенапряжения.

Интегральная схема работает известным образом. При перенапряжении на соответствующем переходе (промежутке) пробивается подключенная параллельно этому переходу вертикальная (горизонтальная) структура защитного транзистора, входящего в интегральную схему (ИС) и предотвращает дальнейшее увеличение напряжения и пробой основного транзистора.

Уменьшение площади кристалла связано с интегрированием в одну ИС основного и защитного транзисторов. В свою очередь в защитном транзисторе сформированы структуры вертикального и горизонтального БТ. Причем его электрические параметры и конструкция обеспечивают одновременно защиту в основном транзисторе от перенапряжения обоих p-n-переходов и цепи коллектор-эмиттер как при прямом, так и при инверсном включении. За счет резкого уменьшения площади, по сравнению с прототипом при одновременной защите p-n-переходов и цепи коллектор-эмиттер, в данном решении пропорционально уменьшаются и значения емкостей эмиттерного и коллекторного p-n-переходов. Это в свою очередь обеспечивает увеличение граничной частоты при одновременной защите p-n-переходов и промежутка коллектор-эмиттер основного транзистора.

Пример реализации. На полупроводниковой подложке 1 марки КДБ 10 p--типа проводимости толщиной 380 мкм, диаметром 76,0 мм и ориентацией < 100> нанесен эпитаксиальный слой 3n--типа проводимости толщиной 5,0 мкм и удельным сопротивлением ρ= 1,0 Ом˙см. На подложке перед эпитаксиальным наращиванием сформирован путем легирования сурьмы скрытый слой 2n+-типа проводимости толщиной 6,0 мкм и поверхностным сопротивлением Rs=250 м/квадрат. В эпитаксиальном слое 3 разделительной диффузией с Rs= 40 Ом/□ сформированы изолирующие области 4 p+-типа проводимости, смыкающиеся с подложкой и образующие изолированную зону n--типа проводимости, являющуюся общим коллектором основного и защитного транзисторов. Область глубокого коллектора 5n+-типа проводимости сформирована имплантацией с поверхностным сопротивлением Rs=25-30 Ом/□ и толщиной (глубиной залегания) 4-4,5 мкм.

В изолированной зоне n--типа сформированы базовые области 6 и 11 p--типа проводимости с Rs=700-900 Ом/□ соответственно защитного и основного транзисторов толщиной 1,2-1,5 мкм. В базе 11 p--типа проводимости основного транзистора сформированы подконтактные области 12 p+-типа проводимости с поверхностным сопротивлением Rs=100±20 Ом/□ и толщиной 0,9-1,3 мкм, одновременно сформированы высоколегированные области p+-типа проводимости 9 и 10 в базе защитного транзистора. Затем в базах 6 и 11 обоих транзисторов и подконтактной области коллектора имплантацией формируют области n+-типа проводимости 7, 8, 13, 14 соответственно. Толщина n+-областей 0,7-0,9 мкм, поверхностное сопротивление Rs= 25-35 Ом/□ . На поверхности эпитаксиальной пленки сформирован маскирующий слой SiО2 - 15, в котором вскрыты окна и сформированы контакты на основе Si+Al к эмиттерным областям основного и защитного транзисторов, а также к базе основного транзистора и общему коллектору. Размеры областей следующие: изолированной (островной зоны n--типа проводимости) 60х40 (мкм2), базы основного и защитного транзисторов p--типа проводимости - 26х20 и 21х14 (мкм2), соответственно; двух приконтактных областей p+-типа проводимости основного транзистора 22х4 (мкм2), высоколегированных областей p+-типа проводимости защитного транзистора 5х4 (мкм2); n+-типа проводимости эмиттера основного транзистора - 20х2 (мкм2) n+-типа двух эмиттеров защитного транзистора 8х6 (мкм2) (оба эмиттера защитного транзистора располагаются над высоколегированными p+-областями), подконтактной области коллектора n+-типа проводимости 42х3 (мкм2); такой же размер области глубокого коллектора.

Использование БТ по данному решению с отсоединенной базой и дополнительными областями под обоими эмиттерами обеспечило одновременную защиту обоих p-n-переходов и промежутка коллектор-эмиттер основного транзистора и следующие величины напряжения пробоя:

коллектор-эмиттер 1; эмиттер 2 - по 17,4 В, инверсное - по 4,8 В;

коллектор-база - 24,2 В;

эмиттер 1 - эмиттер 2 (эмиттер 2 - эмиттер 1) - по 5,5 В.

Основной транзистор имеет следующие пробивные напряжения:

коллектор-эмиттер (при отсоединенной базе) - 12 В, инверсное - 6,8 В, коллектор-база - 24,2 В;

эмиттер-база - 7,4 В.

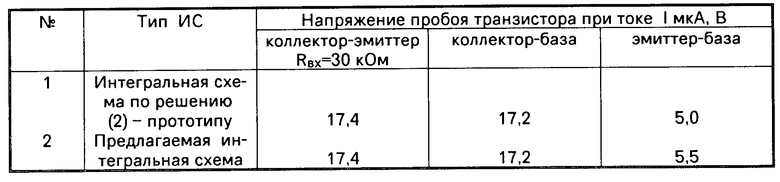

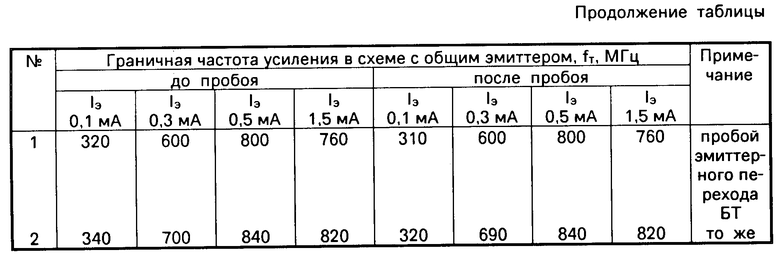

Технические характеристики прототипа и данного решения приведены в таблице.

Из таблицы видно, что введение защиты позволяет значительно стабилизировать изменение fт до и после пробоя, данное решение не только стабилизирует изменение fг, но незначительно его увеличивает по сравнению с прототипом (в таблице у БТ пробивается эмиттерный переход).

Дополнительным преимуществом данного решения является то, что пробивное напряжение эмиттер-база на 0,5 В больше по сравнению с прототипом, что позволяет более широко использовать максимальное напряжение эмиттер-база.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральная биполярная структура | 1990 |

|

SU1746440A1 |

| ИНТЕГРАЛЬНЫЙ БИПОЛЯРНЫЙ ТРАНЗИСТОР | 1989 |

|

SU1831966A3 |

| ТРАНЗИСТОР С ЗАЩИТОЙ ОТ ПЕРЕНАПРЯЖЕНИЙ | 1991 |

|

RU2037237C1 |

| ИНТЕГРАЛЬНЫЙ ТРАНЗИСТОР, УСТОЙЧИВЫЙ К ОБРАТНОМУ ВТОРИЧНОМУ ПРОБОЮ | 1991 |

|

RU2024995C1 |

| ИНТЕГРАЛЬНЫЙ ТРАНЗИСТОР С ЗАЩИТОЙ ОТ ПЕРЕНАПРЯЖЕНИЙ | 1998 |

|

RU2175461C2 |

| ИНТЕГРАЛЬНАЯ СХЕМА | 1992 |

|

RU2078390C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИС НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 1988 |

|

SU1538830A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1979 |

|

SU760837A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНЫХ СТРУКТУР | 1986 |

|

SU1369592A2 |

Использование: конструкции интегральных схем, содержащие биполярные транзисторы. Сущность изобретения: интегральная схема включает основной и защитный биполярные транзисторы одного типа проводимости, выполненные на полупроводниковой подложке. В эпитаксиальном слое сформированы области баз и эмиттеров основного и защитного транзисторов. Область коллектора является общей для транзисторов. В области базы защитного транзистора сформирована область второго эмиттера. Под первым и вторым эмиттерами сформированы высоколегированные области того же типа проводимости, что и область базы, перекрывающие донные части эмиттера. Области база-эмиттер основного транзистора соединены соответственно с областями первого и второго эмиттеров защитного транзистора. Электрические параметры транзисторов удовлетворяют определенным соотношениям. Схема обеспечивает возможность защиты от перенапряжений соответствующих элементов основного транзистора при прямом или инверсном его включении. 1 ил.

ИНТЕГРАЛЬНАЯ СХЕМА, содержащая основной и защитный биполярные транзисторы одного типа проводимости, включающие области коллектора, эмиттера, базы и высоколегированную область, расположенную в базовой области защитного транзистора, прилегающую к донной части эмиттерной области и имеющую тип проводимости базовой области, при этом область коллектора выполнена общей для основного и защитного транзисторов, отличающаяся тем, что, с целью обеспечения одновременной защиты от перенапряжения эмиттерного, коллекторного p - n - переходов и цепи коллектор - эмиттер основного транзистора при одновременном увеличении граничной частоты усиления основного транзистора, в области базы защитного транзистора дополнительно сформированы область второго эмиттера и высоколегированная область, расположенная в базовой области, прилегающая к донной части дополнительной эмиттерной области и имеющая тип проводимости области базы, области базы и эмиттера основного транзистора соединены соответственно с областями эмиттеров первого и второго защитных транзисторов.

| Авторское свидетельство СССР N 1611171, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-03-27—Публикация

1991-01-14—Подача