Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов.

Цель изобретения - упрощение устройства.

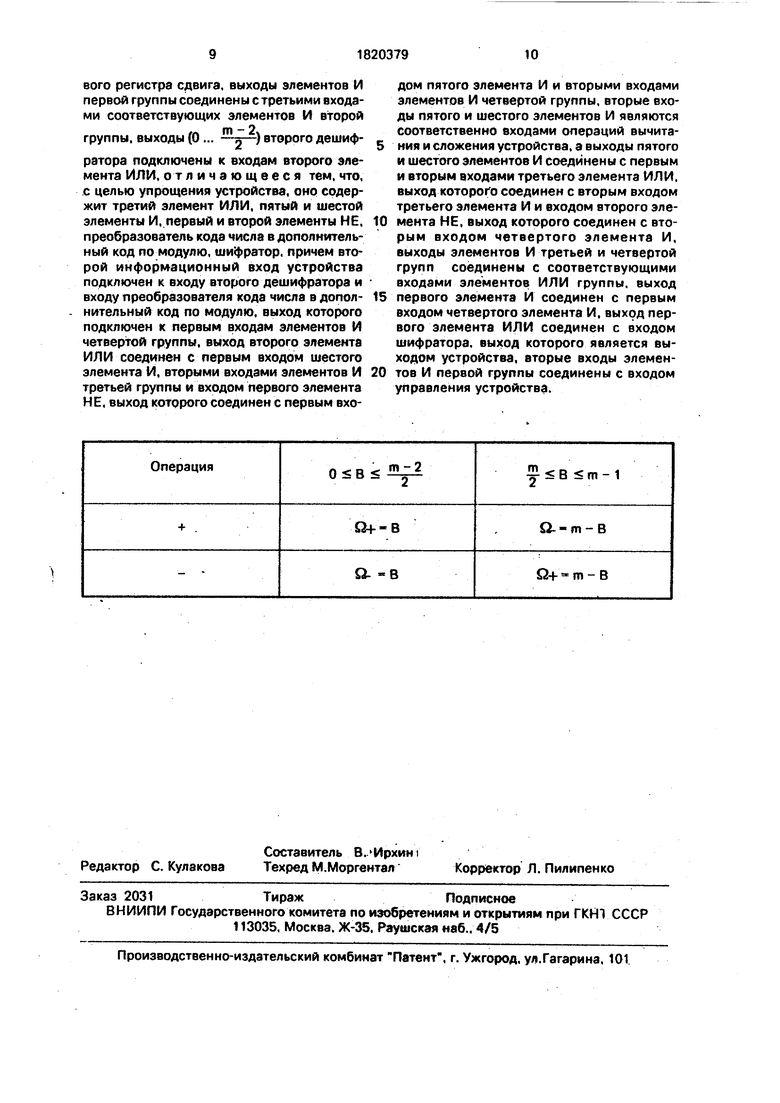

Сущность изобретения состоит в упрощении устройства за счет исключения из схемы трех сумматоров по модулю т, шести групп элементов И, группы элементов ИЛИ, элемента ИЛИ. умножителя частоты и их логических связей при сохранении всех функциональных и технических возможностей устройства путем введения двух инверторов, двух элементов И, одного элемента ИЛИ, шифратора. Обозначим через Q+ B- положительный сдвиг на В разрезов содержимого КСР. Рассмотрим связь проводимой модульной операции расположения второго операнда (В), минимальное количество сдвигов КСР, необходимое для получения результата, и направление сдвига. Полученные результаты представлены в таблице.

Эта таблица может быть реализована при помощи только одного преобразователя кода числа в дополнительный код по модулю. Дальнейшее упрощение устройства возможно уменьшением количества выхода дешифратора операнда В вдвое, т.е. пред- ставлять в унитарном коде только

„ О

О В :Ј. Ш-х- , а остальные значения операнда В реализовать с помощью инвертора.

Положительный эффект от внедрения изобретения состоит в упрощении устройства: уменьшении количества оборудования и упрощении количества логических связей между элементами устройства, повышении эффективности использования оборудования. Данное обстоятельство позволяет уменьшить стоимость операции модульного сложения и вычитания, а.также уменьшить стоимость всего устройства.

Техническое преимущество изобретения состоит в упрощении устройства; что повышает надежность устройства сложения и вычитания по модулю т.. .

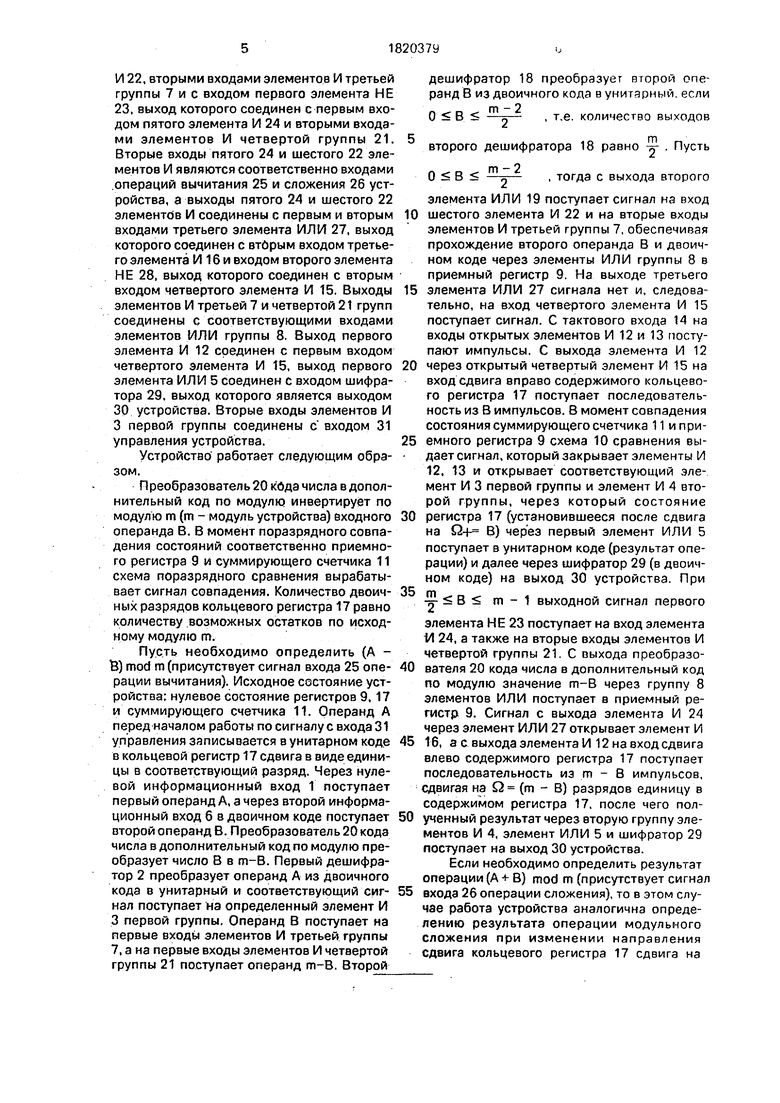

На чертеже представлена структурная схема устройства, где 1 - первый информационный вход устройства, 2 - первый дешифратор, 3 - первая группа элементов И, 4 - вторая группа элементов И, 5 - элемент ИЛИ. 6- второй информационный вход устройства, 7 - третья группа элементов И, 8 - группа элементов ИЛИ, 9 - приемный регистр. 10 - схема сравнения, 11 - суммирующий счетчик, 12 - первый элемент И, 13 - второй элемент И, 14 - тактовый вход

устройства. 15 - четвертый элемент И, 16 - третий элемент И, 17 - кольцевой регистр сдвига, 18 - второй дешифратор, 19 - второй элемент ИЛИ, 20- преобразователь кода

числа в дополнительный код по модулю, 21 - четвертая группа элементов И, 22 - шестой элемент И, 23 - первый элемент НЕ, 24 - пятый элемент И, 25 - вход операции вычитания устройства, 26 - вход операции

0 сложения устройства. 27 - третий элемент ИЛИ, 28 - второй элемент НЕ, 29 - шифратор, 30 - выход устройства, 31 - вход управления устройства.

Первый Информационный вход 1 устройства подключен к входу первого дешифратора 2, выходы которого подключены к первым входам соответствующих элементов И 3 первой группы. Выходы элементов И 4 второй группы соединены с соответству0 ющими входами первого элемента ИЛИ 5, а первые входы элементов И 4 второй группы соединены с соответствующими выходами кольцевого регистра 17 сдвига. Второй информационный вход 6 устройства соединен

5 с первыми входами элементов И третьей . группы 7. Выходы элементов ИЛИ группы 8 соединены с информационными входами приемного регистра 9, выходы которого соединены с первыми информационными вхо0 дами схемы 10 сравнения. Вторые информационные входы последней соединены с выходами суммирующего счетчика 11, вход которого соединен с выходом втб- рого элемента И 13. Выход схемы 10 срав5 нения соединен с первыми входами первого 12 и второго 13 элементов И, с вторыми входами элементов И 4 второй группы. Тактовый вход 14 устройства соединен с вторыми входами первого 12 и второго. 13

0 элементов И. Первый вход третьего элемента И 16 соединён с первым входом четвертого элемента И 15, выходы третьего 16 и четвертого 15 элементов И соединены соответственно с входами сдвига вправо содер5 жимого кольцевого регистра 17 сдвига и с входом сдвига влево содержимого кольцевого регистра 17 сдвига. Выходы элементов И 3 первой группы соединены с третьими входами соответствующих элементов И 4

0m - 9

второй группы, выходы (0... -у-) второго

дешифратора 18 подключены к входам второго элемента ИЛИ 19. Второй информационный вход 6 устройства подключен к входу 5 второго дешифратора 18 и к входу преобразователя 20 кода числа в дополнительный код по модулю, выход которого подключен к первым входам элементов И четвертой группы 21. Выход второго элемента ИЛИ 19 соединен с первым входом шестого элемента

И 22, вторыми входами элементов И третьей группы 7 и с входом первого элемента НЕ 23, выход которого соединен с первым входом пятого элемента И 24 и вторыми входами элементов И четвертой группы 21. Вторые входы пятого 24 и шестого 22 элементов И являются соответственно входами .операций вычитания 25 и сложения 26 устройства, а выходы пятого 24 и шестого 22 элементов И соединены с первым и вторым входами третьего элемента ИЛИ 27, выход которого соединен с вторым входом третьего элемента И 16 и входом второго элемента НЕ 28, выход которого соединен с вторым входом четвертого элемента И 15. Выходы элементов И третьей 7 и четвертой 21 групп соединены с соответствующими входами элементов ИЛИ группы 8. Выход первого элемента И 12 соединен с первым входом четвертого элемента И 15, выход первого элемента ИЛИ 5 соединен с входом шифратора 29, выход которого является выходом 30 устройства. Вторые входы элементов И 3 первой группы соединены с входом 31 управления устройства.

Устройство работает следующим образом.

Преобразователь 20 кбда числа в дополнительный код по модулю инвертирует по модулю m (m - модуль устройства) входного операнда В. В момент поразрядного совпадения состояний соответственно приемного регистра 9 и суммирующего счетчика 11 схема поразрядного сравнения вырабатывает сигнал совпадения. Количество двоичных разрядов кольцевого регистра 17 равно количеству возможных остатков по исходному модулю т.

Пусть необходимо определить (А - В) mod m (присутствует сигнал входа 25 операции вычитания). Исходное состояние устройства: нулевое состояние регистров 9,17 и суммирующего счетчика 11. Операнд А перед началом работы по сигналу с входа 31 управления записывается в унитарном коде в кольцевой регистр 17 сдвига в виде единицы в соответствующий разряд. Через нулевой информационный вход 1 поступает первый операнд А, а через второй информационный вход б в двоичном коде поступает второй операнд В. Преобразователь 20 кода числа в дополнительный код по модулю преобразует число В в m-В. Первый дешифратор 2 преобразует операнд А из двоичного кода в унитарный и соответствующий сигнал поступает на определенный элемент И 3 первой группы. Операнд В поступает на первые входы элементов И третьей группы 7, а на первые входы элементов И четвертой группы 21 поступает операнд m-В. Второй

дешифратор 18 преобразует второй операнд В из двоичного кода в унитарный, если

О В -s- , т.е. количество выходов

5гп

второго дешифратора 18 равно . Пусть

О В

гл-2

, тогда с выхода второго

элемента ИЛИ 19 поступает сигнал на вход

шестого элемента И 22 и на вторые входы элементов И третьей группы 7, обеспечивая прохождение второго операнда В и двоичном коде через элементы ИЛИ группы 8 в приемный регистр 9. На выходе третьего

элемента ИЛИ 27 сигнала нет и, следовательно, на вход четвертого элемента И 15 поступает сигнал. С тактового входа 14 на входы открытых элементов И 12 и 13 поступают импульсы. С выхода элемента И 12

через открытый четвертый элемент И 15 на вход сдвига вправо содержимого кольцевого регистра 17 поступает последовательность из В импульсов. В момент совпадения состояния суммирующего счетчика 11 иприемного регистра 9 схема 10 сравнения выдает сигнал, который закрывает элементы И 12. 13 и открывает соответствующий элемент И 3 первой группы и элемент И 4 второй группы, через который состояние

регистра 17 (установившееся после сдвига на Q-f В) через первый элемент ИЛИ 5 поступает в унитарном коде (результат операции) и далее через шифратор 29 (в двоичном коде) на выход 30 устройства. При

-у В m - 1 выходной сигнал первого

элемента НЕ 23 поступает на вход элемента VI 24, а также на вторые входы элементов И четвертой группы 21. С выхода преобразователя 20 кода числа в дополнительный код по модулю значение m-В через группу 8 элементов ИЛИ поступает в приемный регистр 9. Сигнал с выхода элемента И 24 через элемент ИЛИ 27 открывает элемент И

16, а с выхода элемента И 12 на вход сдвига влево содержимого регистра 17 поступает последовательность из m - В импульсов, сдвигая на Q (т - В) разрядов единицу в содержимом регистра 17. после чего полученный результат через вторую группу элементов И 4, элемент ИЛИ 5 и шифратор 29 поступает на выход 30 устройства.

Если необходимо определить результат операции (А + В) mod m (присутствует сигнал

входа 26 операции сложения), то в этом случае работа устройства аналогична определению результата операции модульного сложения при изменении направления сдвига кольцевого регистра 17 сдвига на

противоположное для данного второго операнда В.

Рассмотрим примеры конкретного выполнения операции для m 5. В этом случае исходное состояние кольцевого регистра 17 сдвига можно схематично представить в виде

С

О-0-0-0-0-

П р и м е р. 1. Пусть необходимо определить результат операции модульного вычитания для А - 2, В 4 (А и В - операнды). По сигналу с входа 31 управления в регистре 17 установлено состояние

Е

0-0-1-0-0

3

Так как - В , то сигнал с выхода

элемента ИЛИ 27 открывает элемент И 16. В приемном регистре 9 будет записано 5 - 4 1 в двоичном коде. Следовательно, происходит сдвиг на один разряд регистра 17 в отрицательном направлении (Q- 1). Состояние регистра 17 будет

рО-0-0-1 -0-|.

Это соответствует унитарному коду числа 3- (2 - 4) mod 5 3 mod 5.

Пример 2. Пусть необходимо определить результат операции модульного сложения для А 2, А 1 (А и В - операнды). Так т-2

как 0 В

, то открывается элемент

И 16. В приемном регистре 9 будет записано число 1 в двоичном коде. Следовательно, происходит сдвиг на один разряд регистра 17 в отрицательном направлении. Исходное состояние регистра 17 будет как и в первом примере, а конечное

rO-0-0-1-0-j

Это соответствует унитарному коду числа 3 (А + В) mod т (2 + 1) mod 5 5

Техническое преимущество изобретения по сравнению с прототипом состоит в существенном упрощении устройства за счет исключения из схемы трех сумматоров по модулю, шести групп элементов И, группы элементов ИЛИ элемента ИЛИ ит.д. при сохранении всех функциональных и технических возможностей устройства путем,введения преобразователя кода числа в дополнительный код по модулю, двух элементов НЕ, двух элементов И, одного элемента ИЛИ.

Положительный эффект использования изобретения состоит в упрощении устройства, повышении коэффициента использования оборудования, что уменьшает экономические затраты на построение и

0 эксплуатацию устройства, а также повышает надежность устройства в целом. Дополнительным положительным эффектом является повышение быстродействия выполнения модульных операций сложения и

5 вычитания примерно в 2 1одат раза.

Достоверность достижения цели подтверждается конкретным примером выполнения модульных операций сложения и вычитания для модуля m 5.

0

Формул а из о бретени я Устройство для сложения и вычитания чисел по модулю, содержащее первый и второй дешифраторы, приемный регистр, сум5 мирующий счетчик, кольцевой регистр . сдвига, схему сравнения, первый и второй элементы ИЛИ. группу элементов ИЛИ, первую - четвертую группы элементов И, первый - четвертый элементы И, причем

0 первый информационный вход устройства подключен к входу первого дешифратора, выходы которого подключены к первым входам соответствующих элементов И первой группы, выходы элементов И второй группы

5 соединены е соответствующими входами первого элемента ИЛИ, а первые входы элементов И второй группы соединены с соот- ветствующими выходами кольцевого регистра сдвига, второй информационный

0 вход устройства соединен с первыми входами элементов И третьей группы, выходы элементов ИЛИ группы соединены с инфор- . мационными входами приемного регистра, выходы которого соединены с первыми ин5 формационными входами схемы сравнения, : вторые информационные входы которой соединены с выходами суммирующего счетчика, вход которого соединен с выходом третьего элемента И, выход схемы сравне0 ния соединен с первыми входами первого и второго элементов И, с вторыми входами элементов И второй группы, тактовый вход устройства соединен с вторыми входами первого и второго элементов И, первый вход

5 третьего элемента И соединен с первым входом четвертого элемента И, выходы третьего и четвертого элементов И соединены соответственно с входами сдвига вправо содержимого кольцевого регистра сдвига и с входом сдвига влево содержимого кольцевого регистра сдвига, выходы элементов И первой группы соединены с третьими входами соответствующих элементов И второй

Л

группы, выходы (0... -2-) второго дешифратора подключены к входам второго элемента ИЛИ,отличающееся тем,что, с целью упрощения устройства, оно содержит третий элемент ИЛИ, пятый и шестой элементы И, первый и второй элементы НЕ, преобразователь кода числа в дополнительный код по модулю, шифратор, причем второй информационный вход устройства подключен к входу второго дешифратора и входу преобразователя кода числа в дополнительный код по модулю, выход которого подключен к первым входам элементов И четвертой группы, выход второго элемента ИЛИ соединен с первым входом шестого элемента И, вторыми входами элементов И третьей группы и входом первого элемента НЕ, выход которого соединен с первым входом пятого элемента И и вторыми входами элементов И четвертой группы, вторые входы пятого и шестого элементов И являются соответственно входами операций вычитания и сложения устройства, а выходы пятого и шестого элементов И соединены с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И и входом второго элемента НЕ. выход которого соединен с вторым входом четвертого элемента И, выходы элементов И третьей и четвертой групп соединены с соответствующими входами элементов ИЛИ группы, выход

первого элемента И соединен с первым входом четвертого элемента И, выход первого элемента ИЛИ соединен с входом шифратора, выход которого является выходом устройства, вторые входы элементов И первой группы соединены с входом управления устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1991 |

|

RU2018935C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1999 |

|

RU2156998C1 |

| Арифметическое устройство по модулю | 1989 |

|

SU1756881A1 |

| Устройство для сложения и вычитания чисел по модулю Р | 1986 |

|

SU1388850A1 |

| Арифметическое устройство по модулю | 1991 |

|

SU1809437A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ | 1999 |

|

RU2157560C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2145112C1 |

| Устройство для сложения и вычитания чисел по модулю | 1990 |

|

SU1755275A1 |

| Устройство для сложения и вычитания чисел по модулю @ | 1985 |

|

SU1312572A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ ПО МОДУЛЮ | 1997 |

|

RU2133495C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов. Цель изобретения -.упрощение устройства. Цель достигается за счет реализации операций модульного сложения и вычитания при помощи одного преобразователя 20 кода числа в дополнительный код по модулю путем введения третьего элемента ИЛИ 27, пятого 24 и шестого 22 элементов И, первого 23 и второго 28 элементов НЕ, преобразователя 20 кода числа в дополнительный код по модулю, шифратора 29 в устройство, содержащее дешифратор 2, первую и вторую группы элементов И 3,4, кольцевой регистр 17 сдвига, элементы И Т2, 13, 15, 16, группу 8 элементов ИЛИК приемный регистр 9, схему 10 сравненияГсчетчик 11, дешифратор 18, группы 7 и 21 элементов И. 1 табл. ,1 ил.

| Устройство для сложения и вычитания чисел по модулю @ | 1985 |

|

SU1247868A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сложения и вычитания чисел по модулю Р | 1984 |

|

SU1257643A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-06-07—Публикация

1991-03-26—Подача