Изобретение относится к испытательной технике и может быть использовано для определения параметров динамических характеристик объектов при проведении виброиспытаний.

Цель изобретения - расширение области применения способа определения резонансной частоты элементов конструкции за счет осуществления возможности определения характера асимметрии линейной резонансной характеристики и отсутствия необходимости введения двух усилителей с коэффициентами усиления, определяемыми в зависимости от двух скоростей разверток частоты.

Цель достигается тем, что по способу определения резонансной частоты элементов конструкции, заключающемуся в том, что дважды воздействуют на конструкцию возбуждающими колебаниями изменяющейся частоты, при каждом возбуждении измеряют сдвиг фаз между возбуждающими колебаниями и колебаниями элементов конструкции и фиксируют частоту, при которой колебания элементов конструкции отстают от возбуждающих колебаний на л/2, изменяют частоту возбуждающих колебаний с постоянной скоростью VL после достижения сдвигом фаз между возбуждающими колебаниями и колебаниями элементов конструкции величины я/2 повторяют развертку частоты с другой постоянной скоростью V2, в соответствии с изобретением повторно дважды воздействуют на конструкцию возбуждающими колебаниями изменяющейся частоты при скоростях развертки vi, va, причем направление изменения частоты противоположно направлению изменения при первом и втором воздействиях, и фиксируют третью и четверЁ

00

со

N5

СО GJ

тую частоты, при которых колебания элементов конструкции опережают возбуждающие на я/2 при скоростях развертки vi и V2 соответственно, а значение резонансной частоты (Do определяют из соотношения ал ом - о% о)з

(OH +OM)-(flJ2+uu)

гдеол, ад, «из и шц - первая, вторая, третья и четвертая частоты, при которых разность фаз колебания элементов конструкции и возбуждающих колебаний равна я/2.

Кроме того, определяют первую и вторую величины, равные разности первой и второй, четвертой и третьей зафиксированных частот соответственно, и при выполнении условий AI Ае; Ai А2; Ai Ag фиксируют асимметрию, при которой дорезонансная ветвь резонансной характеристики имеет большую, меньшую и одинаковую крутизну с за- резонансной ветвью резонансной характеристики соответственно.

Введенный новый алгоритм определения резонансной частоты элементов конструкции позволяет определять резонансную частоту независимо от скоростей развертки частоты по диапазону частот, что исключает необходимость введения усилителей, коэффициенты передачи которых зависят от скоростей развертки частоты. Одновременно определяют характер асимметрии резонансной характеристики за счет определения относительной крутизны дорезонансной и зарезонансной ветвей резонансной характеристики.

Известно, что сдвиг максимума резонансной динамической характеристики при скорости v развертки частоты равен

X Z,u,(1)

где .(2)

ft, Для обобщенной расстройки

.

О)

где Q - добротность симметричной резонансной характеристики.

На основании выражений (1), (2), (3) при скорости vi(v2) развертки частоты в сторону ее увеличения (уменьшения) и добротности Qi(Qa) дорезонансной (зарезонансной) ветви резонансной характеристики запишем соотношения

ес а

Р Р

(4а) (46) (4в) (4г)

0

5

0

5

0

5

0

5

0

5

(5а)

(56)

(6)

Из соотношений (4а) и (4в) ал а

Из соотношений (46) и (4г) аъ-Юо а

ftlo-UM Д

Из соотношений (5а) и (56) получим

ал UM о)з 0)0 (wi + UAJ) - (ад + сиз) Из соотношений (4а) и (46) получим

л

ол-йй 7T-(vi-v2)Qi; Шо

0)4-0)3 -(V1-V2)Q2. Шо

Так как К 4/flJb (vi-v2) для фиксированных vi, V2, оь - постоянный коэффициент, то

Ai (wi - ufc) KQu Ае («и - юз) К 02.(7)

Из соотношений (7) Ai Qi AI Q2 Если

Ai ( - 0)2) А2 (ОМ - ШЗ),

то QI 02, т.е. крутизна дорезонансной ветви больше крутизны зарезонансной ветви.

Если

Ai (ал - цг) Дг (UM - б«з), то Qi 02, т.е. крутизна дорезонансной ветви меньше крутизны зарезонансной ветви.

Если

Ai (ал - 0)2) - Ае (ам - ад) то 01 Q2, т.е. крутизны дорезонансной и зарезонансной ветвей резонансной характеристики одинаковы.

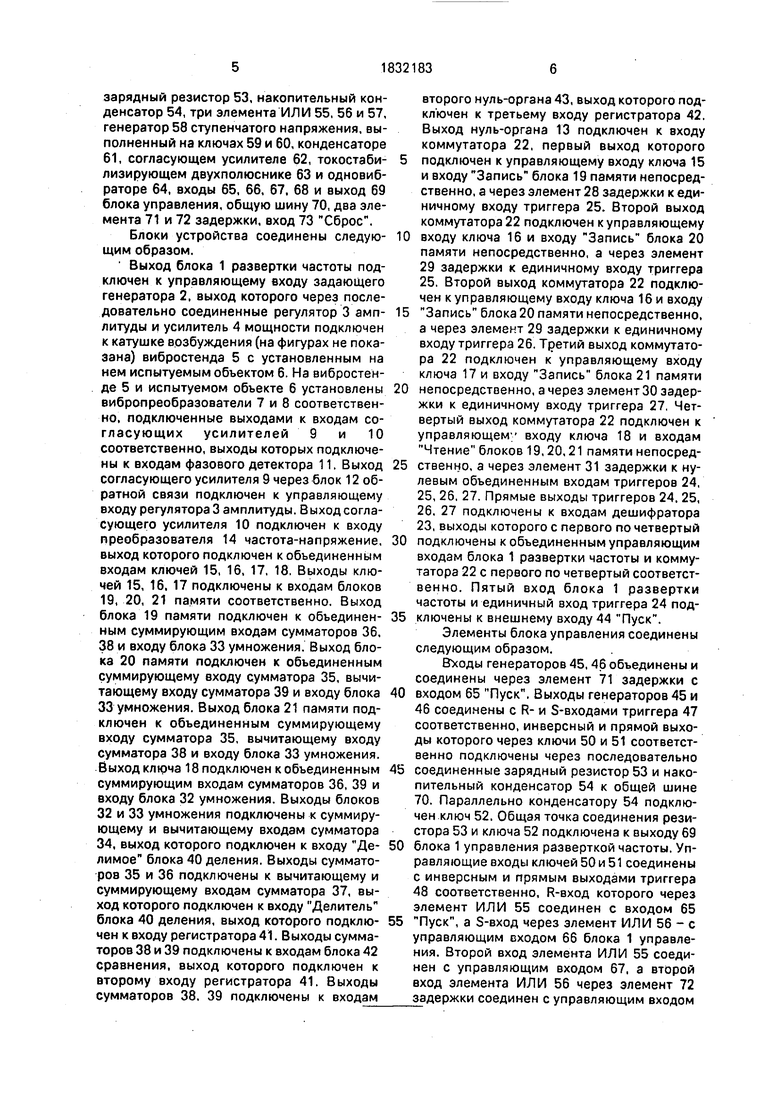

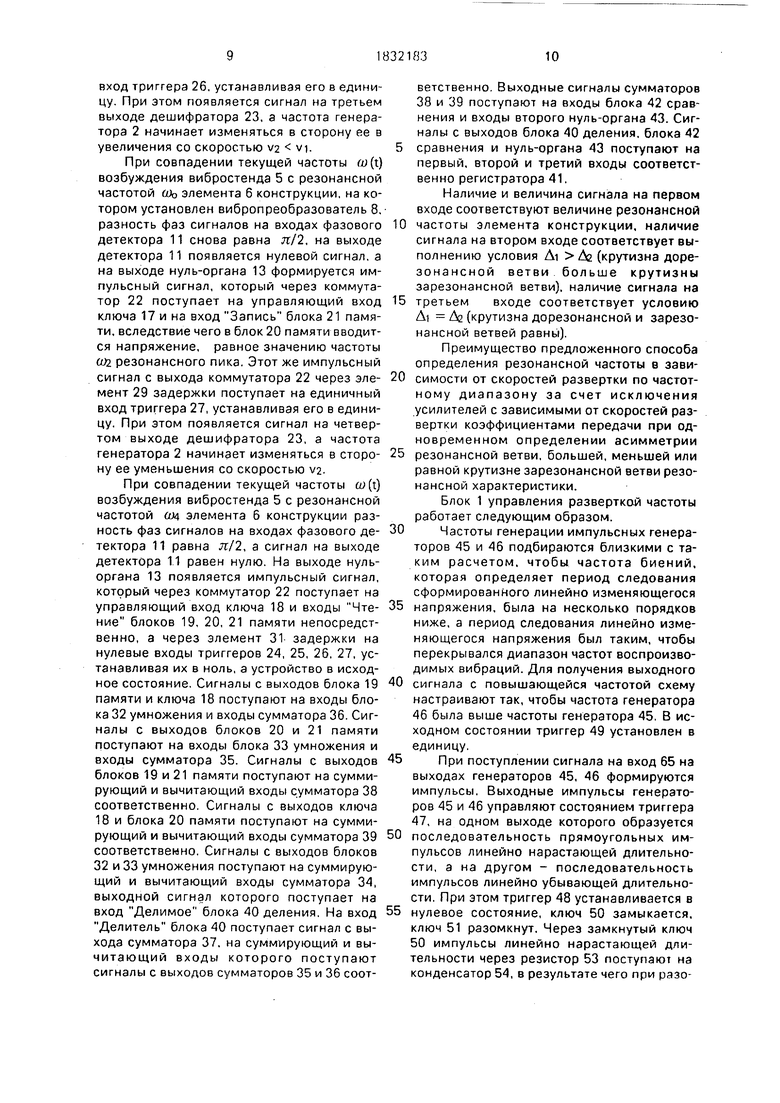

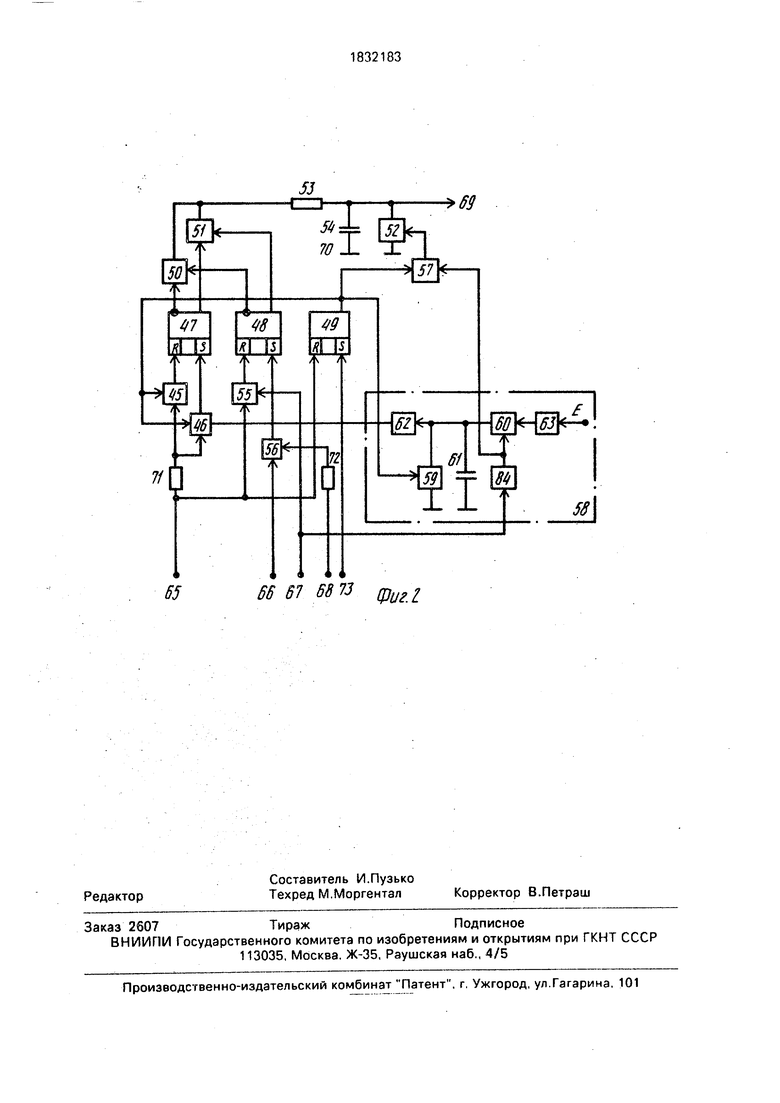

На фиг.1 - изображена блок-схема устройства для измерения резонансной частоты элементов конструкции; на фиг.2 - схема блока управления разверткой частоты.

Устройство содержат блок 1 управления разверткой частоты, задающий генератор 2, регулятор 3 амплитуды, усилитель 4 мощности, вибростенд 5 с установленным на нем испытуемым объектом 6, вибропреобразователи 7 и 8, согласующие усилители 9 и 10, фазовый детектор 11, блок 12 обратной связи, первый нуль-орган 13, преобразователи 14 частота-напряжение, ключи 15 и 16,17 и 18, три блока 19,20 и 21 памяти, коммутатор 22, дешифратор 23, четыре триггера 24, 25, 26 и 27, четыре элемента 28, 29, 30 и 31 задержки, два блока 32 и 33, умножения, шесть сумматоров 34, 35, 36, 37, 38 и 39, блок 40 деления, регистратор 41, блок 42 сравнения, второй нуль-орган 43, вход 44 Пуск.

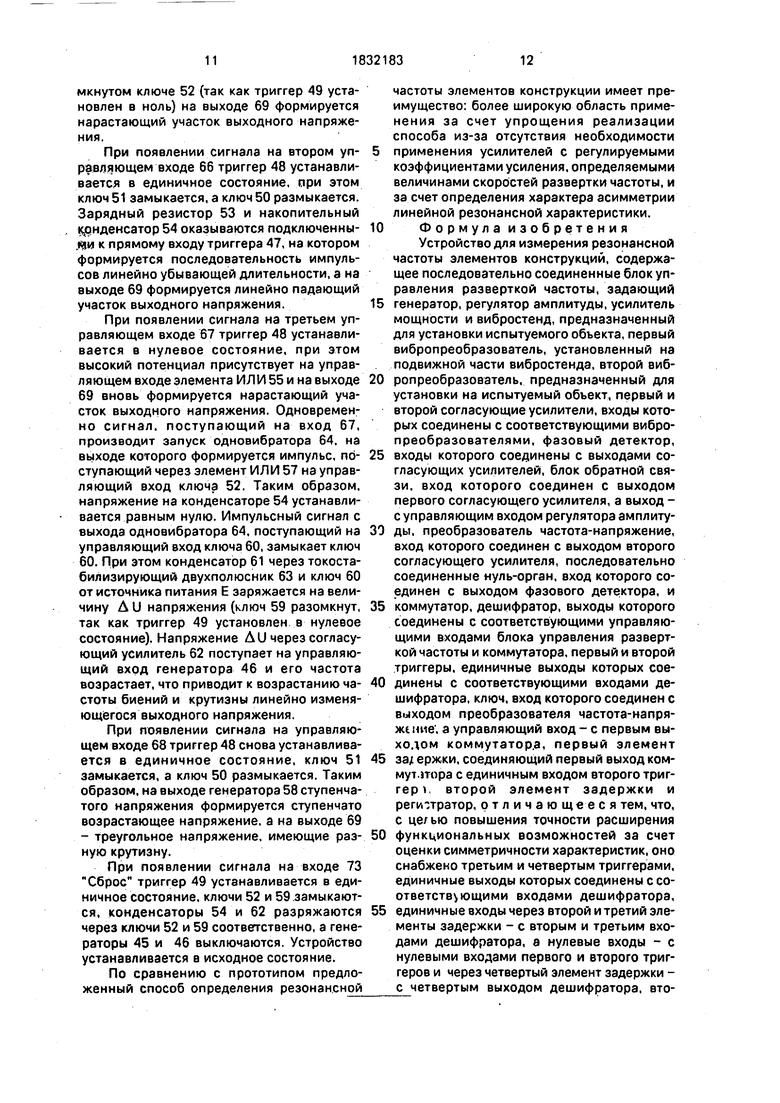

Блок 1 управления разверткой частоты содержит импульсные генераторы 45 и 46, триггеры 47, 48 и 49, ключи 50, 51 и 52,

зарядный резистор 53, накопительный конденсатор 54, три элемента ИЛИ 55, 56 и 57, генератор 58 ступенчатого напряжения, выполненный на ключах 59 и 60, конденсаторе 61, согласующем усилителе 62, токостаби- лизирующем двухполюснике 63 и одновиб- раторе 64, входы 65, 66, 67, 68 и выход 69 блока управления, общую шину 70, два элемента 71 и 72 задержки, вход 73 Сброс.

Блоки устройства соединены следующим образом.

Выход блока 1 развертки частоты подключен к управляющему входу задающего генератора 2, выход которого через последовательно соединенные регулятор 3 амплитуды и усилитель 4 мощности подключен к катушке возбуждения (на фигурах не показана) вибростенда 5 с установленным на нем испытуемым объектом 6. На вибростенде 5 и испытуемом объекте 6 установлены вибропреобразователи 7 и 8 соответственно, подключенные выходами к входам согласующих усилителей 9 и 10 соответственно, выходы которых подключены к входам фазового детектора 11. Выход согласующего усилителя 9 через блок 12 обратной связи подключен к управляющему входу регулятора 3 амплитуды. В ыход согласующего усилителя 10 подключен к входу преобразователя 14 частота-напряжение, выход которого подключен к объединенным входам ключей 15, 16, 17, 18. Выходы ключей 15, 16. 17 подключены к входам блоков 19, 20, 21 памяти соответственно. Выход блока 19 памяти подключен к объединенным суммирующим входам сумматоров 36, 38 и входу блока 33 умножения. Выход блока 20 памяти подключен к объединенным суммирующему входу сумматора 35, вычитающему входу сумматора 39 и входу блока 33 умножения. Выход блока 21 памяти подключен к объединенным суммирующему входу сумматора 35, вычитающему входу сумматора 38 и входу блока 33 умножения. Выход ключа 18 подключен к объединенным суммирующим входам сумматоров 36, 39 и входу блока 32 умножения. Выходы блоков 32 и 33 умножения подключены к суммирующему и вычитающему входам сумматора 34, выход которого подключен к входу Делимое блока 40 деления. Выходы сумматоров 35 и 36 подключены к вычитающему и суммирующему входам сумматора 37, выход которого подключен к входу Делитель блока 40 деления, выход которого подключен к входу регистратора 41. Выходы сумматоров 38 и 39 подключены к входам блока 42 сравнения, выход которого подключен к второму входу регистратора 41. Выходы сумматоров 38. 39 подключены к входам

второго нуль-органа 43, выход которого подключен к третьему входу регистратора 42. Выход нуль-органа 13 подключен к входу коммутатора 22, первый выход которого

5 подключен к управляющему входу ключа 15 и входу Запись блока 19 памяти непосредственно, а через элемент 28 задержки к единичному входу триггера 25. Второй выход коммутатора 22 подключен к управляющему

10 входу ключа 16 и входу Запись блока 20 памяти непосредственно, а через элемент 29 задержки к единичному входу триггера 25. Второй выход коммутатора 22 подключен к управляющему входу ключа 16 и входу

15 Запись блока 20 памяти непосредственно, а через элемент 29 задержки к единичному входу триггера 26. Третий выход коммутатора 22 подключен к управляющему входу ключа 17 и входу Запись блока 21 памяти

0 непосредственно, а через элементЗО задержки к единичному входу триггера 27, Четвертый выход коммутатора 22 подключен к управляющем входу ключа 18 и входам Чтение блоков 19,20,21 памяти непосред5 ственно, а через элемент 31 задержки к нулевым объединенным входам триггеров 24,

25,26, 27. Прямые выходы триггеров 24. 25,

26,27 подключены к входам дешифратора 23, выходы которого с первого по четвертый

0 подключены к объединенным управляющим входам блока 1 развертки частоты и коммутатора 22 с первого по четвертый соответст- венно. Пятый вход блока 1 развертки частоты и единичный вход триггера 24 под5 ключены к внешнему входу 44 Пуск.

Элементы блока управления соединены следующим образом.

Входы генераторов 45, 46 объединены и соединены через элемент 71 задержки с

0 входом 65 Пуск. Выходы генераторов 45 и 46 соединены с R- и S-входами триггера 47 соответственно, инверсный и прямой выходы которого через ключи 50 и 51 соответственно подключены через последовательно

5 соединенные зарядный резистор 53 и накопительный конденсатор 54 к общей шине 70. Параллельно конденсатору 54 подключен ключ 52. Общая точка соединения резистора 53 и ключа 52 подключена к выходу 69

0 блока 1 управления разверткой частоты. Управляющие входы ключей 50 и 51 соединены с инверсным и прямым выходами триггера 48 соответственно, R-вход которого через элемент ИЛИ 55 соединен с входом 65

5 Пуск, а S-вход через элемент ИЛИ 56 - с управляющим сходом 66 блока 1 управления. Второй вход элемента ИЛИ 55 соединен с управляющим входом 67, а второй вход элемента ИЛИ 56 через элемент 72

задержки соединен с управляющим входом

68. Управляющий вход ключа 52 соединен с выходом элемента ИЛИ 57. первый вход которого соединен с выходом одновибратора 64, а второй - с прямым выходом триггера 49. Первый вход 65 блока управления подключен к внешнему входу Пуск, объединенному с R-входом триггера 49, S-вход которого подключен к входу 73 Сброс. Прямой выход триггера 49 соединен с управляющим входом ключа 59. Потенциальный вход источника Е питания через последовательно соединенные токостаби- лизирующий двухполюсник 63, ключ 60 и согласующий усилитель 62 подключен к управляющему входу генератора 46 импульсов. Управляющий вход ключа 60 соединен с выходом одновибратора 64, управляющий вход которого соединен с входом 67. Выход ключа 60 через параллельно соединенные конденсатор 61 и ключ 59 подключен к общей шине 70. Управляющие входы генераторов 45 и 46 подключены к инверсному выходу триггера 49. На выходах генераторов 45, 46 формируются импульсные последовательности только при наличии единицы на управляющих входах, т.е. при наличии единичного потенциала на управляющем входе 65 Пуск.

Устройство работает следующим образом.

В исходном состоянии триггеры 24, 25, 26,27 установлены в ноль, частота задающего генератора 2 установлена равной нижней частоте диапазона развертки частоты. Коммутатор 22 установлен в нейтральное положение, при этом его вход отключен от выходов, а блок 12 развертки частоты установлен в исходное состояние, при котором частота генератора 2 фиксирована.

При поступлении сигнала на вход 44 Пуск триггер 24 устанавливается в единицу. При этом на первом выходе дешифратора 23 появляется сигнал, поступающий на первый управляющий вход коммутатора 22 и первый управляющий вход блока 1 развертки частоты. Дешифратор 23 функционируют следующим образом.

При наличии кодовой комбинации 0000 на входах дешифратора 23 на его выходах сигналов нет, при наличии кодовой комбинации 0001 появляется сигнал на первом выходе-дешифратора 23, при наличии кодовых комбинаций 0011, 0111, 1111 на выходах дешифратора 3 появляется сигнал на втором, третьем и.четвертом выходах дешифратора соответственно.

При наличии сигналов на первом входе блока 1 развертки частоты происходит увеличение частоты генератора 2 от начального значения, определяемого, например, нижней частотой диапазона развертки частоты, со скоростью vi. При наличии сигнала на втором входе блока 1 развертки частоты происходит уменьшение частоты генератора 2 со скоростью V2 VL При наличии сигналов на третьем (четвертом) входе блока 1 развертки частоты происходит увеличение (уменьшение) частоты генератора 2 со скоростью V2. Сигнал с выхода генератора 2

через регулятор 3 амплитуды и усилитель 4 мощности поступает в катушку подвижной части (обмотку возбуждения) вибростенда 5 с установленным на нем испытуемым объектом 6. Сигнал с выхода вибропреобразователя 7 через согласующий усилитель 9 и блок 12 обратной связи поступает на управляющий вход регулятора 3 амплитуды для стабилизации уровня возбуждения вибростенда 5. Сигналы с выходов согласующих

усилителей 9 и 10 поступают на входы фазового детектора 11.

Первоначально вводится режим развертки частоты генератора 2 со скоростью vi. При совпадении текущей частоты a)(i) возбуждения вибростенда 5 с резонансной частотой элемента 6 конструкции (объекта 6) разность фаз сигналов на входах фазового детектора 11 равна я/2, а сигнал на выходе детектора 11 равен нулю. При этом на выходе нуль-органа 13 появляется импульсный сигнал, который через коммутатор 22 поступает на управляющий вход ключа 15, и в блок 19 памяти вводится напряжение, равное значению частоты а резонансного пика, сдвинутой относительно резонансной частоты uh в статическом режиме. Кроме того, импульсный сигнал с выхода коммутатора 22 через элемент 28 задержки поступает на единичный вход триггера 25,

устанавливая его в единицу. При этом появляется сигнал на втором выходе дешифратора 23, а частота генератора 2 начинает изменяться со скоростью vi в сторону ее уменьшения.

При совпадении текущей частоты o(t) возбуждения вибростенда 5 с резонансной частотой элемента 6 конструкции разность фаз сигналов на входах фазового детектора 11 снова равна л/2, а сигнал на выходе

детектора 11 равен нулю. При этом на выходе нуль-органа 13 снова появляется импульсный сигнал, который через коммутатор 22 поступает на управляющий вход ключа 16 и на вход Запись блока 20 памяти, вследствне чего в блок 20 памяти вводится напряжение, равное значению частоты ыз резонансного пика. Этот же импульсный сигнал с выхода коммутатора 22 через элемент 29 задержки поступает на единичный

вход триггера 26, устанавливая его в единицу. При этом появляется сигнал на третьем выходе дешифратора 23, а частота генератора 2 начинает изменяться в сторону ее в увеличения со скоростью V2 VL

При совпадении текущей частоты y(t) возбуждения вибростенда 5 с резонансной частотой Шо элемента 6 конструкции, на котором установлен вибропреобразователь 8,- разность фаз сигналов на входах фазового детектора 11 снова равна я/2, на выходе детектора 11 появляется нулевой сигнал, а на выходе нуль-органа 13 формируется импульсный сигнал, который через коммутатор 22 поступает на управляющий вход ключа 17 и на вход Запись блока 21 памяти, вследствие чего в блок 20 памяти вводится напряжение, равное значению частоты 0)2. резонансного пика. Этот же импульсный сигнал с выхода коммутатора 22 через элемент 29 задержки поступает на единичный вход триггера 27, устанавливая его в единицу. При этом появляется сигнал на четвертом выходе дешифратора 23, а частота генератора 2 начинает изменяться в сторону ее уменьшения со скоростью va.

При совпадении текущей частоты w(t) возбуждения вибростенда 5 с резонансной частотой он элемента 6 конструкции разность фаз сигналов на входах фазового детектора 11 равна я/2, а сигнал на выходе детектора 11 равен нулю. На выходе нуль- органа 13 появляется импульсный сигнал, который через коммутатор 22 поступает на управляющий вход ключа 18 и входы Чтение блоков 19, 20, 21 памяти непосредственно, а через элемент 31 задержки на нулевые входы триггеров 24, 25, 26, 27, устанавливая их в ноль, а устройство в исходное состояние. Сигналы с выходов блока 19 памяти и ключа 18 поступают на входы блока 32 умножения и входы сумматора 36. Сигналы с выходов блоков 20 и 21 памяти поступают на входы блока 33 умножения и входы сумматора 35. Сигналы с выходов блоков 19 и 21 памяти поступают на суммирующий и вычитающий входы сумматора 38 соответственно. Сигналы с выходов ключа 18 и блока 20 памяти поступают на суммирующий и вычитающий входы сумматора 39 соответственно. Сигналы с выходов блоков 32 и 33 умножения поступают на суммирующий и вычитающий входы сумматора 34, выходной сигнал которого поступает на вход Делимое блока 40 деления. На вход Делитель блока 40 поступает сигнал с выхода сумматора 37. на суммирующий и вычитающий входы которого поступают сигналы с выходов сумматоров 35 и 36 соответственно. Выходные сигналы сумматоров 38 и 39 поступают на входы блока 42 сравнения и входы второго нуль-органа 43. Сигналы с выходов блока 40 деления, блока 42 5 сравнения и нуль-органа 43 поступают на первый, второй и третий входы соответственно регистратора 41.

Наличие и величина сигнала на первом входе соответствуют величине резонансной

0 частоты элемента конструкции, наличие сигнала на втором входе соответствует выполнению условия Ai Да (крутизна доре- зонансной ветви больше крутизны зарезонансной ветви), наличие сигнала на

5 третьем входе соответствует условию AI Дз (крутизна дорезонансной и зарезонансной ветвей равны).

Преимущество предложенного способа определения резонансной частоты в ззви0 симости от скоростей развертки по частотному диапазону за счет исключения усилителей с зависимыми от скоростей развертки коэффициентами передачи при одновременном определении асимметрии

5 резонансной ветви, большей, меньшей или равной крутизне зарезонансной ветви резонансной характеристики.

Блок 1 управления разверткой частоты работает следующим образом.

0Частоты генерации импульсных генераторов 45 и 46 подбираются близкими с таким расчетом, чтобы частота биений, которая определяет период следования сформированного линейно изменяющегося

5 напряжения, была на несколько порядков ниже, а период следования линейно изменяющегося напряжения был таким, чтобы перекрывался диапазон частот воспроизводимых вибраций. Для получения выходного

0 сигнала с повышающейся частотой схему настраивают так, чтобы частота генератора 46 была выше частоты генератора 45. В исходном состоянии триггер 49 установлен в единицу.

5При поступлении сигнала на вход 65 на

выходах генераторов 45, 46 формируются импульсы, Выходные импульсы генераторов 45 и 46 управляют состоянием триггера 47, на одном выходе которого образуется

0 последовательность прямоугольных импульсов линейно нарастающей длительности, а на другом - последовательность импульсов линейно убывающей длительности. При этом триггер 48 устанавливается в

5 нулевое состояние, ключ 50 замыкается, ключ 51 разомкнут. Через замкнутый ключ 50 импульсы линейно нарастающей длительности через резистор 53 поступают на конденсатор 54, в результате чего при разомкнутом ключе 52 (так как триггер 49 установлен в ноль) на выходе 69 формируется нарастающий участок выходного напряжения.

При появлении сигнала на втором уп- равляющем входе 66 триггер 48 устанавливается в единичное состояние, при этом ключ 51 замыкается, а ключ 50 размыкается. Зарядный резистор 53 и накопительный конденсатор 54 оказываются подключенными к прямому входу триггера 47, на котором формируется последовательность импульсов линейно убывающей длительности, а на выходе 69 формируется линейно падающий участок выходного напряжения.

При появлении сигнала на третьем управляющем входе 67 триггер 48 устанавливается в нулевое состояние, при этом высокий потенциал присутствует на управляющем входе элемента ИЛИ 55 и на выходе 69 вновь формируется нарастающий участок выходного напряжения. Одновременно сигнал, поступающий на вход 67, производит запуск одновибратора 64, на выходе которого формируется импульс, поступающий через элемент ИЛИ 57 на управляющий вход ключа 52. Таким образом, напряжение на конденсаторе 54 устанавливается равным нулю. Импульсный сигнал с выхода одновибратора 64, поступающий на управляющий вход ключа 60, замыкает ключ 60. При этом конденсатор 61 через токоста- билизирующий двухполюсник 63 и ключ 60 от источника питания Е заряжается на величину Д U напряжения (ключ 59 разомкнут, так как триггер 49 установлен в нулевое состояние). Напряжение A U через согласующий усилитель 62 поступает на управляющий вход генератора 46 и его частота возрастает, что приводит к возрастанию частоты биений и крутизны линейно изменяющегося выходного напряжения.

При появлении сигнала на управляющем входе 68 триггер 48 снова устанавливается в единичное состояние, ключ 51 замыкается, а ключ 50 размыкается, Таким образом, на выходе генератора 58 ступенчатого напряжения формируется ступенчато возрастающее напряжение, а на выходе 69 - треугольное напряжение, имеющие разную крутизну.

При появлении сигнала на входе 73 Сброс триггер 49 устанавливается в единичное состояние, ключи 52 и 59 .замыкаются, конденсаторы 54 и 62 разряжаются через ключи 52 и 59 соответственно, а генераторы 45 и 46 выключаются. Устройство устанавливается в исходное состояние.

По сравнению с прототипом предложенный способ определения резонансной

частоты элементов конструкции имеет преимущество: более широкую область применения за счет упрощения реализации способа из-за отсутствия необходимости

применения усилителей с регулируемыми коэффициентами усиления, определяемыми величинами скоростей развертки частоты, и за счет определения характера асимметрии линейной резонансной характеристики.

0 Формула и зобретени я

Устройство для измерения резонансной частоты элементов конструкций, содержащее последовательно соединенные блок управления разверткой частоты, задающий

5 генератор, регулятор амплитуды, усилитель мощности и вибростенд, предназначенный для установки испытуемого объекта, первый вибропреобразователь, установленный на подвижной части вибростенда, второй виб0 ропреобразователь, предназначенный для установки на испытуемый объект, первый и второй согласующие усилители, входы которых соединены с соответствующими вибропреобразователями, фазовый детектор,

5 входы которого соединены с выходами согласующих усилителей, блок обратной связи, вход которого соединен с выходом первого согласующего усилителя, а выход - с управляющим входом регулятора амплиту0 ды, преобразователь частота-напряжение, вход которого соединен с выходом второго согласующего усилителя, последовательно соединенные нуль-орган, вход которого соединен с выходом фазового детектора, и

5 коммутатор, дешифратор, выходы которого соединены с соответствующими управляющими входами блока управления разверткой частоты и коммутатора, первый и второй триггеры, единичные выходы которых сое0 динены с соответствующими входами дешифратора, ключ, вход которого соединен с выходом преобразователя частота-напряжение , а управляющий вход - с первым выходом коммутатора, первый элемент

5 за/ ержки, соединяющий первый выход коммутатора с единичным входом второго триггер), второй элемент задержки и регистратор, отличаю ще е с я тем. что, с це/ью повышения точности расширения

0 функциональных возможностей за счет оценки симметричности характеристик, оно снабжено третьим и четвертым триггерами, единичные выходы которых соединены с со- ответств ющими входами дешифратора,

5 единичные входы через второй и третий элементы задержки - с вторым и третьим входами дешифратора, а нулевые входы - с нулевыми входами первого и второго триггеров и через четвертый элемент задержки - с четвертым выходом дешифратора, вторым, третьим и четвертым ключами, входы которых соединены с выходом преобразователя частота-напряжение, а управляющие входы - с соответствующими выходами коммутатора, тремя блоками памяти, входы которых соединены с выходами соответствующих ключей, а входы Запись - с соответствующими выходами коммутатора, первым блоком умножения, входы которого соединены с выходами первого блока памяти и четвертого ключа, с вторым блоком умножения, входы которого соединены с выходами второго и четвертого блоков памяти, первым сумматором, входы которого соединены с выходами первого и второго блоков умножения, вторым сумматором, входы которого соединены с выходами второго и третьего блоков памяти, третьим сумматором, входы которого соединены с

входами первого блока умножения, четвертым сумматором, входы которого соединены с выходами второго и третьего сумматоров, пятым сумматором, входы которого соединены с выходами первого и третьего блоков памяти, шестым сумматором, входы которого соединены с выходами второго блока памяти и четвертого ключа, делителем, вход Делимое которого соединен с выходом первого блока памяти, а вход Делитель - с выходом четвертого блока памяти, а выход - с первым входом регистратора, блоком сравнения, входы которого соединены с выходами пятого и

шестого сумматоров, а выход - к второму входу регистратора, и вторым нуль-органом, входы которого соединены с входами блока сравнения, а выход - с третьим входом регистратора.

Изобретение относится к области исследования динамических свойств элементов конструкций и предназначено для исследования частотных характеристик. Цель изобретения - повышение точности и расширение функциональных возможностей за счет оценки симметричности характеристик. Устройство реализует способ, по которому фиксируют смещенные резонансные частоты ш и «УЗ при увеличении и уменьшении частоты со скоростью vi и ftfc, UM при скорости V2, резонансную частоту соь определяют по формуле (Ш С04 - Шг Gu)/( + ОМ) - (W2 + Уз) . а симметричность - по разностям (ш - од) и (вдз - ад). Для реализации способа устройство включает в себя вибростенд и блоки, реализующие необходимые соотношения. 2 ил.

Л

5Ь

Г7Ј

65

66 67 6873 фиг1

| Устройство для обнаружения резонансной частоты объекта | 1985 |

|

SU1254310A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Способ определения резонансной частоты элементов конструкции | 1987 |

|

SU1633294A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-08-07—Публикация

1989-12-05—Подача