i Изобретение относится к электросвязи и может быть использовано в системах телемеханики для передачи и приема данных.

Цель изобретения - упрощение системы и повышение помехоустойчивости.

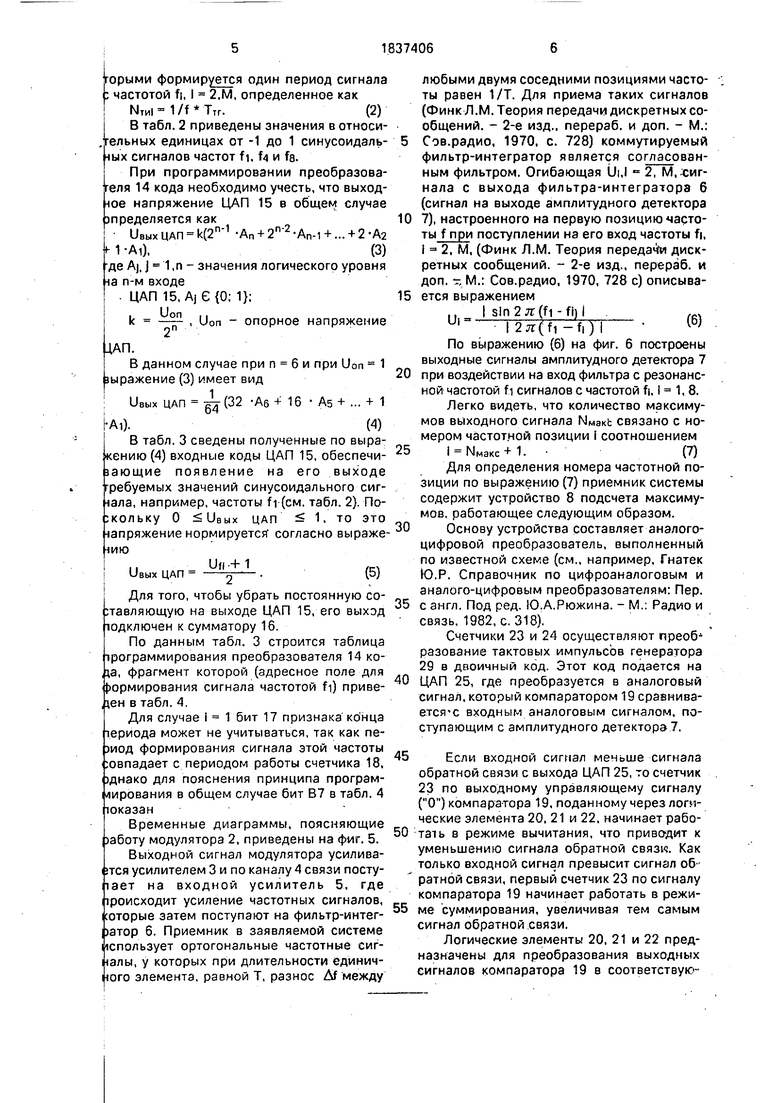

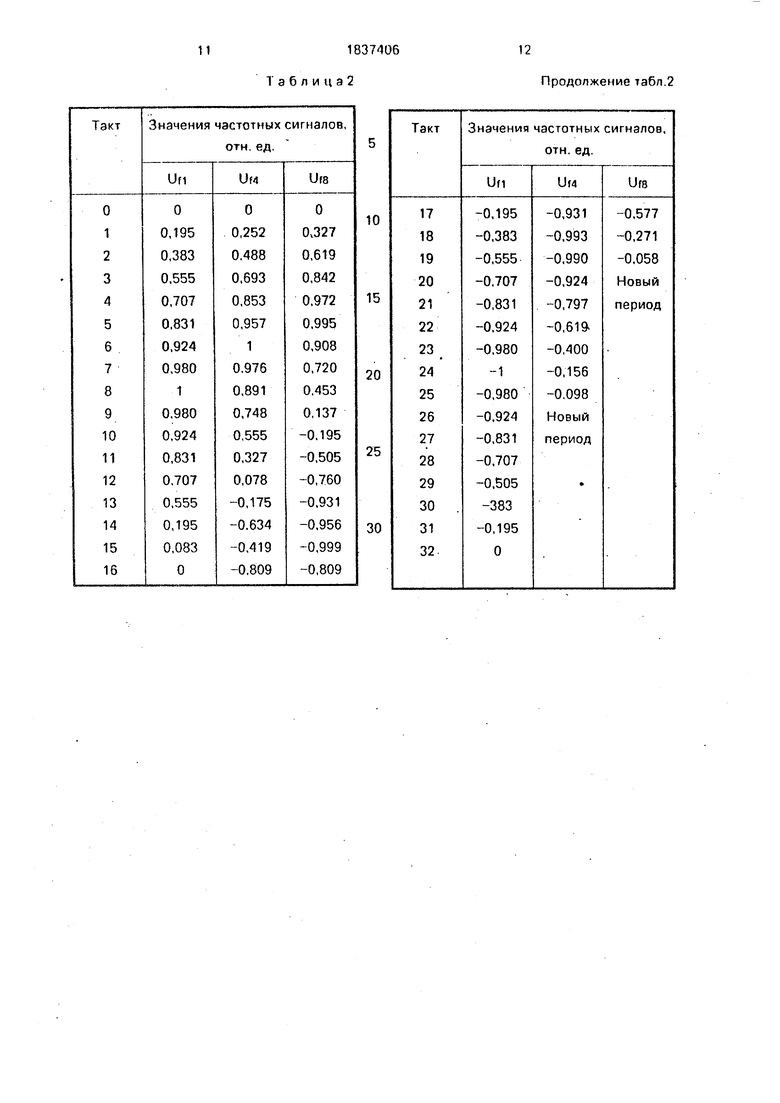

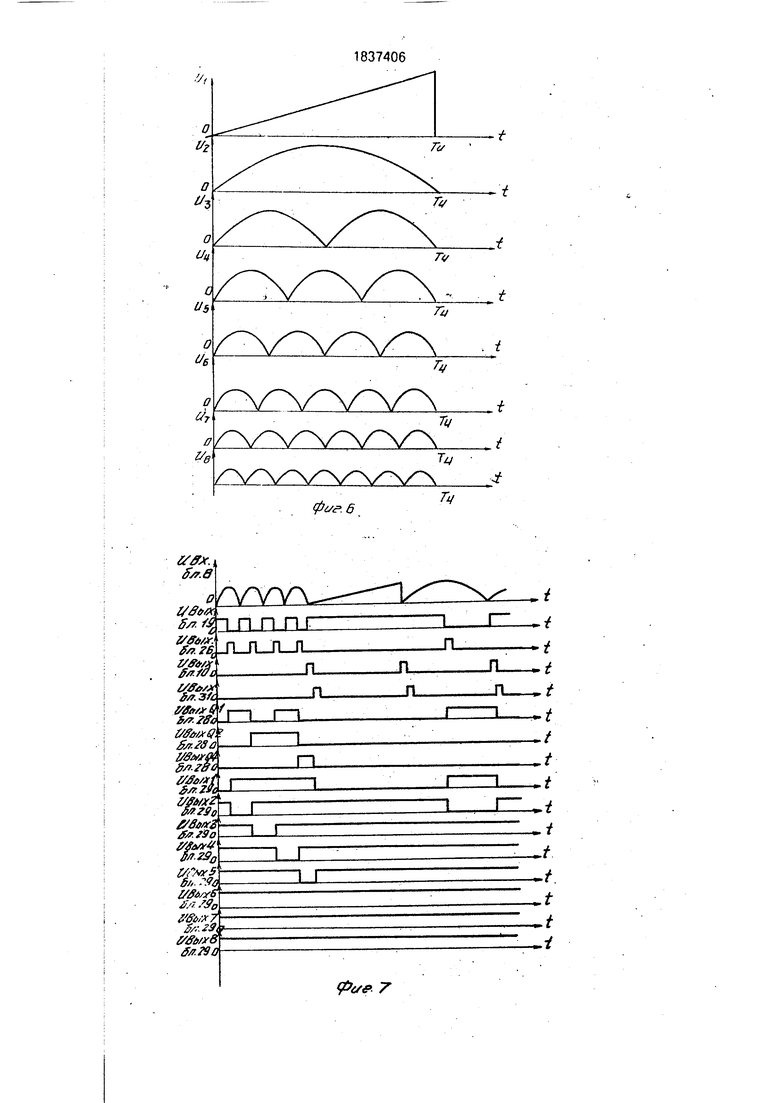

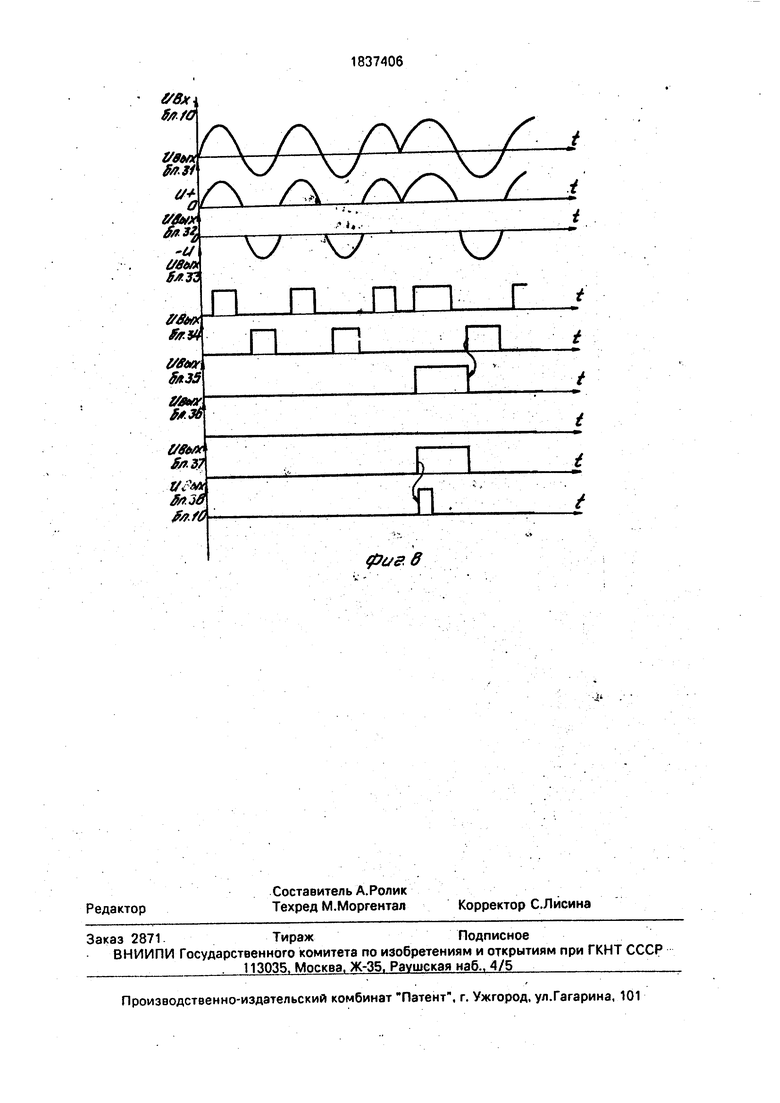

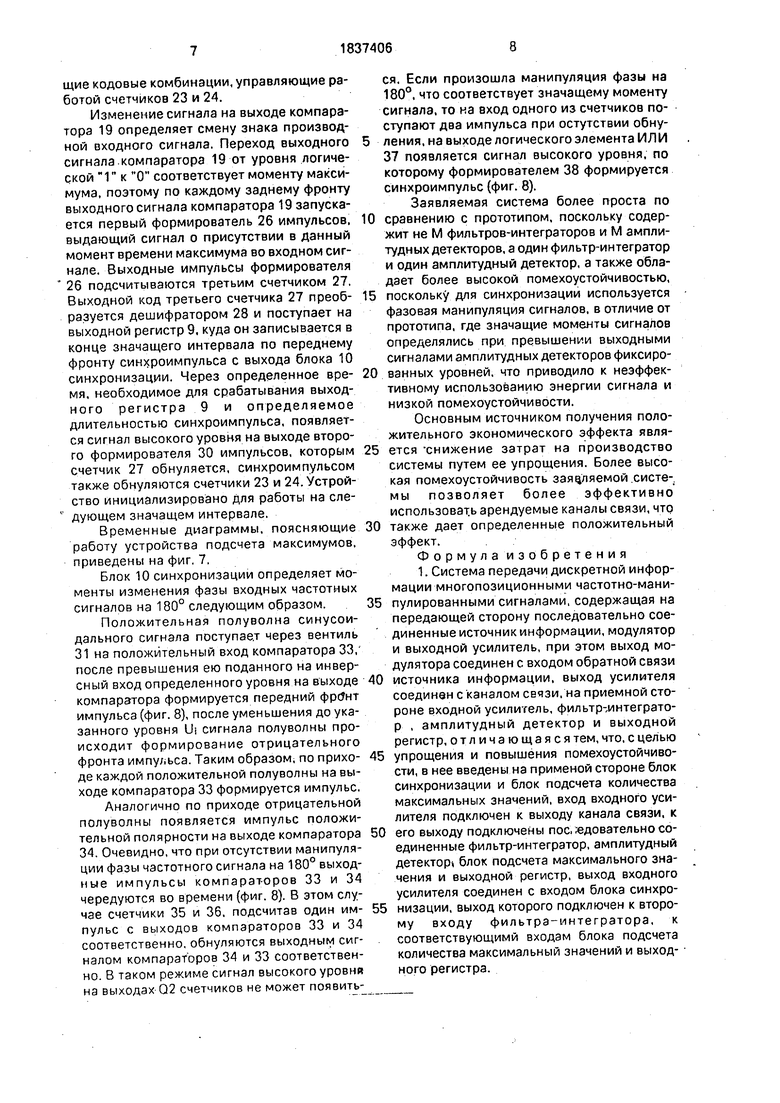

На фиг. 1 приведена структурная схема (истемы; на фиг. 2 - функциональная схема модулятора; на фиг. 3 - функциональная (хема устройства подсчета максимумов; на оиг. 4 - функциональная схема блока синхронизации; на фиг. 5 приведены временные диаграммы, поясняющие работу модулятора; на фиг. 6 - графики выходных напряжений амплитудного детектора; на фиг. 6 проиллюстрирована работа устройства подсчета максимумов; на фиг. 8 временными диаграммами пояснена работа блока синхронизации.

Система содержит на передающей стороне источник 1 информации, модулятор 2. выходной усилитель 3, канал 4 связи, на приемной стороне входной усилитель 5,

фильтр-интегратор 6, амплитудный детектор 7. устройство 8 подсчета максимумов, выходной регистр 9 и блок 10 синхронизации.

Модулятор 2 (фиг. 2) содержит элемент И It. счетчик 12, регистр 13, преобразователь 14 кода, цифроаналоговый преобразователь (ЦАП) 15. сумматор 16. тактовый генератор 17. счетчик 38.

Устройство 8 подсчета максимумов (фиг. 3) содержит компаратор 19, элемент И-НЕ 20, инвертор 21, элемент НЕ 22, счетчики 23 и 24, ЦАП 25, формирователи 26 и 30 импуль- сов, счетчик 27. дешифратор 28, тактовый генератор 29.

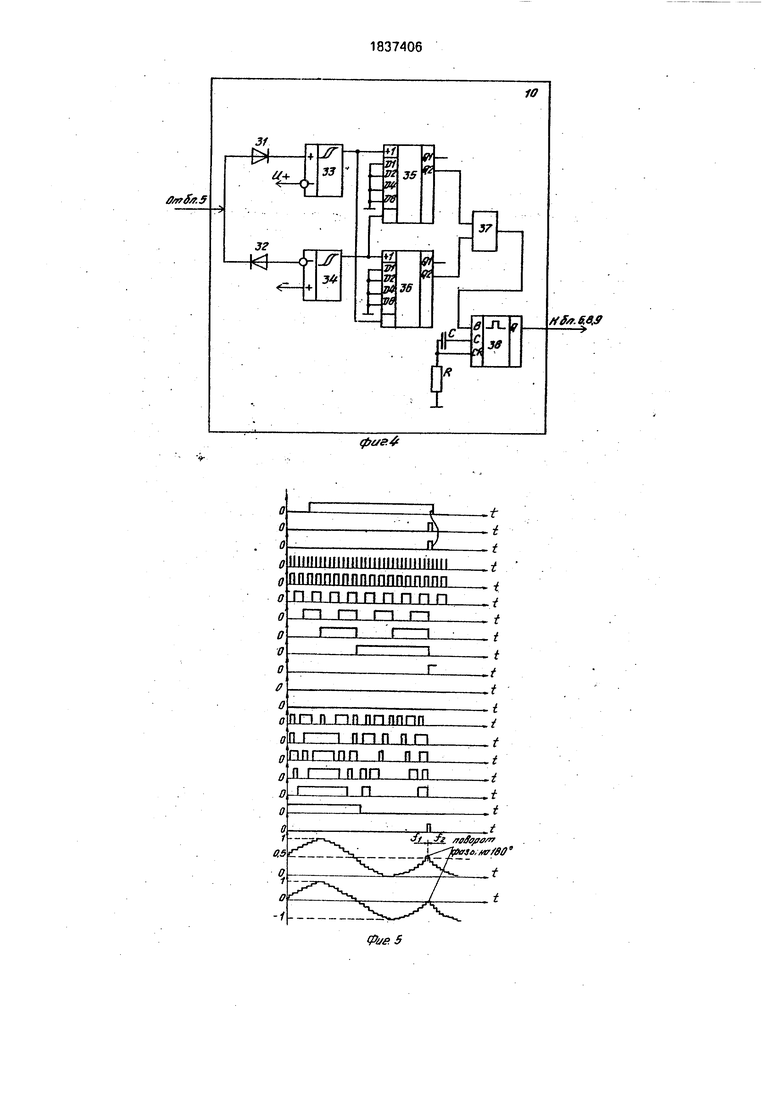

Блок 10 синхронизации (фиг. 4) содержит два вентиля 31 и 32, два компаратора 33 и 34, два счетчика 35 и 36, элемент ИЛИ 37. формирователь 38.

Система работает следующим образом.

Предлагаемая информация от источника, информации поступает на модулятор 2

00

со

2

О

Оч

в параллельном М-рэзрядном двоичном коде и по синхроимпульсу записывается в регистр 13. В модуляторе 2 каждой входной М-разрядной кодовой комбинации ставится в соответствие выходной сигнал определенной частоты fi, I 1-М, где М - 2т, следующим образом. Очередная передаваемая кодовая комбинаци, записанная в регистре 13, поступает на адресные входы преобразователя 14 кода и определяет номер соответствующей частоты,которую необходимо передать в канал связи. Счетчик 18с входной разрядностью 1 по тактовым импульсам генератора 17 осуществляет опрос адресного поля, определенного выходным кодом регистра 13, на выходе преобразователя 14 кода формируется изменяющийся по тактовым импульсам генератора 17 код, который после преобразования в аналоговую форму ЦАП 15 и вычитания постоянной составляющей сумматором 16 представляет собой синусоидальный сигнал требуемой частоты.

Полный период каждой частоты должен быть сформирован на один цикл опроса адресных входов преобразователя 14 кода счетчиком 18, поэтому ввиду того, что частота тактового генератора 17 постоянна,а периоды разных частот различны, в модуляторе введена связь выходов преобразователя 14 кода с входами предварительной установки счетчика 18, управляющая длительностью цикла работы счетчика следующим образом.

При появлении на выходе преобразователя 14 кода кодовой комбинации, соответствующейпоследнемутактуаппроксимации периода любой из частот, одновременно (и только в этом случаев) появляется сигнал высокого уровня на (п + 1)-м выходе преобразователя 14 кода - признак завершения формирования полного периода частоты. Этим сигналом (по его переднему фронту) счетчик 18 обнуляется (возврат в начало периода). Если синхроимпульс отсутствует (необходимо продолжать формировать сигнал этой же частоты), то счетчик 18 снова начинает опрашивать то же адресное поле (определенное входным кодом сдвигового регистра 13), что и в предыдущем цикле Поскольку значения синусоидального сигнала в начале и в конце периода равны (целесообразно принять нулевое значение), то при этом никаких скачков напряжения на выходе ЦАП нет. Если же в описанный момент синхроимпульс присутствовал на первом входе логического элемента И 11, то не выходе регистра 13 появляется следующая передаваемая кодовая комбинация, адресное поле преобразователя 14 кода, опрашиваемое счетчиком

0

5

0

5

0

5

0

5

0

5

18, изменяется соответствующим образом. Начинается формирование периода определенной выходным кодом регистра 13 новой частоты. В конце периода снова появляется сигнал высокого уровня на (п+1)-м выходе преобразователя 14 кода.

Синхронизация сигналов на входах элементов И 11 осуществляется следующим образом. В конце тактового интервала источник 1 информации после установления на шине данных (информационные входы регистра 13) нового слова выдает синхроимпульс (первый вход элемента И 11) и не снимает его до тех пор, пока не будет закончено формирование периода ранее передаваемой частоты. По окончании формирования импульс с (п+1)-го выхода преобразователя 14 кода поступает на второй вход элемента И 11. По выходному импульсу элемента И 11 новая кодовая комбинация записывается в регистр 13 и одновременно источником информации (через вход обратной связи) снимается синхроимпульс с нулевого входа элемента И 11.

Счетчик 12, работающий в режиме счетного триггера, служит для внесения в передаваемые сигналы информации об их. значащих моментах. Для этого информация в преобразователе 14 кода записана таким образом, что при наличии на его адресном входе, подключенном к выходу счетчика 12, сигнала низкого уровня с начала значающе- го интервала происходит формирование выходного кода, соответствующего сигнала sinWt, где W определяется частотой такто, ... 2 п fr

вого генератора fr, как W ;- , где t 21

разрядность счетчика 12, а при наличии сигнала высокого уровня с начала значающего интервала формируется код, соответствующий сигналу sin(Wt +я).

Конкретно преобразователь 14 кода может быть запрограммирован, напримео, следующим образом.

Пусть при М 8, m 3, n 6, 100 Гц, где Л f - разнесение между соседними частотными позициями, используется пятиразрядный счетчик 12 (t 5). При этом значения формируемых частот, их периоды приведены в табл. 1. При этом формировании сигнала с частотой fi используются все 32 адреса с выхода счетчика 12, для которого в этом случае необходима тактовая частота генератора 17.

fw fi 32 3200 (Гц)(1)

с периодом

Ттг 1/ттг 3,125 105(с).

В табл. 1 также приведено количество NTHI тактовых импульсов генератора 17, коСерыми формируется один период сигнала с частотой fi, I 2,М, определенное как

Мти - 1 Л Ттг.(2)

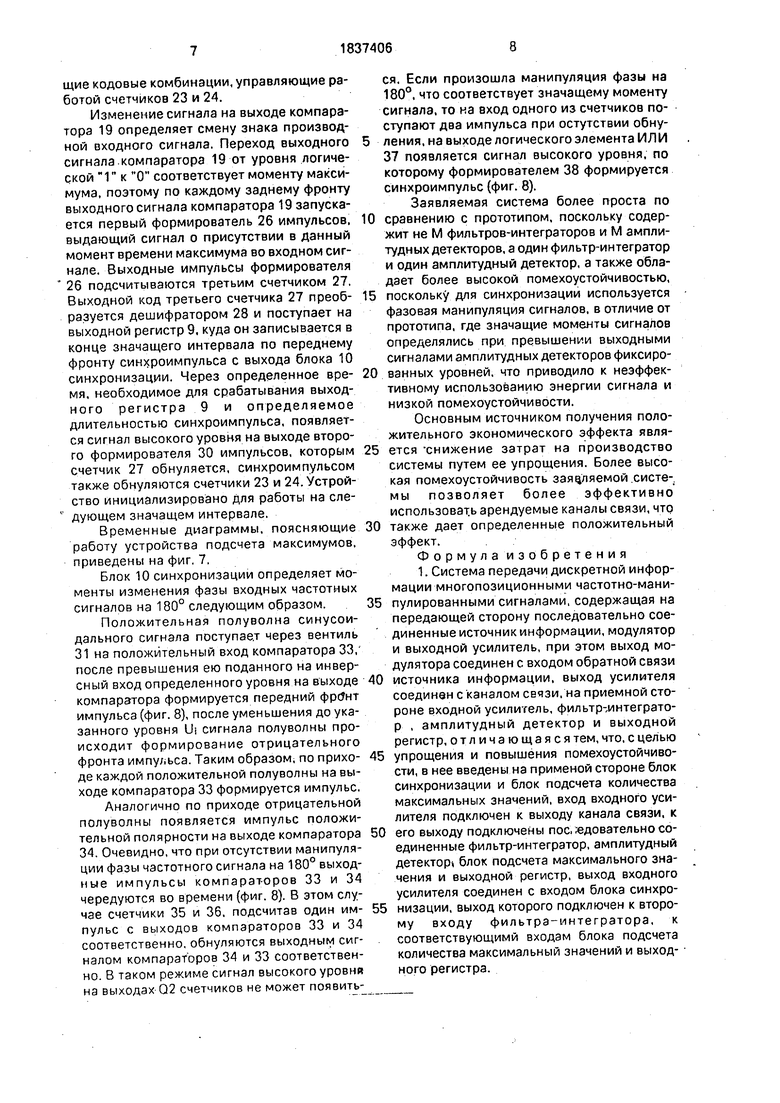

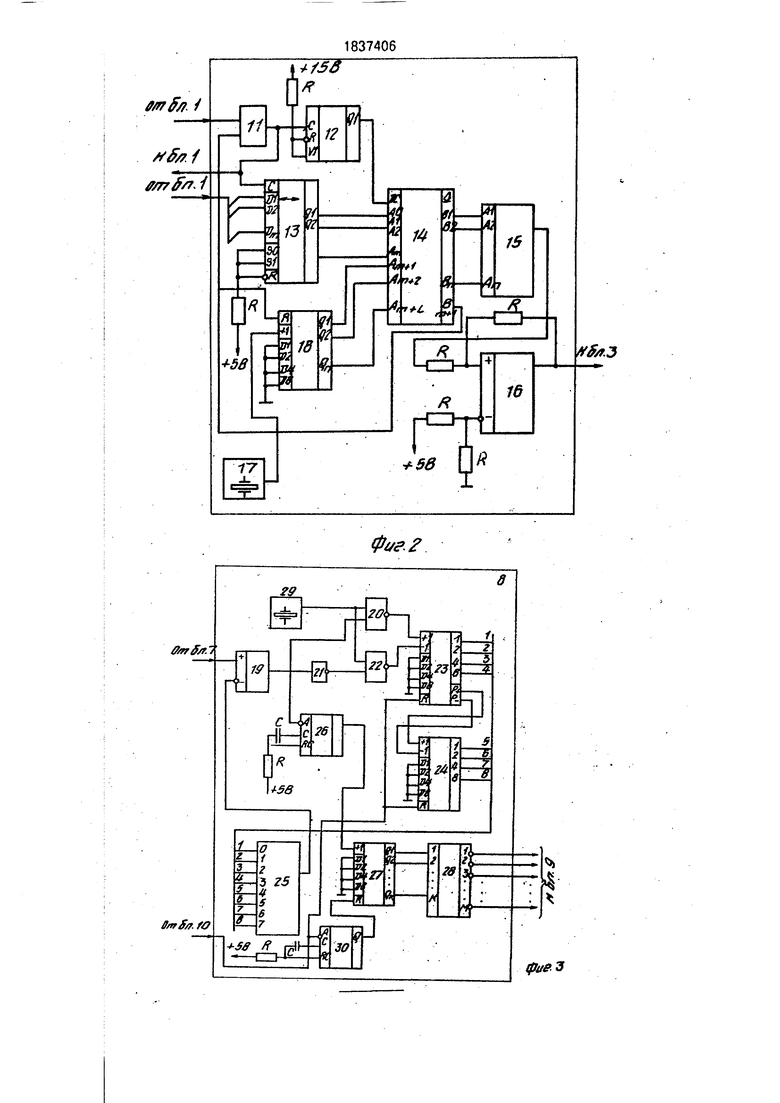

i В табл. 2 приведены значения в относительных единицах от -1 до 1 синусоидаль- шх сигналов частот fi. и fa. i При программировании преобразователя 14 кода необходимо учесть, что выход- -юе напряжение ЦАП 15 в общем случае

эпределяется как

п-1

in-2.

1 -АО,

Увых ЦАП k( -An + 2n An-1 +... + 2 -А2

(3)

де AJ, j 1 ,п - значения логического уровня на n-м входе

ЦАП 15,Aje{0; 1};

оп Don - опорное напряжение

ЬА

2п

П.

В данном случае при п 6 и при Uon выражение (3) имеет вид 1

Увых ЦАП 5:4 (32 -Аб + 16

As + ... + 1

ut

rAi).(4)

В табл. 3 сведены полученные по выра- кению (4) входные коды ЦАП 15, обеспечи- зающие появление на его выходе требуемых значений синусоидального сигала, например, частоты fi (см. табл. 2}. По- :кольку 0 Увых ЦАП 1. то это спряжение нормируется1 согласно выраже1ИЮ

Ufi + 1

Увых ЦАП

(5)

Для того, чтобы убрать постоянную составляющую на выходе ЦАП 15, его выход подключен к сумматору 16.

По данным табл. 3 строится таблица трограммирования преобразователя 14 кода, фрагмент которой (адресное поле для формирования сигнала частотой fi) приведен в табл. 4.

Для случае i 1 бит 17 признака ко нца периода может не учитываться, так как пе- )иод формирования сигнала этой частоты совпадает с периодом работы счетчика 18. щнако для пояснения принципа программирования в общем случае бит В7 в табл. 4 юказан

Временные диаграммы, поясняющие )аботу модулятора 2, приведены на фиг. 5.

Выходной сигнал модулятора усилива- i тся усилителем 3 и по каналу 4 связи посту- пает на входной усилитель 5. где происходит усиление частотных сигналов, соторые затем поступают на фильтр-интег- атор 6. Приемник в заявляемой системе использует ортогональные частотные сигналы, у которых при длительности единичного элемента, равной Т, разнос Af между

любыми двумя соседними позициями частоты равен 1/Т. Для приема таких сигналов (Финк Л .М. Теория передачи дискретных сообщений. - 2-е изд., перераб. и доп. - М.:

5 Сов.радио, 1970, с. 728) коммутируемый фильтр-интегратор является согласованным фильтром. Огибающая Ui,l 2, М,-сигнала с выхода фильтра-интегратора 6 (сигнал на выходе амплитудного детектора

10 7), настроенного на первую позицию часто- ты f при поступлении на его вход частоты fi, I 2, М, (Финк Л.М. Теория передач дискретных сообщений. - 2-е изд., перераб. и доп. т, М.: Сов.радио, 1970, 728 с) описыва15 ется выражением

I з)п2л:(т1-Л)|

Ur

(6)

I23r(fi-fi)l По выражению (6) на фиг. 6 построены выходные сигналы амплитудного детектора 7

20 при воздействии на вход фильтра с резонансной частотой fi сигналов с частотой fi, 1 1,8. Легко видеть, что количество максимумов выходного сигнала МмакЬ связано с номером частотной позиции i соотношением

25 1 Ммакс+1. (7)

Для определения номера частотной позиции по выражению (7) приемник системы содержит устройство 8 подсчета максимумов, работающее следующим образом.

30 Основу устройства составляет аналого- цифровой преобразователь, выполненный по известной схеме (см., например, Гнатек Ю.Р. Справочник по цифроаналоговым и аналого-цифровым преобразователям: Пер.

35 с англ. Под ред. Ю.А.Рюжина. - М.: Радио и связь, 1982, с. 318).

Счетчики 23 и 24 осуществляют преоб4 разование тактовых импульсов генератора 29 в двоичный код. Этот код подается на

40 ЦАП 25, где преобразуется в аналоговый сигнал, который компаратором 19 сравнива- ется с входным аналоговым сигналом, поступающим с амплитудного детектора.

45 Если входной сигнал меньше сигнала обратной связи с выхода ЦАП 25, то счетчик 23 по выходному управляющему сигналу (О) компаратора 19, поданному через лот- ческие элемента 20, 21 и 22, начинает рабо50 тать в режиме вычитания, что приводит к уменьшению сигнала обратной связк. Как только входной сигнал превысит сигнал обратной связи, первый счетчик 23 по сигналу компаратора 19 начинает работать в режи55 ме суммирования, увеличивая тем самым сигнал обратной связи.

Логические элементы 20, 21 и 22 предназначены для преобразования выходных сигналов компаратора 19 в соответствующие кодовые комбинации, управляющие работой счетчиков 23 и 24.

Изменение сигнала на выходе компаратора 19 определяет смену знака производной входного сигнала. Переход выходного сигнала компаратора 19 от уровня логической 1 к О соответствует моменту максимума, поэтому по каждому заднему фронту выходного сигнала компаратора 19 запускается первый формирователь 26 импульсов, выдающий сигнал о присутствии в данный момент времени максимума во входном сигнале. Выходные импульсы формирователя 26 подсчитываются третьим счетчиком 27. Выходной код третьего счетчика 27 преобразуется дешифратором 28 и поступает на выходной регистр 9, куда он записывается в конце значащего интервала по переднему фронту синхроимпульса с выхода блока 10 синхронизации. Через определенное время, необходимое для срабатывания выходного регистра 9 и определяемое длительностью синхроимпульса, появляется сигнал высокого уровня на выходе второго формирователя 30 импульсов, которым счетчик 27 обнуляется, синхроимпульсом также обнуляются счетчики 23 и 24. Устройство инициализировано для работы на следующем значащем интервале.

Временные диаграммы, поясняющие работу устройства подсчета максимумов, приведены на фиг. 7.

Блок 10 синхронизации определяет моменты изменения фазы входных частотных сигналов на 180° следующим образом.

Положительная полуволна синусоидального сигнала поступает через вентиль 31 на положительный вход компаратора 33, после превышения ею поданного на инверсный вход определенного уровня на выходе компаратора формируется передний импульса (фиг. 8), после уменьшения до указанного уровня Uj сигнала полуволны происходит формирование отрицательного фронта импульса. Таким образом, по приходе каждой положительной полуволны на выходе компаратора 33 формируется импульс. Аналогично по приходе отрицательной полуволны появляется импульс положительной полярности на выходе компаратора 34. Очевидно, что при отсутствии манипуляции фазы частотного сигнала на 180° выход- ные импульсы компараторов 33 и 34 чередуются во времени (фиг. 8). В этом случае счетчики 35 и 36. подсчитав один импульс с выходов компараторов 33 и 34 соответственно, обнуляются выходным сигналом компараторов 34 и 33 соответственно. В таком режиме сигнал высокого уровни на выходах Q2 счетчиков не может появиться. Если произошла манипуляция фазы на 180°, что соответствует значащему моменту сигнала, то на вход одного из счетчиков поступают два импульса при остутствии обнуления, на выходе логического элемента ИЛ И 37 появляется сигнал высокого уровня, по которому формирователем 38 формируется синхроимпульс (фиг. 8).

Заявляемая система более проста по

сравнению с прототипом, поскольку содержит не М фильтров-интеграторов и М амплитудных детекторов, а один фильтр-интегратор и один амплитудный детектор, а также обладает более высокой помехоустойчивостью,

поскольку для синхронизации используется фазовая манипуляция сигналов, в отличие от прототипа, где значащие моменты сигналов определялись при превышении выходными сигналами амплитудных детекторов фиксированных уровней, что приводило к неэффективному использованию энергии сигнала и низкой помехоустойчивости.

Основным источником получения положительного экономического эффекта является снижение затрат на производство системы путем ее упрощения. Более высокая помехоустойчивость заявляемой системы позволяет более эффективно использовать арендуемые каналы связи, что

также дает определенные положительный эффект.

Формула изобретения 1. Система передачи дискретной информации многопозиционными частотно-манипулированными сигналами, содержащая на передающей сторону последовательно соединенные источник информации, модулятор и выходной усилитель, при этом выход модулятора соединен с входом обратной связи

источника информации, выход усилителя соединен с каналом связи, на приемной стороне входной усилитель, фильтр-интеграто- р , амплитудный детектор и выходной регистр, отличающаяся тем, что, с целью

упрощения и повышения помехоустойчивости, в нее введены на применой стороне блок синхронизации и блок подсчета количества максимальных значений, вход входного усилителя подключен к выходу канала связи, к

его выходу подключены пос,«довательно соединенные фильтр-интегратор, амплитудный детектор блок подсчета максимального значения и выходной регистр, выход входного усилителя соединен с входом блока синхронизации, выход которого подключен к второму входу фильтра-интегратора, к соответствующими входам блока подсчета количества максимальный значений и выход- ного регистра.

2. Система поп. 1,отличающаяся ем. что модулятор содержит элемент И, два :четчика, регистр, преобразователь кода, дифроаналоговый преобразователь, сумма- гор, тактовый генератор, первый вход эле- лента И соединен с выходом :инхронизации источника информации, вы- сод элемента И подключен к входу обратной :вязи источника информации и к тактовому зходу первого счетчика, информационными зходами модулятора являются информационные входы регистра, к тактовому входу (второго подсоединен выход элемента И, саждый из М выходов регистра подключен к соответствующему входу преобразователя сода, к входам которого также подключены }ыходы второго счетчика, выходы преобразователя кода подключены к входам цифро- налогового преобразователя, выход оторого подключен к первому входу сумма- ора, второй вход которого является входом апряжения постоянного уровня, выход умматора является выходом модулятора, ыход тактового генератора подключен к ;четному входу второго счетчика, выходы оторого соединены с соответствующими зходами преобразователя кода, М+1-й выход которого соединен с входом обнуления второго счетчика и с вторым входом элемента И.

3. Система по п. 1,отличающаяся тем, что блок подсчета максимального значения сигнала содержит компаратор, инвертор, два элемента И-НЕ, три Счетчика, цифроаналоговый преобразователь, два формирователя импульсов, дешифратор и тактовый генератор, причем входом блока является первый вход компаратора,Овыход которого подключен к первому входу первого элемента И-НЕ, и через инвертор - к первому входу второго элемента И-НЕ, выход которых подключен к счетным входам первого счетчика, выход переноса которого соединен с соответстсующими счетными входами второго счетчика, а разрядные выходы первого и второго счетчиков подключены к входам цифроаналогового преобразователя, выход которого подключен к второму входу компаратора, выход которого подключен через первый формирователь импульсов к счетному входу третьего счетчика, разрядные выходы которого соединены ,с информационными входами дешифратора, выходы которого являются выходами блока, к вторым входам элементов И-НЕ подключен вход генератора, входы обнуления всех счетчиков соединены через второй формирователь импульсов с входом синхронизации блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2003 |

|

RU2246799C1 |

| СИСТЕМА РАДИОВЕЩАНИЯ | 2008 |

|

RU2383103C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

| Цифровой телевизионный приемник | 1983 |

|

SU1321384A3 |

| СИСТЕМА ЦИФРОВОГО ТЕЛЕВИДЕНИЯ | 2001 |

|

RU2208917C2 |

| СИСТЕМА РАДИОВЕЩАНИЯ | 2011 |

|

RU2479926C1 |

| Детектор @ -зубца электрокардиосигнала | 1984 |

|

SU1260004A1 |

| ЦИФРОВАЯ СИСТЕМА РАДИОВЕЩАНИЯ | 2011 |

|

RU2457620C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ ВЫСОКОЙ ЧЕТКОСТИ | 2000 |

|

RU2194370C2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

Изобретение относится к электросвязи и может быть и использовано в системах телемеханики для передачи и приема данных. Цель изобретения - упрощение системы и повышение ее помехоустойчивости. Цель достигается тем, что при использовании любого числа М передаваемых частот приемная сторона системы содержит только один фильтр- интегратор и один амплитудный детектор, а также тем, что регистрирующий импульс выдается в моменты, соответствующие значаю- щим моментам передаваемых сигналов, для чего в систему введены устройство подсчета максимумов и блок синхронизации. 2 з.п. ф- лы, 4 табл.. 8 ил.

Т а б л и ц а 1

Т а б л и ц а 2

12

Продолжение табл.2

о

о

0,195 0,383 555 0,707 0,831 0,924 0,980 1

0,980 0,924 0,831 0,707 0,555 0,383 0,195 О

-0,195 -0,383 -0,555 -0,707 -0,831 -0,924 -0,980 -1

-0,980 -0,924 -0,831 -0,707 -0,555 -0,383 -0,195

0,5

0,598

0,692

0,777

0,853

0,915

0,962

0,990

1

0,990

0,962

0,915

0,853

0,777

0,692

0,598

0,5

0,403

0,309

0,223

0,146

0,0845

0,0380

0,01

О

0,01

0,038

0,0845

0,146

0,223

0,309

0,403

Т аблица 3

о о о 1 1 1 1 1 1 1 1 1 1 1 о о о 1 1 о о о о о о о о о о о

о

о

1

о

о

1

1

1

1

1

1

о

о

1

о

о

1

о

1

1

о

о

о

о

о

о

о

1

1

о

1

о 1 1

о 1 о 1 1 1 1 1 о 1 о 1 1 о о о о о 1 о о о о о 1 о о о о

1 о о 1 о 1 1 1 о о 1 о о о 1 о о 1 1 1

о

1

о

1

1

1

о

о

1

о

о

1

1

1

о

1

о

о

1

о

1

1

о

1

о

1

о

1

1

о

1

о

Т аблица А

рыг.1

ff/rrff/r.t

0/aSff fO

Фие.

фиеЗ

9 лф

У/

QOt ACSl

фиг 8

| Устройство для передачи и приема частотной информации | 1976 |

|

SU650089A1 |

| кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для передачи дискретных сигналов | 1974 |

|

SU490153A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1993-08-30—Публикация

1991-05-27—Подача