Известны счетчики импульсов на фазоимпульсных многоустойчивых элементах, содержащие генератор тактовых импульсов, опорнух ячейку, входное устройство прямого счета и схемы совпадения и объединения.

Предложенный счетчик отличается от известных тем, что он содержит входное устройство обратного счета, выход которого соединен с дополнительным входом схемы объединения и одним из входов схемы совпадения первого разряда. Второй вход упомянутой схемы совпадения и вторые входы соответствующих схем совпадения остальных разрядов подключены к выходам тех же разрядов, а выходы этих схем совпадения через расширители импульсов соединены с одним из входов схемы совпадений каждого следующего разряда.

Это позволило упростить схему счетчика и обеспечить реверс и индикацию счета.

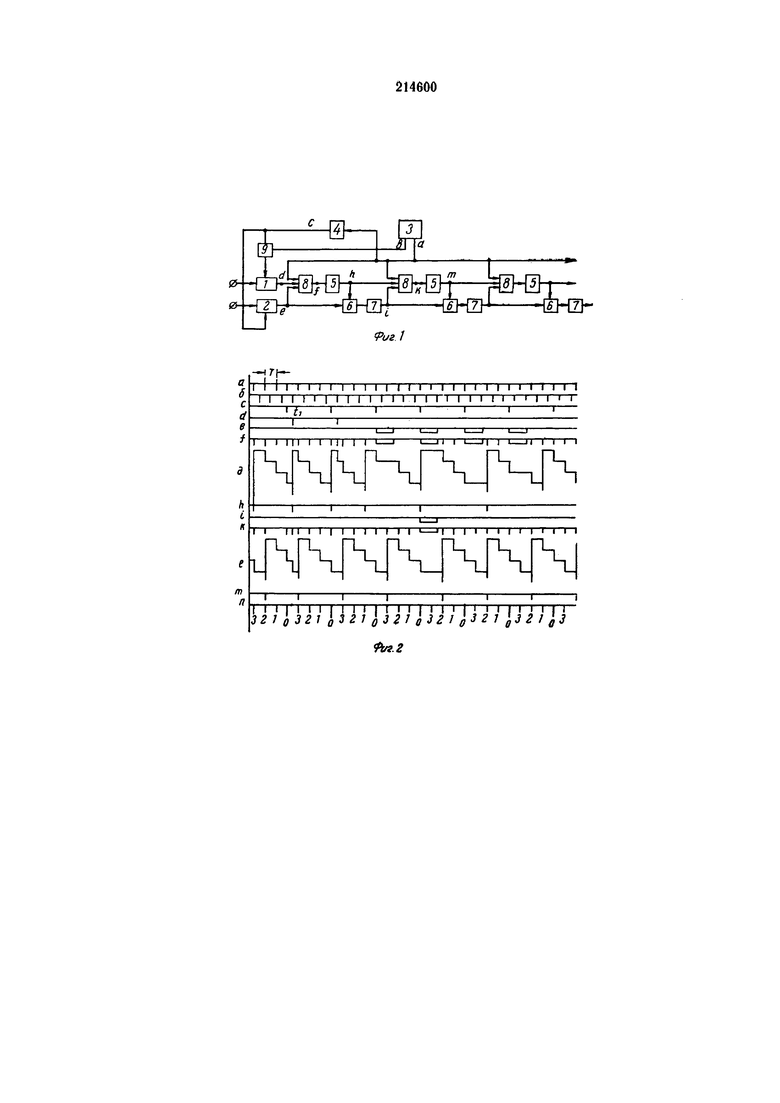

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - временные диаграммы напряжений в точках, обозначенных на фиг. 1 соответствующими буквами латинского алфавита. На фиг. 2, n приведена шкала состояний.

Схема счетчика состоит из входных устройств прямого счета 1 и обратного счета 2, двухтактного генератора 3 тактовых импульсов, опорной ячейки 4, представляющей собой фазоимпульсный элемент, соответствующего числа разрядов, каждый из которых содержит фазо-импульсный многоустойчивый элемент 5, схему совпадения 6, расширитель импульсов 7, трехвходовую схему «ИЛИ» 8 и схему задержки 9. Временные диаграммы, приведенные на фиг. 2, иллюстрируют работу четверичного счетчика, т.е. коэффициенты давления любого фазоимпульсного элемента памяти и опорной ячейки равны четырем.

Тактовые импульсы с одного из выходов генератора 3 поступают на опорную ячейку 4 и на первые входы схем «ИЛИ» 8 всех разрядов счетчика. Импульсы прямого счета, появляющиеся в произвольные моменты времени, поступают на вход устройства 1, которое обеспечивает привязку этих импульсов к ближайшим во времени импульсам опорной последовательности, предварительно задержанным с помощью схемы 9. Время задержки выбирают так, чтобы импульсы с выхода устройства прямого счета 1, поступающие на второй вход схемы «ИЛИ» 8 первого разряда, не совпадали ни с одним из импульсов такта. Очевидно, что разрешающее время такого счетчика не превышает периода следования импульсов опорной последовательности.

Появление каждого импульса на выходе схемы «ИЛИ» 8 вызывает в случае использования фазоимпульсного элемента на емкостном накопителе изменение напряжения на накопительной емкости. После прихода каждых четырех импульсов напряжение на конденсаторе достигает порога срабатывания схем сброса (на чертеже не показаны). В результате срабатывания схемы сброса конденсатор разряжается до первоначального значения и импульс передается на следующий разряд счетчика.

При отсутствии счетных импульсов схема сброса любого разряда срабатывает под воздействием одного из тактовых импульсов. При этом действие импульса сброса на вход схемы «ИЛИ» 8 совпадает во времени с тактовым импульсом, поступающим на другой вход «ИЛИ» 8. Так как одновременный приход импульсов на различные входы схемы объединения вызывает появление на ее выходе только одного импульса, то каждый последующий разряд срабатывает только после прихода четырех тактовых импульсов. Следовательно, состояния всех разрядов счетчика при отсутствии импульсов счета должны сохраняться неизменными.

Приход каждого импульса прямого счета изменяет состояние первого разряда, а момент перехода разряда из конечного состояния в нулевое не совпадает ни с одним из тактовых импульсов, что обусловливает изменение на единицу состояния последующего старшего разряда.

Импульсы обратного счета поступают на вход устройства 2, обеспечивающего привязку этих импульсов к ближайшим во времени импульсам опорной последовательности и их расширение до величины τ, причем Т<τ<2Т. Привязанные и расширенные импульсы поступают на третий вход схемы «ИЛИ» 8 первого разряда и на один из входов схемы совпадения 6, второй вход которой подсоединен к выходу первого разряда. Выход схемы совпадения через расширитель 7 подключен к третьему входу схемы «ИЛИ» 8 и одному из входов схемы совпадения 6 второго разряда счетчика.

Таким образом, каждый импульс обратного счета вызывает в момент действия ближайшего опорного импульса появление на третьем входе схемы «ИЛИ» 8 расширенного импульса. В результате следующий (во времени) за опорным тактовый импульс, приходящий на первый вход схемы «ИЛИ» 8 совпадает с расширенным импульсом и не воздействует на заряд накопительного конденсатора первого разряда счетчика, задерживая тем самым момент срабатывания этого разряда на время Т. В момент перехода разряда из нулевого состояния в конечное на вход последующего разряда поступает импульс займа.

Приход второго импульса обратного счета совпадает с моментом срабатывания первого разряда, в результате чего на выходе схемы совпадения 6 первого разряда и, следовательно, на выходе расширителя 7 возникает сигнал займа, переводящий второй разряд из третьего состояния во второе. При этом первый разряд счетчика переходит в конечное - третье - состояние.

В качестве схемы расширителя 7 можно использовать одновибратор, ждущий блокинг-генератор, двухвходовый триггер и др.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU275136A1 |

| Счетчик импульсов | 1978 |

|

SU750745A1 |

| Счетчик импульсов | 1972 |

|

SU456369A1 |

| Реверсивный счетчик импульсов | 1972 |

|

SU437231A1 |

| Счетчик импульсов | 1977 |

|

SU830650A1 |

| Счетчик импульсов | 1978 |

|

SU746949A1 |

| СЧЕТЧИК ИМПУЛЬСОВ по МОДУЛЮ п | 1965 |

|

SU170205A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU275132A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1972 |

|

SU430512A1 |

| ОДНОРАЗРЯДНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК | 1971 |

|

SU300958A1 |

Счетчик импульсов на фазоимпульсных многоустойчивых элементах, содержащий генератор тактовых импульсов, опорную ячейку, входное устройство прямого счета, схемы совпадения и объединения, отличающийся тем, что, с целью упрощения схемы счетчика три обеспечении реверса и индикации счета, он содержит входное устройство обратного счета, выход которого соединен с дополнительным входом схемы объединения и одним из входов схемы совпадения первого разряда, причем второй вход упомянутой схемы совпадения и вторые входы соответствующих схем совпадения остальных разрядов подключены к выходам тех же разрядов, а выходы этих схем совпадения через расширители импульсов соединены с одним из входов схемы совпадения каждого следующего разряда.

Авторы

Даты

1968-06-17—Публикация

1966-04-14—Подача