1

Изобретение относится к радиоэлектронике, автоматике и вычислительной технике.

В известном устройсТ|Ве, содержащем источник онорной последовательности, триггер знака, блок синхронизации, преобразователь разности фаз, счетчик-преобразователь и коммутатор разрядов, необходимо иметь генератор фазовых констант реверсивным, что усложняет схему и снижает ее надежность. Кроме того, известное устройство характеризуется сложностью работы с внешними устройствами и необходимостью иметь дополнительные преобразователи кодов для работы с внешними устройствами, а также питание цифровых индикаторов короткими импульсами 8- 10 мксек неблагоприятно сказывается на согласовании информационных сигналов с цифровыми индикаторами и на долговечности индикаторов.

Предлагаемое устройство, с целью его упрощения и расширения функциональных возможностей, содержит схему анализа кодов, схему запрета, вентили анализа дополнительного кода и схему совпадений, причем входы схемы анализа кодов соединены с выходами триггера знака,, коммутатора разрядов и источника опорной последовательности, а выходы схемы анализа кодов соединены с блоком синхронизации и преобразователем разности фаз, выход схемы запрета

соединен со входом установки «минус единица счетчика-преобразователя, а входы этой схемы соединены с коммутатором разрядов и выходом схемы совпадения, входы которой соединены с выходом блока синхронизации и с выходом триггера знака, первые входы вентилей анализа дополнительного кода соединены с информационными выходами соответствующих разрядов реверсивного счетчика импульсов, выходы вентилей соединены с коммутатором разрядов и со вторыми входами вентилей анализа дополнительного кода каждого следующего разряда, второй вход вентиля анализа дополнительного кода

младшего разряда соединен с выходом источника опорной последовательности.

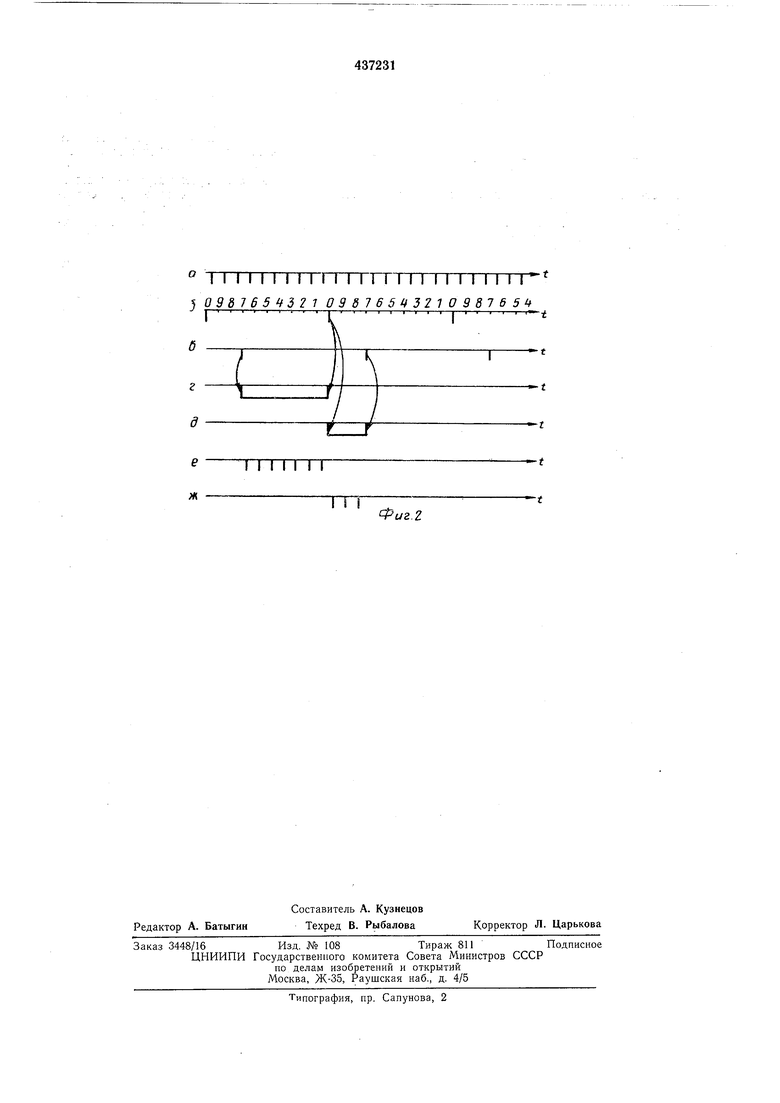

Па фиг. I представлена блок-схема предлагаемого устройства; на фиг. 2 - преобразование фазоимпульсного кода в прямой и дополнительный.

Приняты следующие обозначения: известная часть 1 реверсивного счетчика; входное устройство 2 прямого счета; входное устройство 3 обратного счета; двухтактный генератор 4 тактовых импульсов; источник 5 опорной последовательности; схема 6 задержки; фазоимпульсный многоустойчивый элемент 7; схема 8 совпадений; расшир:итель 9 и.мпульсов; схема «ИЛИ 10; схемы 11, 12 совпадеНИИ; триггер 13 знака; известная часть 14

устройства вывода; коммутатор 15 разрядов; блок 16 управления; счетчик-преобразователь 17; преобразователь 18 разности фаз в число импульсный код; блок 19 синхронизации; схема 20 задержки; устройство 21 индикации; схема 22 анализа кодов; схемы 23- 24 совпадений; вентиль 25 анализа дополнительного кода; схемы 26, 27 совпадений; схема 28 запрета.

Известная часть 1 счетчика состоит из входных устройств прямого 2 и обратного счета 3, двухтактного генератора 4 тактовых импульсов, источника 5 опорной последовательности, элементов 6 задержки и соответствующего числа разрядов, каждый из которых содержит фазоимпульсный многоустойчивый элемент 7, схему 8 совпадения, расширитель 9 импульсов и трехвходовую схему «ИЛИ 10 объединения; кроме того, счетчик содержит схемы 11 и 12 совпадения и триггер 13 знака.

Известная часть 14 устройства вывода состоит из коммутатора 15 разрядов, блока 16 управления, счетчика 17 преобразователя, преобразователя 18 разности фаз в число импульсный код, блока 19 синхронизации, схемы 20 задержки и устройства 21 индикации. Кроме того, счетчик содержит схему 22 анализа кодов со схемами 23 и 24 совпадения, вентиль 25 анализа дополнительного кода со схемами 26 и 27 совпадения и схемой 28 запрета.

Устройство работает следующим образом.

Иосле поступления импульса «Начало индикации (или регистрации) на вход блока 16 управления, на его управляющем выходе появляются импульсы. Первый импульс установит блок 19 синхронизации в исходное состояние и переключит коммутатор 15 разрядов. При -положительном числе импульс с информационного выхода коммутатора 15 разрядов через открытую схему 23 совпадения переключит блок 19 синхронизации, который выдаст одиночный импульс на преобразователь 18 разности фаз в число импульсный код и на вход закрытой схемы 27 совпадения. На второй вход схемы преобразователя 18 разности фаз поступает импульс опорной последовательности через вторую открытую схему 23 совпадения.

Таким образом формируется временной интервал, пропорциональный разности фаз в прямом коде, который заполняется импульсами вспомогательной тактовой последовательности. При отрицательном числе первый импульс опорной последовательности через открытую схему 24 совпадения переключит блок 19 синхронизации, который выдаст одиночный импульс на преобразователь 18 разности фаз в числоимпульсный код и на вход открытой схемы 27 совпадения. На второй вход схемы преобразователя 18 разности фаз поступает импульс с информационного выхода коммутатора 15 разрядов через вторую открытую схему 24 совпадения.

Таким образом формируется временной интервал, пропорциональный разности фаз в дополнительном коде, который заполняется импульсами вспомогательной тактовой последовательности.

На фиг. 2 поясняется преобразование фазоимпульсного кода в прямой и дополнительный (до «10) коды (цифра «7). Приняты следующие обозначения: импульсы а вспомогательной тактовой последовательности; опорная последовательность б; информационный сигнал е; временной интервал г, пропорциональный прямому коду; временной интервал д, пропорциональный дополнительному коду; информационный сигнал е в прямом числоимпульсном коде; информационный сигнал ж в дополнительном числоимпульсном коде. При индикации истинных значений отрицательных чисел информация младшего разряда всегда преобразуется в дополнительный код до «10. Преобразование информации последующих разрядов в дополнительный код до «10 осуществляется только в том случае, когда все предыдущие разряды находятся в нулевом состоянии. Если же хотя бы один из предыдущих разрядов находится не в нулевом состоянии, то преобразование осуществляется в дополнительном коде до «9.

Это достигается тем, что счетчик-преобразователь 17 предварительно устанавливается в состояние «О при дополнении до «10 и в состояние «-1 (для двоичного счетчика на четырех триггерах - в состояние «14) -

при дополнении до «9 с помощью вентиля 25 анализа дополнительного кода. Вентиль 25 работает следующим образом. На входы всех схем 26 совпадения поступают информационные сигналы соответствующих им разрядов. На вход схемы 26 совпадения младщего разряда поступают сигналы опорной последовательности. Выход схемы 26 совпадения младшего разряда соединен со входом схемы 26 совпадения следующего разряда и входом коммутатора разрядов 15. Выходы остальных схем 26 совпадения соединены аналогичным образом.

Коммутатор 15 разрядов каждым импульсом опроса одновременно коммутирует информационный выход очередного разряда элемента 7 и выход схемы 26 совпадения предыдущего разряда.

Если предыдущие разряды фазоимпульсного мпогоустойчивого элемента 7 находятся в

нулевом состоянии, то со второго выхода коммутатора 15 разрядов сигнал синфазный с нулевой опорной последовательностью запрещает в схеме 28 запрета одиночный импульс, поступающий с блока 19 синхронизации через открытую схему 27 совпадения. Если хотя бы один из предыдущих разрядов элемента 7 находится не в нулевом состоянии, то на втором выходе коммутатора 15 разрядов сигналы отсутствуют, и одиночный импульс с

блока 19 синхронизации через открытые схемы 27 совпадения и запрета 28 установит счетчик-преобразователь 17 в состояние «минус единица.

Предмет изобретения

Реверсивный счетчик импульсов на фазоимпульсных многоустойчивых элементах, содержащий источник опорной последовательности, триггер знака, блок синхронизации, преобразователь разности фаз, счетчик-преобразователь и коммутатор разрядов, отличающийся тем, что, с целью упрощения устройства и расщирения функциональных возможностей, он содержит схему анализа кодов, схему запрета, вентили анализа дополнительного кода и схему совпадений, причем входы схемы анализа кодов соединены с выходами триггера знака, коммутатора разрядов и источника опорной последовательности, а выходы схемы анализа кодов соединены с блоком синхронизации и преобразователем разности фаз, .выход схемы запрета соединен со входом установки «минус единица счетчика-лреобразователя, а входы этой схемы соединены с коммутатором разрядов и выходом схемы совпадения, входы которой соединены с выходом блока синхронизации и с выходом триггера знака, первые входы вентилей анализа дополнительного кода соединены с информационными выходами соответствующих разрядов реверсивного счетчика импульсов, выходы вентилей соединены с коммутатором разрядов и со вторыми входами вентилей анализа дополнительного кода каждого следующего разряда, второй вход вентиля анализа дополнительного кода младщего разряда соединен с выходом источника опорной последовательности.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ДИСКРЕТНОГО КОНТРОЛЯ РАССТОЯНИЙ ДО ИСТОЧНИКА КОЛЕБАНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2028579C1 |

| Цифровой фазометр | 1980 |

|

SU875304A1 |

| Инфранизкочастотный фазометр | 1990 |

|

SU1775683A1 |

| Фазоимпульсный преобразователь | 1983 |

|

SU1161977A1 |

| Устройство фазоимпульсной модуляции | 1985 |

|

SU1411958A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1681316A1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Устройство для измерения параметров динамического процесса и управления с самоконтролем | 1986 |

|

SU1495751A1 |

I I I I I I I I I ГТТТГТ I I I I I I I I I I I

5 0 9 8 7 6 S 3 2 1 0 9 S 7 6 54321098765

- Г 7 I I I J L. .ly .. ..-.-... I. .. I. . .. .. ... - 1 I i IT

Фиг.г

Авторы

Даты

1974-07-25—Публикация

1972-03-24—Подача