Известны логические элементы «И, содержащие магнито-транзисторные ячейки с тактовыми и управляющими обмотками. Нагрузочная способность этих элементов мала, и частота работы их ограничена параметрами транзисторов и резисторов.

Предложенный элемент отличается от известных тем, что в нем транзисторы входных ячеек переходами коллектор-эмиггер через разделительные диоды подключены параллельно управляющим обмоткам выходных ячеек.

Такое соединение позволило значительно повысить нагрузочную способность элемента, количество входов и довести рабочую частоту до предельной частоты переключения сердечника.

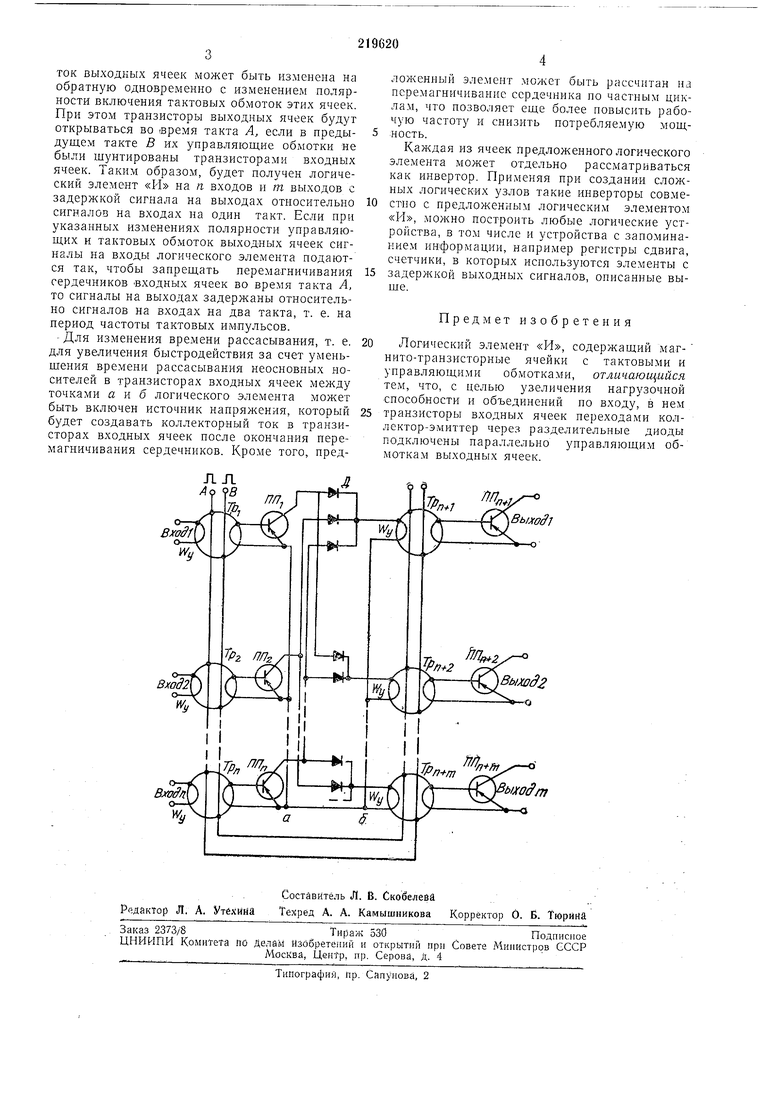

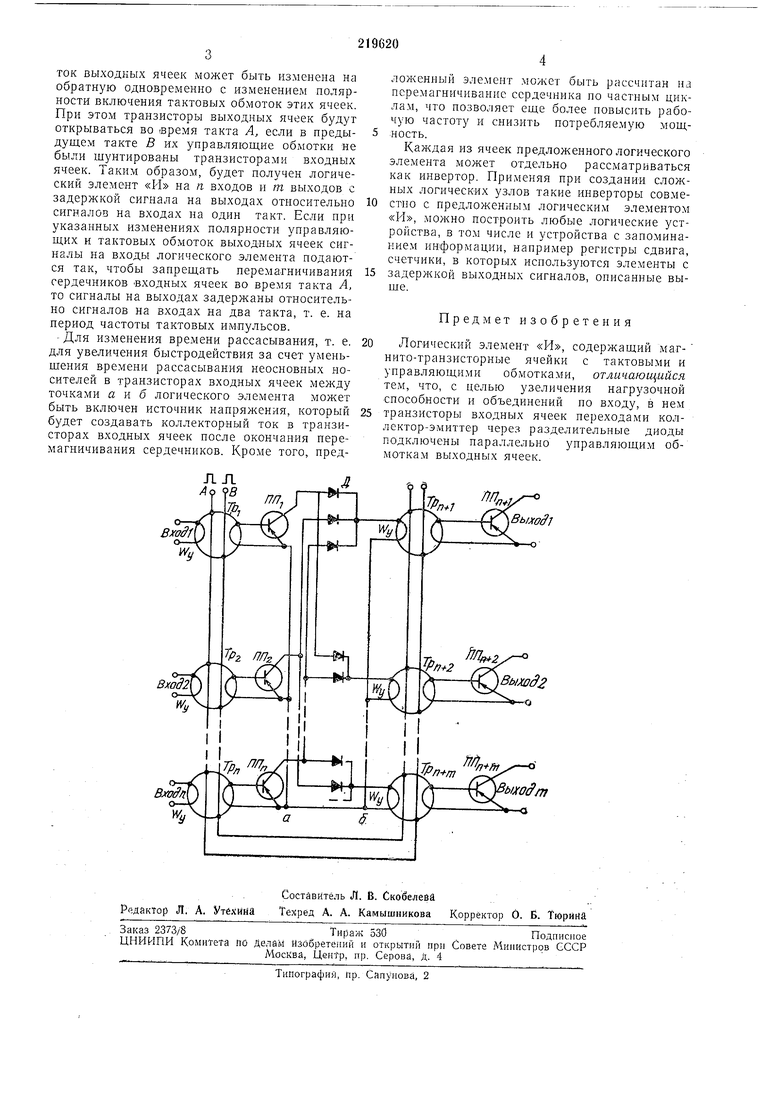

Схема логического элемента на п входов и т выходов показана на чертеже.

Схема состоит из п входных ячеек с трансформаторами Гр1-Гр„ и транзисторами /7/7i-ЯЯ„ и m выходных ячеек с трансформаторами Грн+1 -Трп+т и транзисторами ППп, Трансформаторы имеют управляющие Wy и таковые WT обмотки, намотанные на сердечники с прямоугольной петлей гистерезиса, перемагничивающиеся тактовыми импульсами А и В. Пусть сигнал на выходе / появляется в результате совпадения сигналов только на входах /, 2 и п, тогда только транзисторы ПП, ПП-у, ПП„ должны быть переходами коллектор-эмиттер подключены через разделительные диоды Д параллельно управляющей обмотке Wy трансформатора Трп-.

Если хотя бы на одном из указанных трех входов сигнала нет (например, на входе 1, то во время такта В транзистор этой входной ячейки (транзистор ПП) открывается и в это время переходом эмиттер-коллектор щунтирует управляющую обмотку трансформатора Трп+1 , запрещая перемагничивание его сердечника. Транзистор ППп,1 , включенный на выходе / логического элемента, во время такта В не открывается, т. е. сигнала на выходе /

нет.

Если на входах 1, 2 и п есть сигналы, которые запрещают перемагничивание сердечников трансформаторов Tpi, Тр и Тр во время такта В, например, щунтированием их управляющих обмоток, аналогично тому, как тран зисторы входных ячеек логического элемента щунтируют управляющие обмотки выходных ячеек, то транзисторы ЯЯ, ЯЯа и ЯЯ„ не открываются во время такта В, сердечник трансформатора Tpn.i не перемагничивается. Транзистор ППп,1 откроется во время такта В, выдавая выходной сигнал на выход 1.

На остальных выходах сигналы образуются аналогично. ток выходных ячеек может быть изменена на обратную одновременно с изменением полярности включения тактовых обмоток этих ячеек. При этом транзисторы выходных ячеек будут открываться во время такта А, если в нредыдущем такте В их управляющие обмотки не были шунтированы транзисторами входных ячеек. Таким образом, будет получен логический элемент «И на л входов и т выходов с задержкой сигнала на выходах относительно сигналов на входах на один такт. Если при указанных изменениях полярности управляющих и тактовых обмоток выходных ячеек сигналы на входы логического элемента подаются так, чтобы запрещать перемагничивания сердечников входных ячеек во время такта А, то сигналы на выходах задержаны относительно сигналов на входах на два такта, т. е. на период частоты тактовых импульсов. Для изменения времени рассасывания, т. е. для увеличения быстродействия за счет уменьшения времени рассасывания неосновных носителей в транзисторах входных ячеек между точками а и б логического элемента может быть включен источник напряжения, который будет создавать коллекторный ток в транзисторах входных ячеек после окончания неремагничивания сердечников. Кроме того, предложенный элемент может быть рассчитан на перемагничивание сердечника по частным циклам, что позволяет еще более повысить рабочую частоту и снизить потребляемую мошность. Каждая из ячеек предложенного логического элемента может отдельно рассматриваться как инвертор. Применяя при создании сложных логических узлов такие инверторы еовместно с предложенным логическим элементом «И, можно построить любые логические устройства, в том числе и устройства с запоминанием информации, например регистры сдвига, счетчики, в которых используются элементы с задержкой выходных сигналов, описанные выше. Предмет изобретения Логический элемент «И, содержащий Магнито-транзисторные ячейки с тактовыми и управляющими об1мотками, отличающийся тем, что, с целью увеличения нагрузочной способности и объединений но входу, в нем транзисторы входных ячеек переходами коллектор-эмиттер через разделительные диоды подключены параллельно управляющим обмоткам выходных ячеек.

Выхо

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХТАКТНЫЙ РАСПРЕДЕЛИТЕЛЬ | 1971 |

|

SU312372A1 |

| Преобразователь напряжения с многозонной модуляцией | 1982 |

|

SU1086525A1 |

| УСТРОЙСТВО ДЛЯ ИМПУЛЬСНО-ФАЗОВОГО УПРАВЛЕНИЯ т-ФАЗНЫМ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1969 |

|

SU436429A1 |

| Импульсный стабилизатор постоянного напряжения | 1990 |

|

SU1800450A1 |

| ДВУХТАКТНЫЙ ЭЛЕМЕНТ СОВПАДЕНИЯ | 1970 |

|

SU281543A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 1994 |

|

RU2077110C1 |

| Стабилизатор постоянного напряжения | 1986 |

|

SU1422324A1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1997 |

|

RU2129331C1 |

| Стабилизированный однотактный преобразователь напряжения | 1990 |

|

SU1728947A2 |

| Импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1597868A1 |

Даты

1968-01-01—Публикация